M. Tech. (Computer Science) Dissertation Series

# STUDIES IN SHORT CIRCUIT FAULT DIAGNOSIS OF MULTISTAGE INTERCONNECTION NETWORKS.

a disssertation submitted in partial fulfilment of the requirements for the M. Tech. (Computer Science) degree of the Indian Statistical Institute

By

MILIND B. KAMBLE

under the supervision of

Prof. B. P. SINHA

#### ACKNOWLEDGEMENT

I am deeply indebted to my supervisor Prof. B. P. Sinha for his helpful guidance and constant support during the course of this study. I am also grateful to Dr.B.B.Bhattacharya for his advice on numerous occasions. It has been an enlighteneing experience to study and work under some of the most enthusiastic educators and outstanding researchers at I.S.I.

I would like to mention special thanks to Krishnendu Mukhopadhyaya for the countless discussions and suggestions that have helped to make progress in this work. His help has been a major contribution in all aspects of this work.

I thank my friends Arani, Ashutosh, Hemanta, Jaydeep, Jyotishman, Koushik, Rahal, Rajan and Suresh for their support and encouragement.

#### AUSTRACT

The problem of diagnosing a single short circuit fault jointly with single switching element fault in baseline network has been studied in this work. The fault model has been described and upper bound result on the number of test vectors neccessary to detect short circuit fault in baseline network is obtained. The test vectors for detecting the fault are also determined. The diagnostic procedures for the cases of two-links short circuit case and three link short circuit case considered jointly with single switching element fault are developed. The difficulties in diagnosing the short circuit fault for higher number of links are finally discussed.

# CONTENTS

| Abstract                                             |       |

|------------------------------------------------------|-------|

| Acknowledgements                                     |       |

| 1. INTRODUCTION                                      |       |

| 1.1 Introduction to Multistage Interconnection Netwo | rks   |

| 1.2 Properties and classification of MINs.           |       |

| 1.3 Scope of the work.                               | • • • |

| 1.4 Organization                                     | - • • |

| 2. REVIEW OF FAULT DIAGNOSIS OF MINS                 |       |

| 2.1 Literature Survey.                               | ļ     |

| 2.2 Single Fault Diagnosis of a Baseline network     |       |

| 2.2.1 Fault Model and Test Set for Testing a SE.     | (     |

| 2.2.2 Test Vector Design and Algorithm for Singl     |       |

| Fault Diagnosis.                                     |       |

| 2.2.3 Casewise Diagnosis of Single Fault.            | 10    |

| 3. SHORT CIRCUIT FAULT DIAGNOSIS                     |       |

| 3.1 Problem definition and Motivation.               | 1 3   |

| 3.2 Fault Model, Upper Bound on the Number of Tests  |       |

| and Test Vector Generation.                          | 15    |

| 3.3 Diagnosis of Single Fault of Baseline Network.   |       |

| 3.4 Short Circuit Fault among Two Links.             |       |

| 3.4.1 Diagnosis of Nonseperated                      |       |

| Two-response Fault.                                  | 19    |

| 3.4.2 Diagnosis of Four-response Fault.              | 22    |

| 3.5 Short Circuit Fault among Three Links.           | ,     |

| 3.5.1 Diagnosis of Nonseperated                      |       |

| Three-response lault.                                | 23    |

| 3.5.2 Diagnosis of Fire-response Fault.              | 25    |

| 3.5.3 Diagnosis of Four-response Fault.              | 26    |

| 3.5.4 Diagnosis of Sir-response Fault.               | 27    |

| 3.6 Short Circuit Fault of Benes Network.            | 28    |

|                                                      | 40    |

...30

4. REFERENCES

3.7 Conclusions.

### 1.1 Introduction to Multistage Interconnection Networks

To improve computational power and computing speed, the concept of Parallel Processing has become quite popular. Alded by advances in VLSI technology, multiple processor systems are configured to provide computational parallelism. Each processor is called a Processing Element (PE), which can complex as a fully functional contemporary be as microprocessor or as simple as a basic ALU block. A multiprocessor system generally consists of more than one memory modules (MM) to make processor and memory bandwidths compatible. Unlike a simple PE-MM interconnection bus in uniprocessor systems, multiprocessor systems usually have complex PE-MM data paths.

Multiprocessor systems may be designed either in unchared memory configuration or chared memory configuration. In the former, each PE has its individual MM connected as a uniprocessor system bus and exchange of data/information among PEs takes place via communication links interconnecting the PEs. In the later, any PE can acess any MM and exchange of data/information is done via predetermined memory locations. Unshared memory configuration is suitable for computations that are highly individualistic and require little data flow amongst the PEs, for example matrix transpose and multiplication operations, while the shared memory configuration is suitable for computations that are highly dependent, requiring heavy interprocessor dataflow, for example FFT computations.

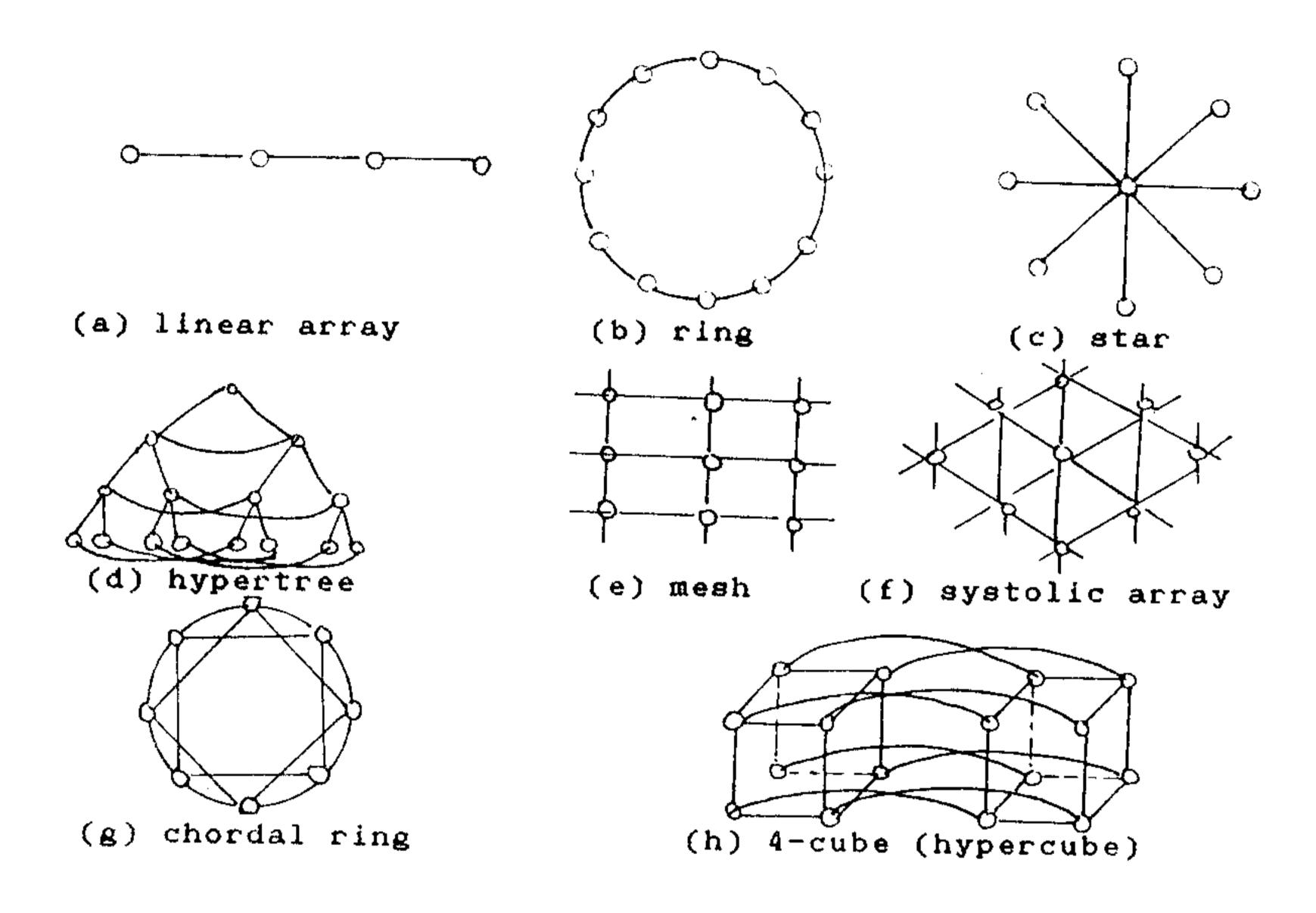

Unshared memory systems are usually configured using static (dedicated) communication links among the PEs so that the interconnection network has a distinct topology. Linear array, ring, mesh, star, systolic array, hypertree, hypercube, barrell shifter, cube-conected cycles are some of the popular static interconnection topologies, some of which

are shown in Fig. 1.

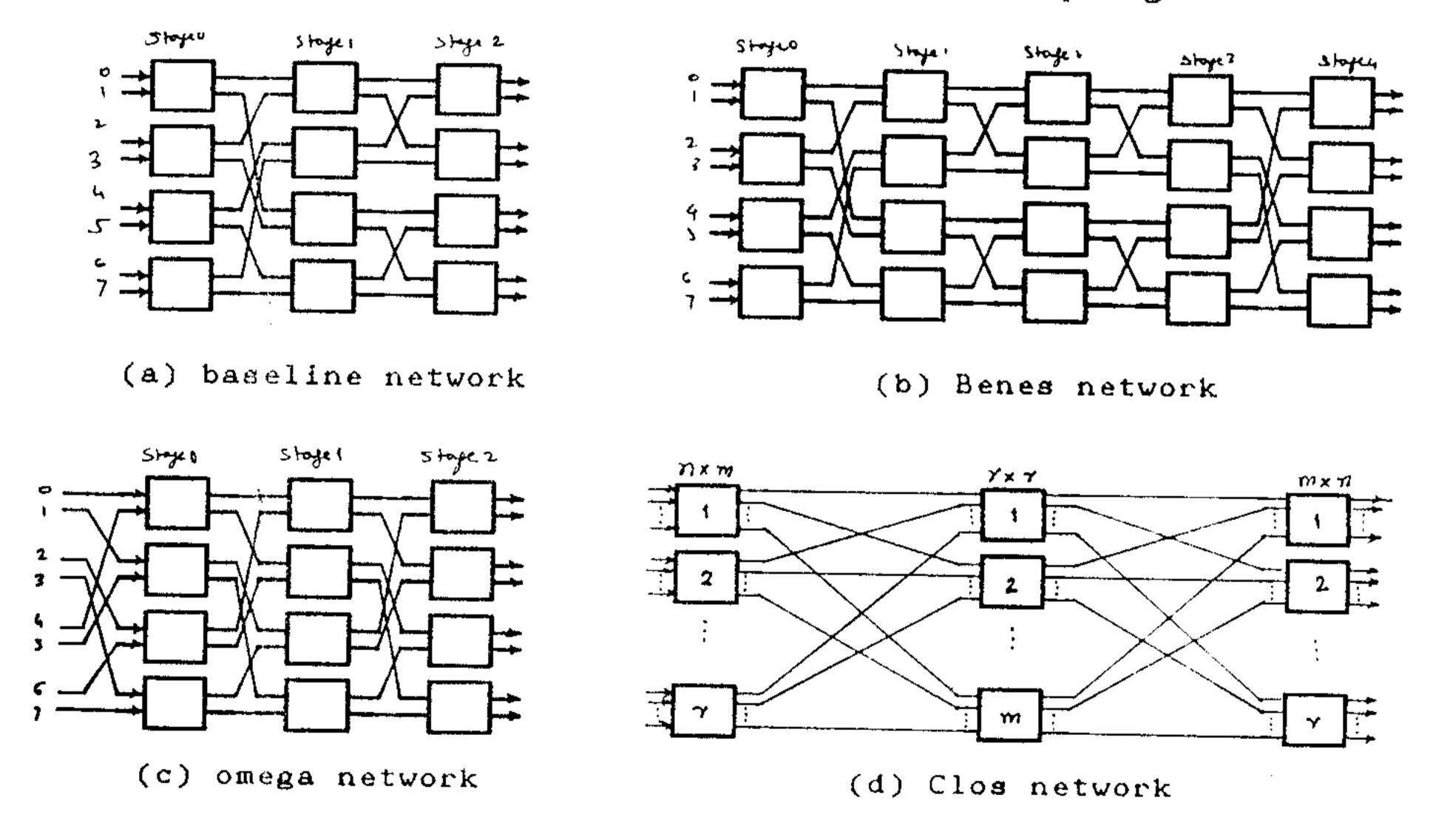

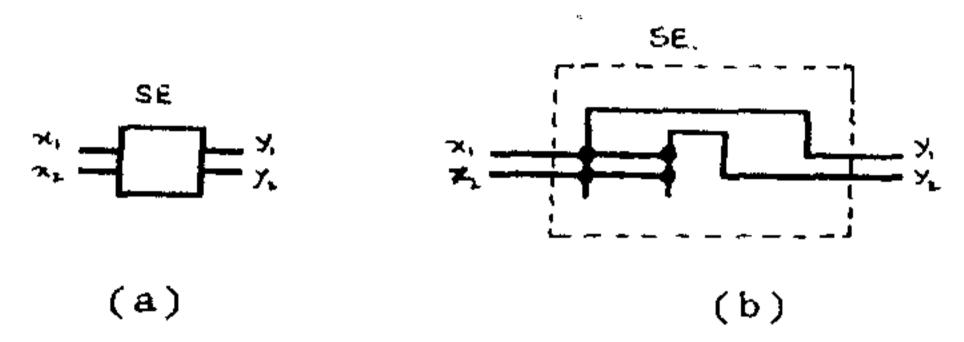

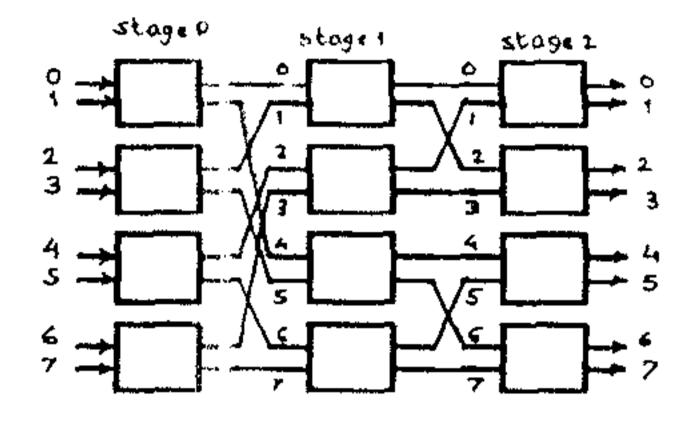

Since shared memory systems require that any PE be able to acess any MM, the PE-MM data paths need to be dynamic and memory contention should also be prevented. This is achieved by a Multistage Interconnection Network (MIN) which has programmable datapaths so that a path can be dynamically established between a pair of input-output lines. The dynamism of datapaths is achieved by using programmable solid state switching elements (SE) grouped together in one or more stages. The SEs of consecutive stages are interconnected by communication links, the topology of which give rise to MIN configurations such as lienes, baseline, butterfly, omega, flip, data manipulator and indirect hypercube networks, some of which are shown in Fig. 2.

# 1.2 Properties and Classification of MINs

The number of stages interstage connection topolgy and switching capability of the SEs characterize a MIN. A switching element can, in general, have m input lines and n output lines, so that it is not incorrect to identify a SE as a interconnection network itself. The simplest SE is a 2x2 switch having four possible input-output routings as shown in Fig.3. Most MINs use 2x3 switching elements and restrict their valid states to straight (S-mode) and cross (X-mode) only.

The MIN can be thought of as a permutation function, which permutes the input lines to a given order at the output. In this respect, it is important to note that not all MINs are capable of providing all possible (=N!, where N is the number of input/output lines) permutations. On this basis the MINs can be classified as follows:

(i) Blocking or Nonrearrangeable type: These MINs cannot provide all permutations. This happens because, there is generally a unique path between a given input-output pair in the network and it blocks certain other input-output paths from being established. This class includes the baseline, omega, reverse baseline, flip and indirect hypercube

Fig.1. Static interconnection network topologies.

Fig. 2 Multistage interconnection networks

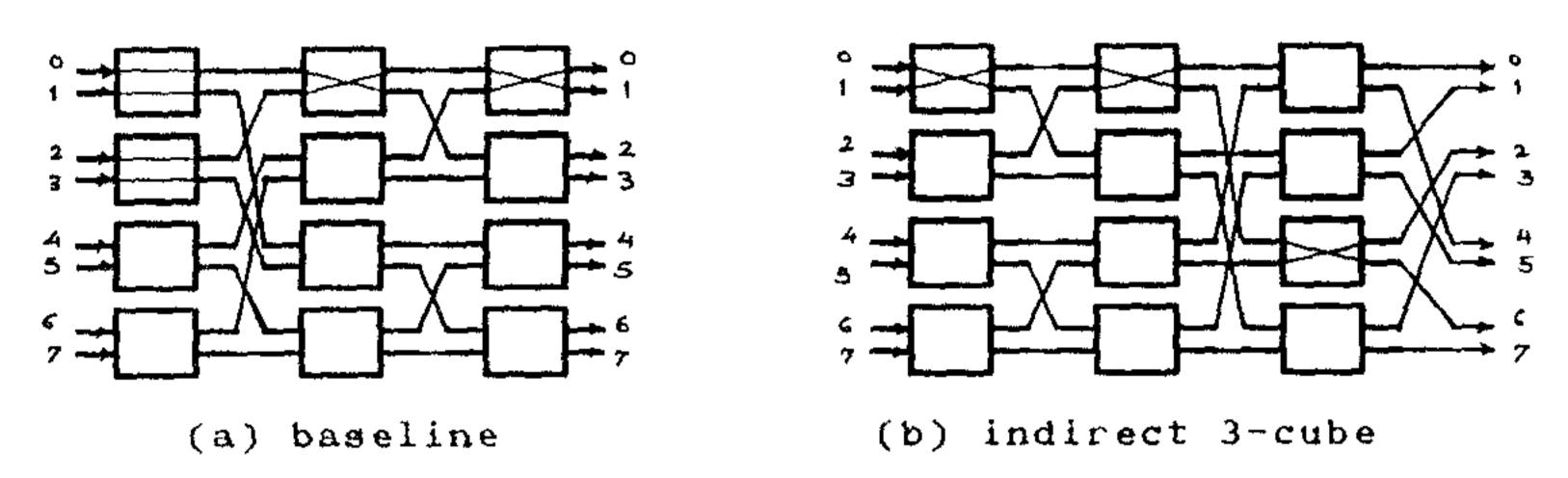

networks. Fig.4. shows instances of blocking in baseline and indirect hypercube network.

# (ii) Loosely nonblocking or Rearrangeable type :

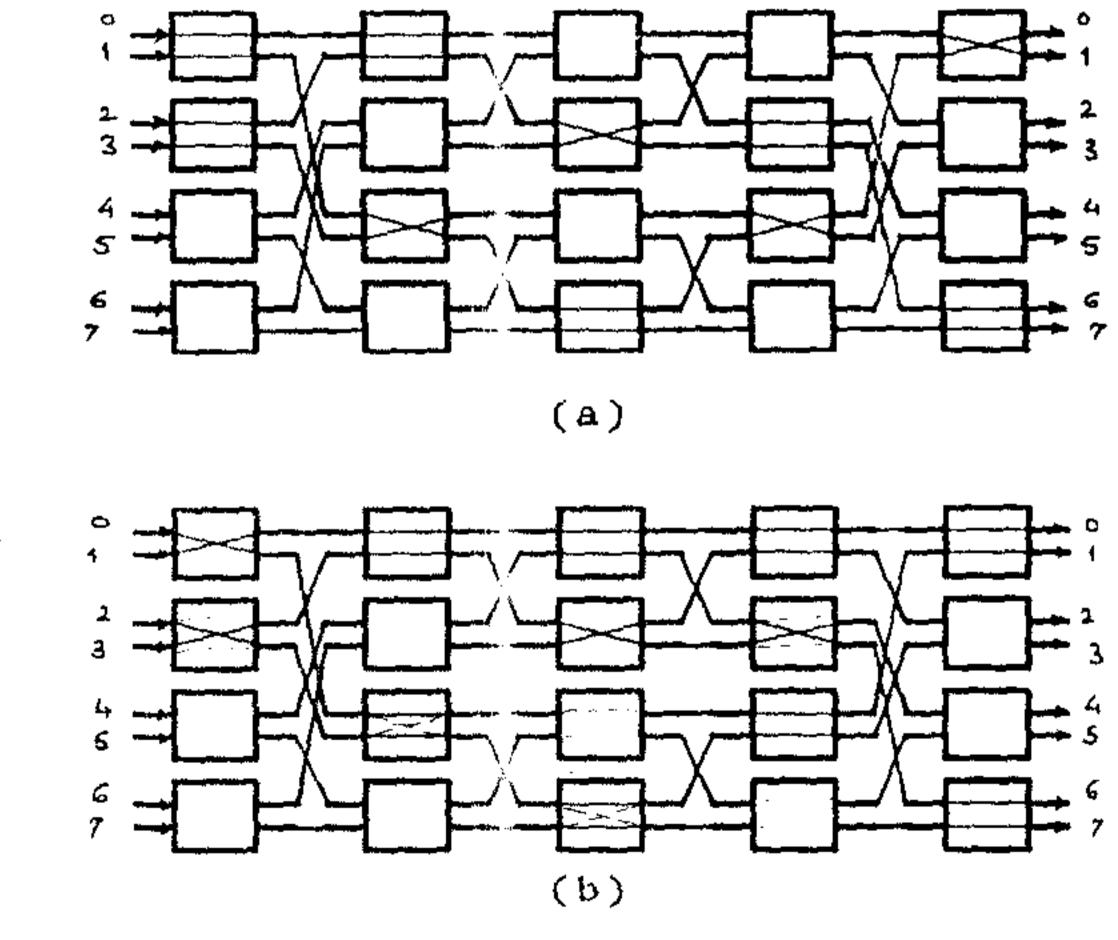

These MINs can provide all permutations of the input lines. However it may be necessary to establish an alternate path for an existing one, so as to accommodate the path for some other pair. This is called rearranging the network to achieve the required permutation. This class includes the Benes, (3log<sub>2</sub>N-4) stage omega network, (2log<sub>2</sub>N-1) stage omega<sup>2</sup>-omega<sup>4</sup> networks. Fig.5 shows instances of rearranging in a 8x8 Benes network.

# (iii) Strictly nonblocking type:

These MINs have multiple paths for any input-output pair and it is always possible to establish a path independent of existing paths. The Clos network is an example of this class.

#### 1.3 Scope of the Work

The area of fault diagnosis of MINs is assuming more and more importance because with the use of parallel systems expanding rapidly, system reliability measures are becoming prominent parameters for system performance.

The problem of diagnosing a single short circuit fault jointly with single SE fault in baseline network has been studied in this work. The fault model has been described and upper bound result on the number of test vectors neccessary to detect short circuit fault in baseline network is obtained. The test vectors for detecting the fault are also determined. The diagnostic procedures for the cases of two-links short circuit case and three link short circuit case considered jointly with single SE fault are developed. The difficulties in diagnosing the short circuit fault for higher number of links are discussed.

#### 1.4 Organization of the report

The current state of work in the fault diagnosis related to MINs is reviwed in chapter 2. The study of single SE fault diagnosis is summarised in more detail in section 2.2 because

Fig.3 A 2x2 switching element. (a)straight connection (S-mode). (b)cross connection (X-mode). (c)lower broadcast (LB-mode). (d)Upper broadcast (UB-mode).

Fig. 4 Blocking networks

- (a) The path 2-1 blocks paths 3-0, 0-1, 7-1 etc.

- (b) The path 1-6 blocks paths 0-4, 0-6, 0-2 etc.

Fig. 5 Rearranguable network (Benes)

- (a) Paths 2-6 and 1-0 block the path 3-1.

- (b) Paths 2-6, 1-0, 3-1 are established after rearrangement.

we wish to develop fault diagnosis procedures for short circuit faults jointly with the single SE fault.

Chapter 3 discusses the bulk of work done. In this, the fault model is first defined in terms of the output response behaviour of these faults. The upper bound results for fault detection are determined in section 3.2. In section 3.4. we discuss the fault diagnosis of two-link short circuit fault. The three-link short circuit fault is discussed in section 3.5. In section 3.6 the short circuit fault diagnosis of Benes network is proposed.

## 2.1 Literature Survey

Study of fault diagnosis of MINs was initiated in the early 70's by Opferman et. al.in [OT71] in which, they gave a diagnostic procedure for Benes network considering a restricted fault model with only two faulty states of the SEs. They developed a test set generation procedure using a looping algorithm.

[A82] is a survey of the fault diagnosis works related to blocking networks, rearrangeable networks and fault tolerant design of MINs.

Feng et. al. give a very comprehensive fault diagnosis procedure for single fault of a baseline network in [FW81]. They describe a general fault model of the SE and the diagnosis is done by observations on the output side only. Testing consists of two phases in which all the SEs are set in S-mode and X-mode and there are two tests in each phase. A fault can be detected in four tests independent of network size. Single fault diagnosis requires at most max(12,6+2[log<sub>2</sub>(log<sub>2</sub>N)]) tests for an NxN baseline network. Certain SE faults cannot be accurately located and such faults are also indistinguishable from link stuck-type fault. This is because these faults exhibit exactly same output response for any test input and any setting of the baseline network.

[FY86] design test procedures for fault diagnosis of rearrangeable networks. Unlike [OT71], instead of a Benes network, they use a (2log N-1) stage omega -omega network which is equivalent to a Benes network as shown in [L81].

[FZ91] gives fault diagnosis procedure for blocking MINs having four valid states of the SEs. They have again used a baseline network for study, since most other blocking networks are equivalent to a baseline network as demonstrated in [WF80].

#### 2.2 Single Fault Diagnosis of a Baseline Network ([FW81])

As discussed in section 1.3, our aim is to provide diagnostic procedures for thort circuit faults, so as to make the test procedure of a baleline network complete. Since we shall be referring to the [FW81] work frequently in chapter 3, we feel it appropriate to discuss the relevant portions vis-a-vis short circuit faults here. This will also help to introduce the terminology to be used further on.

#### 2.2.1 Fault Model and Test Set for Testing a SE/link

A fault located at a link can be modelled by a link stuck-at-0 (s-a-0) or stuck-at-1 (s-a-1). A 2x2 SE can be modelled by a 2x2 crosspoint switching matrix as shown in Fig.6. An SE in this model can have 16 possible states, which covers all the possible input-output connections of a 2x2 switch. Hence this model is the most general model of a 2x2 SE. Table I shows the set  $S = \{S_0, \ldots, S_{15}\}$  of 16 states and the encoding of these states.

Definition 1: The states of an SE which are allowed in a MIN are called the valid states of the SE for that MIN. The remaining states of S form the set of faulty states.

Most of the MINs, for example baseline, flip, Benes and indirect hypercube, have  $S_5$  and  $S_{10}$  as the valid states. Some MINs, for example omega and regular SW banyan networks, also include  $S_9$  and  $S_{12}$  as valid states.

For an SE with n valid states, there are (16) different state configurations in which it can behave. The set of ordered n-tuples:  $\{(s_1,s_2,\ldots,s_n)\mid s_i \in S,\ 1 \leq i \leq n\}$  gives all the configurations of the SE. Among the (16) configurations only one is fault-free, the rest represent a fault of the SE. Thus the number of faulty configurations in this general fault model increases exponentially with the number of valid states. In a baseline network, therefore, we have one fault-free configuration and 255 faulty configurations. Except four faults, all are diagnosable by observing output responses of various tests. To design a test set for switching element and link stuck-type faults, the

Fig. 6.(a)switching element (SE). (b) 2x2 crosspoint switching matrix (CSM)

Table I

Set of 16 states of a 2x2 SE and their encoding

| state          | SE                                      | CSM<br>symbol | atate SE<br>symbol | CSM<br>symbol |

|----------------|-----------------------------------------|---------------|--------------------|---------------|

| S <sub>o</sub> |                                         |               | S <sub>B</sub>     |               |

| S <sub>4</sub> |                                         | <del>-</del>  | s <sub>e</sub>     | -             |

| S <sub>2</sub> | · — — — — — — — — — — — — — — — — — — — |               | S <sub>10</sub>    |               |

| S <sub>9</sub> |                                         | <del></del>   | Sii                |               |

| S.             |                                         | <del></del>   | S <sub>12</sub>    |               |

| S <sub>5</sub> |                                         |               | S <sub>19</sub>    |               |

| S <sub>o</sub> |                                         |               | S <sub>14</sub>    |               |

| S <sub>7</sub> |                                         |               | S <sub>15</sub>    | <del>-</del>  |

test bits which cause observable faulty outputs must be determined. Table II and table III indicate the necessary test inputs.

Definition 2: A logically unidentified value is denoted by — and a logically erroneous value by  $\Phi$ .

The binary logic value of a open circuited link is represented by -. The binary logic value of a short circuited link is represented by  $\Phi$ . Note that a shorted condition is observed only if the shorted pair of links receive complementary test bits, otherwise the fault is transparent.

The values — and & depend on the circuit implementation of the MIN, however an arbitrary but consistent assignment of 0 or 1 will not affect the fault diagnosis. In fact there is an algorithm to accurately distinguish between these types of faults.

From tables II and III it can be observed that only two test inputs  $(x_1, x_2) = (0, 1)$  and  $(x_1, x_2) = (1, 0)$  are needed to observe the SE/link faults. The test set should therefore ensure that the SEs and the links are tested with complementary test bits.

# 2.2.2 Test Vector Design and Algorithm for Single Fault Diagnosis.

Definition 3: Links are assigned addresses by identifying them with the stage, the input side of which they are connected to and numbering them from top to bottom. The stages of the MIN are numbered from left to right starting from 0, and if n is the number of stages in the MIN, the output side links are designated as links of stage n. A Link is called even if its binary address contains even number of 1's, odd otherwise.

Accordingly, in an NxN MIN with  $N=2^n$  and 1-stages, a link of the  $j^{th}$  stage will be identified as  $P_j=(p_{n-1}\dots p_1p_0)_j$ ,  $0\le j\le n$ . Fig. 7 shows the addressing scheme for a 16x16 baseline network. A path of the MIN will be given as a (n+1)-tuple  $P=(P_0,P_1,\dots,P_{n-1},P_n)$  of its links or by anyone of its links, say  $P_i$ , if the MIN setting is known.

TABLE II FAULTS, TEST INPUTS, AND OUTPUTS IN VALID STATE  $S_{10}$

| 170013, 1                   |                                              | 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 | <del></del>                 | 3D 31 X 11 3 10 |  |  |  |

|-----------------------------|----------------------------------------------|-----------------------------------------|-----------------------------|-----------------|--|--|--|

|                             | Fault                                        |                                         | Output                      |                 |  |  |  |

|                             |                                              |                                         | Normal                      | Frules          |  |  |  |

|                             |                                              |                                         | \$ \$2                      | , s, s,         |  |  |  |

|                             |                                              | ×1 ×2                                   | 1 2                         | 1               |  |  |  |

|                             | X; , ×;                                      | 1 0                                     | 1 0                         | 0 0             |  |  |  |

| <u> </u>                    |                                              | 1 1                                     | 1 1                         | 0               |  |  |  |

| 2.3                         | * * * * * * * * * * * * * * * * * * *        | 0 0                                     | 0 0                         | 1 0             |  |  |  |

| 🕰                           |                                              | 0 1                                     | 0 1                         | 1 - 1           |  |  |  |

| ⊷<br>삼                      | 1 ×2' ×2                                     | 0 1                                     | 0 1                         | 1 0             |  |  |  |

| Part I: Link<br>Stuck Fault | 1 21 21                                      | 0 0                                     | $\frac{1}{0}$ $\frac{1}{0}$ | 0 1             |  |  |  |

| 5 v                         | ×2. ×2                                       | 1 0                                     | ] i o                       | 1 1             |  |  |  |

|                             | <del> </del>                                 | 0 1                                     | 0 1                         | <del>}</del>    |  |  |  |

|                             | s <sub>10</sub> -s <sub>0</sub>              | 1 0                                     | 1 0                         | ]               |  |  |  |

|                             | 10 0                                         | 0 0                                     | 0 0                         | <u> </u>        |  |  |  |

|                             | J                                            | 1 1                                     | 1 1                         | <u> </u>        |  |  |  |

|                             |                                              | 0 1                                     | 0 1                         | 1 -             |  |  |  |

|                             | S <sub>10</sub> -S <sub>1</sub>              | 1 0                                     | 1 0                         | 0 -             |  |  |  |

|                             | :                                            | 0 0                                     | 0 0                         | 0 -             |  |  |  |

|                             | <u> </u>                                     | \ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \ | \ <del>1</del>              |                 |  |  |  |

|                             | <b>,</b> ,                                   | ] 0 1                                   | 0 1                         | - 0             |  |  |  |

|                             | \$10 <sup>-8</sup> 2                         | ôŏ                                      | 0 0                         | - 0             |  |  |  |

|                             | }                                            | 1 1                                     |                             | - 1             |  |  |  |

|                             | 5.2-5,                                       | 0 1                                     | <del>0</del> 1              | 1 1             |  |  |  |

| 77                          | 10 3 .                                       | 1 0                                     | 1 0                         | ОС              |  |  |  |

| Fault                       |                                              | 0 1                                     | 0 1                         | <del>-</del> 0  |  |  |  |

| ŭ,                          | \$10 <sup>-5</sup> 4                         | 1 0                                     | 10                          | - 1             |  |  |  |

| ř                           | 10 4                                         | 0 0                                     | 00                          | <b>-</b> 0      |  |  |  |

| 3lement                     |                                              | 1 1                                     | 1 1                         | <u> </u>        |  |  |  |

| . ដ                         | 510-5                                        | 0 1                                     |                             | 1 0             |  |  |  |

|                             |                                              | $\frac{1}{0}$                           | $\frac{1}{0}$               | 0 1             |  |  |  |

| 15.<br>+1                   | 5 -5                                         | 1 0                                     |                             | ~               |  |  |  |

| Ω<br><del>τ.</del>          | 210_26                                       | 0 0                                     |                             | - 0             |  |  |  |

| Switching                   | 1                                            | 1 1                                     | iii                         | - ì             |  |  |  |

| Ň                           | \$10-57                                      | 0 1                                     | 0 1                         | 1 4             |  |  |  |

|                             | 10 /                                         | 1 0                                     | 1 0                         | 0 0             |  |  |  |

| : 11                        |                                              | 0 1                                     | 0 1                         | 0 -             |  |  |  |

|                             | 5 <sub>10</sub> -58                          | 1 0                                     | \                           | 1 -             |  |  |  |

| . ti                        |                                              | 0 0                                     | 0 0                         | 0 -             |  |  |  |

| Δ.                          |                                              | 1 1                                     | \ <u></u>                   |                 |  |  |  |

|                             |                                              | 0 1                                     | 0 1                         | ¢ -             |  |  |  |

|                             | s <sub>10</sub> -5 <sub>9</sub>              | 0 0                                     | 0 0                         | ç -<br>D -      |  |  |  |

|                             | ľ                                            | 0 0                                     |                             | 1 -             |  |  |  |

|                             | 5, -5,                                       | 0 1                                     | 0 1                         | φ <u>1</u>      |  |  |  |

| į                           | "10 "11                                      | 1 0                                     | iô                          | 6 0             |  |  |  |

|                             | S, ~ S, ,                                    | 0 1                                     | 0 1                         | 0 0             |  |  |  |

| j                           | 10 12                                        | 1 0                                     | 1 0                         | 1               |  |  |  |

|                             | 510-513                                      | 0 1                                     | 0 1                         | ¢ 0             |  |  |  |

| i                           | 10 13                                        | 1 0                                     | 1 0                         | <u> </u>        |  |  |  |

| ;                           | 5 <sub>10</sub> -5 <sub>14</sub>             | 0 1                                     | 0 1                         | 0 0             |  |  |  |

|                             | <u></u>                                      | 1 0                                     | 1 0                         | 1 4             |  |  |  |

|                             | S <sub>10</sub> -S <sub>15</sub>             | 0 1                                     | 0 1                         | <b>* *</b>      |  |  |  |

|                             | <u>.                                    </u> | 1 0                                     | 1 0 1                       | <u> </u>        |  |  |  |

TABLE III FAULIS, TEST INPUTS, AND OUTPUTS IN VALID STATE  $S_3$   $^{\prime\prime}$

| ī a s          | Fault                              |                | Test       |               | Output        |               |              |   |

|----------------|------------------------------------|----------------|------------|---------------|---------------|---------------|--------------|---|

|                |                                    |                |            |               | Norma)        |               | ulty         |   |

|                |                                    | , ×            | *2 ·       | £,            | ÷2            | ı xî          | x,           |   |

| 춫              | *1. *2                             | 1              | 0          | 0             | 1             | 0             | 0            |   |

| 1              | $\mathbf{x}_1^1, \hat{\kappa}_2^1$ | 0              | 0          | 0             | n<br>0        | n             | 1            |   |

| <b>∷</b> ,     | ×;. 5;                             | 1 0            | 1          | 1             | Ú             | 0             | 0            |   |

| Ston           |                                    | 0              | 0          | 0             | <u>1</u>      | $\frac{1}{1}$ | - 6          |   |

| <del>,</del> - | 7. 1                               | $\frac{1}{0}$  | - <u>0</u> | $\frac{1}{1}$ | <u>i</u>      | 1 -           | 1            |   |

|                | \$5-5 <sub>0</sub>                 | 1 0            | 0          | 0             | )<br>0        | -             | -            |   |

|                | ļ                                  | 1              | 1          | 1             | 1             |               |              |   |

|                | \$ <sub>5</sub> -s <sub>1</sub>    | 1              | 0          | 0             | 0             | 1 0           | -            |   |

|                | 1 3 1                              | 0              | 0          | C             | 0             | 0             | <del>-</del> |   |

|                |                                    | 0              | 1          | 1             |               | <del> </del>  | 1            |   |

|                | 55 <sup>-5</sup> 2                 | 0              | 0          | C             | ),<br>Q       | -             | 0<br>0       |   |

|                | }<br>} <u></u>                     | 1              | 1          | 1             | 1             | <u> </u>      | 1            |   |

|                | 55-53                              | 0              | <u>0</u>   | 0             | 0             | 1 0           | 1<br>0       |   |

| 1 0 E          | ¢ . ¢                              | 0              | 0          | 1 0           | 0             |               | 0            |   |

|                | S5-S4                              | 0              | 0          | 0             | ō             | } _           | Ô            |   |

| אר היי         | <br>                               | 1 0            | <u>_1</u>  | $\frac{1}{1}$ | 1             |               | <del></del>  |   |

| Element        | 5-5 <sub>6</sub>                   | 1              | 0          | 0             | 1             | <u>-</u>      | •            |   |

|                |                                    | 0              | D<br>1     | 0             | 0             |               | 0            |   |

| Svítching      | 5"57                               | 0              | 0          | 0             | 0             | 1 0           | 0            |   |

| vit            |                                    | ΰ              | ì          | 1             | 0             | ō             |              |   |

|                | \$5~\$8                            | .1             | C<br>O     | 0             | 1<br>0        | 0             | _            |   |

| 11:            | ·                                  | 1_1            | 1          | 1             | 1             | 1             |              |   |

| i i            | \$ <sub>5</sub> -5 <sub>9</sub>    | 0              | 1<br>0     | 0             | 0             | •             | _            |   |

| # .            | , ,                                | 0              | 0          | 0             | 0             | 0             | <b>→</b>     |   |

|                | 5-510                              | <del></del>    |            | 1             | 0             | 0             |              |   |

|                | 55                                 | $-\frac{1}{0}$ | 0          | 0<br>1        | $\frac{1}{0}$ | <del>i</del>  |              |   |

|                | 3 11                               |                | <u>0</u>   | 0             | 1             | <u> </u>      | <u> </u>     |   |

|                | \$5 <sup>-8</sup> 12               | 0<br>1         | 0          | 0             | 0<br>1        | 0             | 0<br>_1      |   |

|                | 55-S13                             | 0<br>1         | 0          | 0             | 1             | •             | 0            |   |

| ļ              | 55-514                             | 0              | 1          | 1             | 0             | 0             | •            |   |

| j              | 5-S <sub>15</sub>                  | 0              | 1          |               | 0             | <del>1</del>  | <del>*</del> |   |

|                |                                    |                | 0          | _0_           | _1            | 4             | •            | _ |

### Algorithm A: Test vector design

1. Even links of stage ) receive test bit 1, odd links receive test bit 0.

#### end.

Definition 4: The S-phase of testing consists of setting all the SEs in the S-mode and performing the following tests:

- (i) feed the test vector, observe the output responses

- (ii) feed the complementary test vector, observe the output responses.

The X-phase of testing is done exactly as above with all the SEs set in X-mode.

Algorithm B : Testing a baseline network for single faults.

- 1. Generate the test vector by algorithm A.

- 2. Using the test vector of step 1 perform the 5-phase test.

- 3. Using the test vector of step 1 perform the X-phase test.

- 4. If there exists a single fault in the network some faulty response lines will be observed. As discussed in sec. 2.2.3, the fault can be diagnosed by additional tests if necessary.

#### end.

Theorem 1: The algorithm B ensures that all links and SEs receive complementary test bits in both valid states.

Proof: By testing the network in S-phase and X-phase, the SEs are tested in both valid states. Since each phase involves tests with complementary test vectors, every link receives complementary test bits. It remains to be shown that the SEs receive complementary test inputs in both phases.

(1) S-phase

Consider an NxN baseline,  $H = 2^n$ . In the S-phase a path P containing the link  $(p_{i-1}, \dots, p_0)_0$  will contain the link  $(p_0, \dots, p_{i-1}p_{n-1}, \dots, p_i)_i$ ,  $0 \le i \le n$ .

Now the input links of any SE of stage i,  $0 \le i \le n-1$ , will be of the form  $P_i = (p_0 \dots p_{i-1} p_{n-1} \dots p_i)_i$  and  $P_2 = (p_0 \dots p_{i-1} p_{n-1} \dots \overline{p_i})_i$ , which will receive the same test

bits as the links  $P_9 = (p_{n-1} \dots p_{l+1} p_l p_{l-1} \dots p_0)_0$  and  $P_4 = (p_{n-4} \dots p_{l+1} \overline{p_l} p_{l-1} \dots p_0)_0$  respectively.  $P_4$ ,  $P_9$  have the same number of 1's and so do  $P_2$ ,  $P_4$ . Since  $P_4$ ,  $P_2$  form an even-odd pair  $P_9$ ,  $P_4$  also form an even-odd pair. Hence by algorithm A,  $P_4$ ,  $P_2$  receive complementary test bits in S-phase.

# (II) X-phase

In the X-phase a path P containing the link  $(p_{n-1}, p_0)_0$  will contain the link  $(\overline{p}_0, ..., \overline{p}_{i-1}p_{n-1}, ..., p_i)_i$ ,  $0 \le i \le n$ .

Now the input links of any SE of stage i,  $0 \le i \le n-1$ , will be of the form  $P_4 = (\overline{p_0} \dots \overline{p_{i-4}} p_{n-4} \dots p_i)_i$  and  $P_2 = (\overline{p_0} \dots \overline{p_{i-4}} p_{n-4} \dots \overline{p_i})_i$ , which will receive the same test bits as the links  $P_3 = (p_{n-4} \dots p_i p_{i-4} \dots p_0)_o$  and  $P_4 = (p_{n-4} \dots \overline{p_i} p_{i-4} \dots p_0)_o$  respectively.

Case a : i is even :

$P_1$ ,  $P_3$  form an even-odd pair and so do  $P_2$ ,  $P_4$ . Since  $P_1$ ,  $P_2$  are an even-odd pair  $P_3$ ,  $P_4$  are also an even-odd pair.

Case b : i is odd :

$P_4$ ,  $P_9$  form either an even-even or an odd-odd pair and so do  $P_2$ ,  $P_4$ . Since  $P_4$ ,  $P_2$  are an even-odd pair  $P_9$ ,  $P_4$  are also an even-odd pair.

Thus by algorithm A,  $P_1$ ,  $P_2$  will receive complementary test bits in X-phase.

Q. E. D.

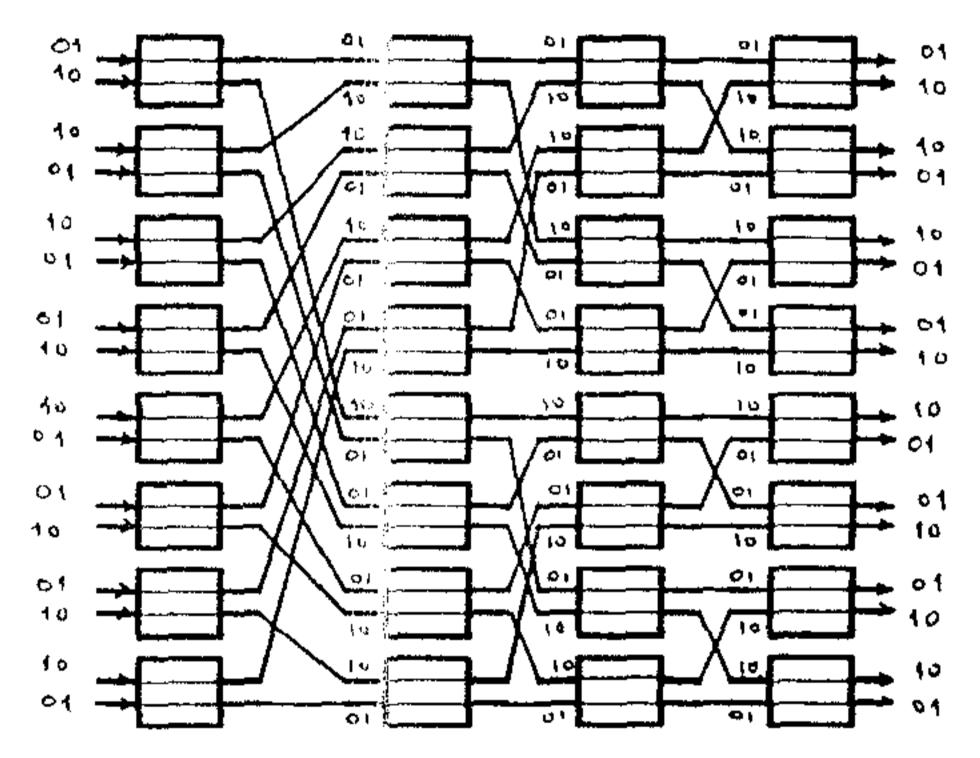

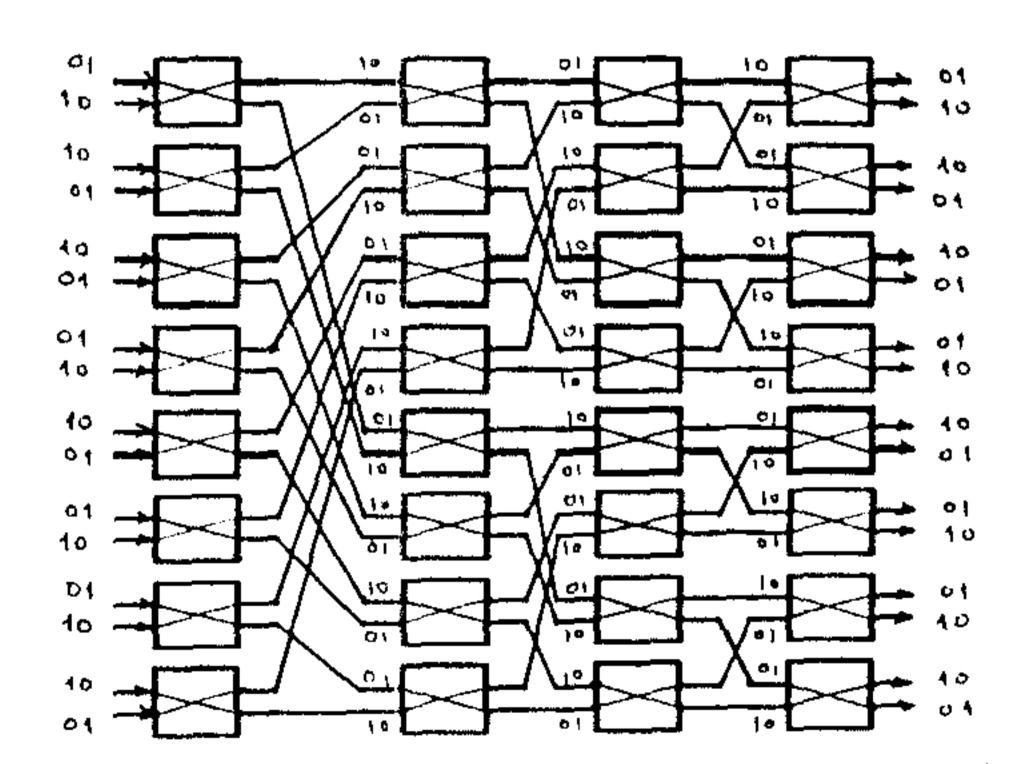

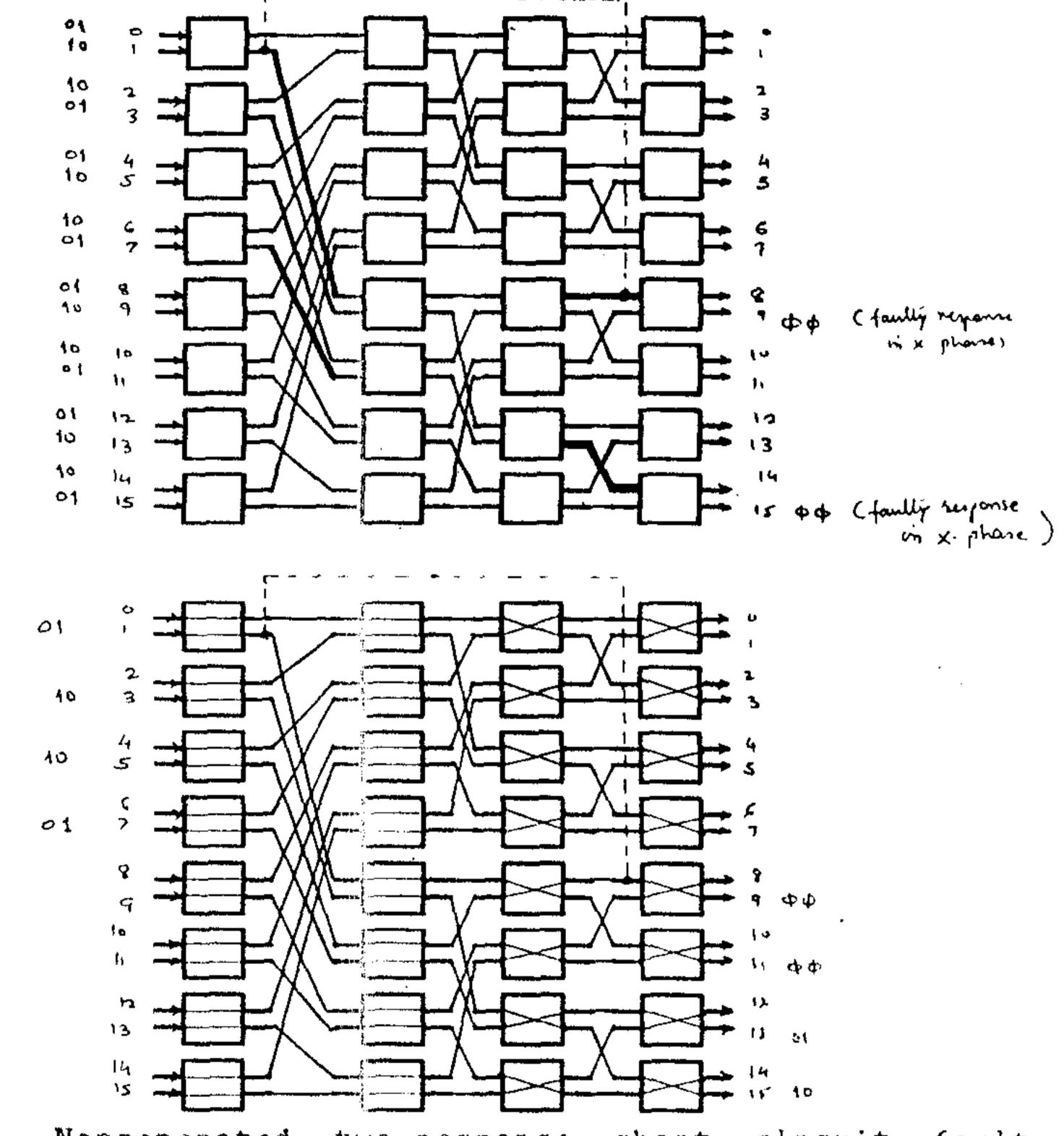

Fig. 8 and Fig. 9 show that all SEs receive complementary test inputs in both phases in a baseline network.

From tables I, II and theorem 1, it can be concluded that four test are necessary and sufficient to detect single fault at the SE or link level, independent of the network size.

Definition 6: Define the faulty output response as unary if the observed response is 00 or 11 in the two tests of a phase. Define it as binary if the observed response is 01 or 10, vis-a-vis a normal response of 10 or 01 respectively, in the two tests of a phase.

Note that open and short circuit faults will show unary response. Example of unary and binary faults is shown in

Fig. 7 Address assignment to links in a 8x8 baseline

Fig.8 Fault free response of a baseline network to the tests in S-phase

Fig.9 Fault free response of a baseline network to the tests in X-phase

fig. 10.

Algorithm C : Resolve shor, and open circuit condition of unary response fault

// It is necessary to know the location of the faulty SE. //

- 1. set the network as in the phase in which the unary fault was observed.

- Identify the input lines which lead to the faulty SE. Test the SE with test inputs (0, 0) and (1, 1) on these input lines and observe the faulty output lines. If the response is binary then fault is of short circuit type, else it is of the open circuit type.

end.

## 2.2.3 Casewise Diagnosis of Single Fault

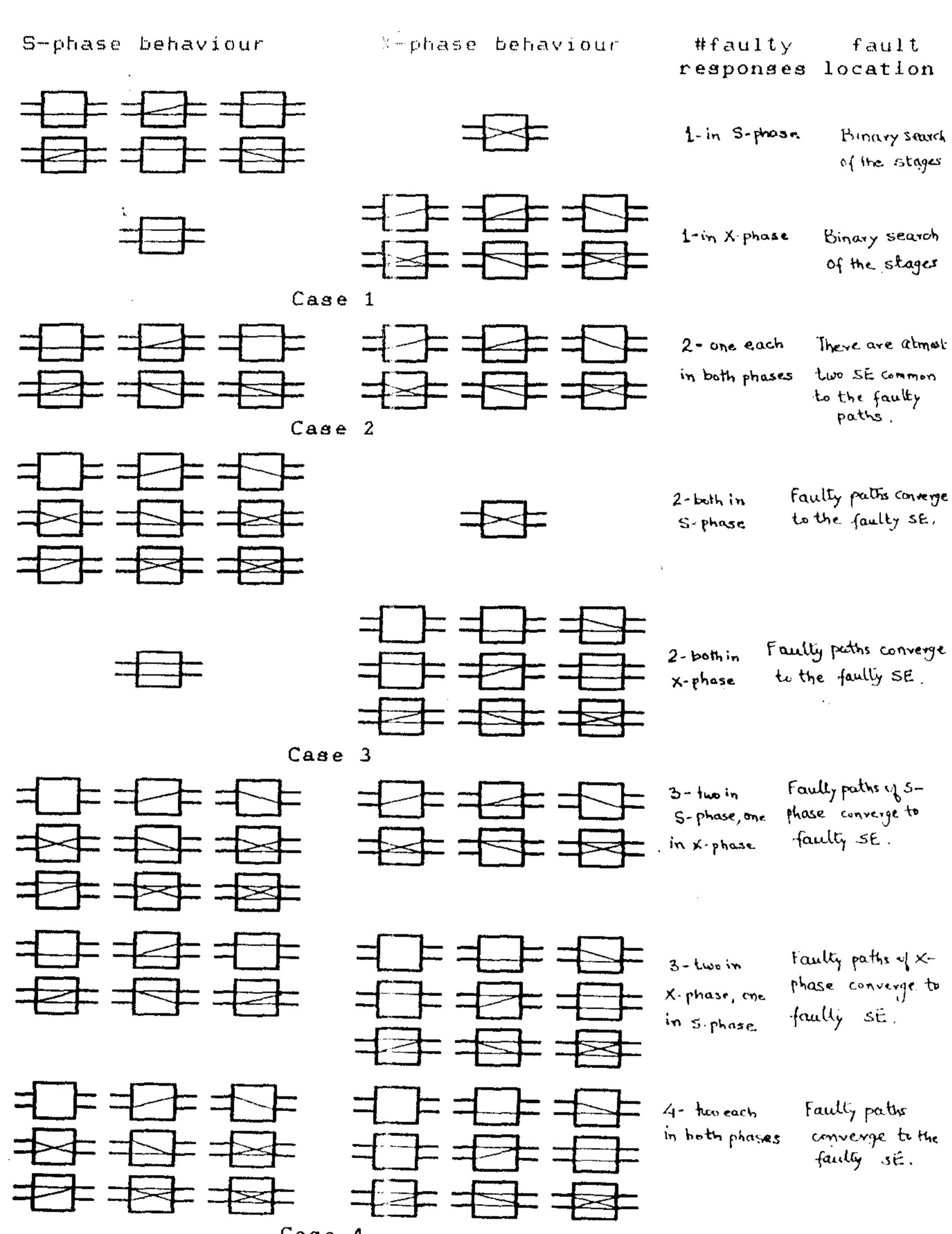

The four tests of algorithm B detect the fault and the following data is available from these tests: the number of faulty output lines, the behaviour of the faulty lines, and the phase in which they were observed. This data and a few other tests are sufficient to diagnose the fault. The 255 faults of the SE and the link stuck-type fault can be classified as follows:

- 1) One-response fault: There is only one faulty output which can be in S-phase or X-phase test.

- 2) Seperated two-response fault: There are two faulty outputs. One of them occurs in the S-phase test and the other occurs in the X-phase test.

- 3) Nonseperated two-response fault: There are two faulty outputs both occur either in the S-phase or the X-phase test.

- 4) Multiple-response fault : There are more than two faulty outputs

Fig. 12 pictorially shows the classification of all the 255 faults of the SE. Each of these four cases are considered in the following paragraphs.

Case 1: This case cover the 12 faults in the union of the sets  $\{S_4, S_9, S_8, S_{14}, S_{12}, S_{14}\} \times \{S_5\}$  and  $\{S_{10}\} \times \{S_1, S_9, S_4, S_9, S_{12}, S_{13}\}$ . The faulty SE can be anyone of the switching

Case 4

Fig 12. Classification of single SE faults.

elements lying on the faulty path and hence the data available from fault detection tests is insufficient for fault location. Using additional tests and technique of binary search of the stages, this fault can be diagnosed in at most  $4+2\lceil \log_{2}(\log_{2}N) \rceil$  tests.

Case 2: This case covers the 36 faults in the the set  $\{S_2,S_9,S_8,S_{11},S_{12},S_{14}\}\times\{S_1,S_1,S_1,S_2,S_2,S_3\}$ . It also includes the link stuck-type fault. The SE faults can be further classified as shown in tables IV and V. In this case at most two SEs will be common to the faulty paths. Faults of subcase A,B,C,D and E can be diagnosed in at most 16 tests, independent of the network size. The ambiguity of fault location of subcase F faults cannot be resolved by any test in which only the input-output terminals of the MIN are accessible. The subcase F faults are also indistinguishable from link stuck-type faults. Fig.11 shows the one-one correspondence between a subcase F fault and link stuck-type fault.

Case 3: This case covers the 18 faults in the union of the sets  $(S_0,S_1,S_4,S_5,S_6,S_7,S_9,S_{18},S_{15})\times(S_5)$  and  $(S_{10})\times(S_0,S_2,S_6,S_8,S_9,S_{10},S_{11},S_{14},S_{15})$ . The fault outputs converge uniquely to the faulty SE. Hence this fault can be diagnosed in at most 6 tests after resolving the short and open circuit conditions of the unary faulty outputs.

Case 4: This case can be subdivided into the following subcases

In both the above subcases the two faulty paths of one of the phases uniquely converge to the faulty SE. Hence this fault can be diagnosed in at most 8 tests after resolving the

Fig. 10 Examples of unary and binary behaviour of faulty output lines. Findicates faulty SE.

Table IV

Faulty output pattern for Case 2 faults.

Table V

Classification of the

| tot       | r Case 2 faul | ts.                      |              |                 | Li       | ase 7                   | tai       | 1118     | • | <b>.</b>     |

|-----------|---------------|--------------------------|--------------|-----------------|----------|-------------------------|-----------|----------|---|--------------|

| Sul       | one phase     | responses<br>other phase | Fault        | _               | 1        | sult<br>S <sub>12</sub> |           |          |   | <sup>7</sup> |

| A         | Binary        | Binary                   |              | Sg              | A        | A                       | В         | В        | С | C            |

| B         | Binary        | Unary (\$\$\$)           |              | S <sub>12</sub> | A        | A                       | В         | В        | В | C            |

| C         | Binary        | Unary ()                 |              | S <sub>7</sub>  | В        | В                       | E         | E        | D | D            |

| D         | Unary (44)    | Unary ()                 |              | S . 3           | В        | В                       | E         | E        | D | D            |

| E         | Unary (44)    | Unary (🍎 🗗 )             |              | Sı              | C        | С                       | С         | C        | F | F            |

| F         | Unary ()      | Unary ()                 |              | S4              | С        | С                       | С         | С        | F | F            |

|           |               |                          |              | 5-a             | <u>-</u> |                         |           | 5.a.     | - | 1            |

|           |               |                          |              |                 |          |                         |           |          |   |              |

|           |               |                          |              | <b>一</b>        |          |                         |           | <b>}</b> |   | ]-           |

|           |               |                          | =[           | ]-/             |          | ]=                      |           | }-       |   | }            |

| =         |               |                          |              |                 |          | ]=                      |           | <b>]</b> |   | 7=           |

|           |               |                          | . —          |                 | _        |                         |           |          |   |              |

|           | input         |                          | input Sau    |                 |          |                         |           | 于        |   |              |

| iput said | input         |                          | input searce |                 |          | input                   |           | ]=       |   |              |

|           | - F4'         | krut 5                   | output<br>-  |                 |          | <b>]=</b> ""            | put smand | -        |   | 5a-a output  |

|           | suit          | put                      | - outpat     |                 |          | ];                      | output    | •        |   | Frank output |

Fig. 11 Behavioural equivalence of subcase F fault of SE and link stuck-type fault. (Among the pair of dotted lines, one is an open connection and other is a normal connection)

short and open circuit conditions of the unary faulty outputs.

Table VI summarises the results of single switching element fault diagnosis of the baseline network.

TABLE XH

CHARACTERISTICS OF SINGLE FAULTS

| Cases                            | Fault Types                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Faulty<br>Output<br>Pattern | No. of<br>Fault<br>Types | No. of Tests Needed<br>For Determining the<br>Fault Location |                                                            |

|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|--------------------------|--------------------------------------------------------------|------------------------------------------------------------|

| Came 1:<br>One-Rospo<br>Fault    | <u></u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1 4                         | 4                        | 4+2[1067(1087N)]<br>07 4+2[10#2(10#7H)]                      | 0                                                          |

| Subca                            | (\$2,5),(\$8,5),(\$11,5),(\$14,5)<br>(\$10,5),(\$10,5),(\$10,5),(\$10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ,s <sub>13</sub> ) 4        | 8                        | 4+2[log_(log_N)]<br>or 4+2[log_(log_N)]                      | 7                                                          |

| ^                                | 12,15,15,1,12,2,15,13,15,17,13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | · 6                         | 4                        | 4 or 8                                                       | 0                                                          |

| Succ.                            | $(s_{12}, s_{13}), (s_{12}, s_{7}), (s_{3}, s_{13}), (s_$ | 1,S <sub>3</sub> ), Table 9 | 16                       | 4 of 6                                                       | 2                                                          |

| Subca                            | $E = \frac{(s_{11}, s_4), (s_{11}, s_1), (s_{14}, s_4), (s_{14}, s_1)}{(s_{11}, s_{13}), (s_{11}, s_{7}), (s_{14}, s_{13}), (s_{14}, s_{13})}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | S <sub>1</sub> }, Table [   | 12                       | 4, 8 or 12                                                   | 0 or 4                                                     |

| Subca<br>F                       | (s <sub>2</sub> ,s <sub>4</sub> ),(s <sub>2</sub> ,s <sub>1</sub> ),(s <sub>8</sub> ,s <sub>4</sub> ),(s <sub>8</sub> ,s <sub>1</sub> )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Teble<br>11                 | 4                        | (cannot be located at the single syltching element lovel)    | (not a distin-<br>guishable<br>from a link<br>stuck fault) |

| n-<br>parated<br>o-Respon<br>ult |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | .S <sub>15</sub> )          | 18                       | 4                                                            | 0 or 2                                                     |

| e 4:<br>ltiple-<br>sponse<br>ult | (S-S <sub>10</sub> ) × (S <sub>0</sub> ,S <sub>2</sub> ,S <sub>6</sub> ,S <sub>8</sub> ,S <sub>9</sub> ,S <sub>10</sub> ,S <sub>11</sub> ,S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | · i I                       | 189                      | 4                                                            | 0, 2, or 4                                                 |

#### 3.1 Problem definition and Mativation

In chapter 2 we have seen how single faults in a baseline network are diagnosed. The faults were restricted to switching element or link stuck-type fault. There is another important type of prevailent fault namely, short circuit fault among the links of the MIN. The problem is 'To study and develop diagnostic procedures for short circuit fault in MINs'. It is desirable that these procedures also incorporate the fault diagnosis of switching element faults as well.

A little insight into the problem will reveal that this general problem has the following parameters:

- 1. the number of links that belong to a short circuited group,

- 2. the number of disjoint groups of short circuited links or in other words, whether there is a single short circuit fault or there are multiple short circuit faults.

- 3. restrictions on the location of the faults i.e. whether or not the short circuited links belong to the same stage and

- 4. the class of MIN for which the fault diagnosis is studied.

Here we have restricted the problem to single fault with the number of short circuited links limited to at most three for the baseline network only. The fault location is unrestricted. The short circuit fault diagnosis for Benes network in the above framework is also proposed.

The upper bound on the number of tests for any general MIN in which the valid states of the SEs are either S-mode or X-mode has been obtained and the corresponding test vectors are also developed.

The area of fault diagnosis of MINs is assuming more and more importance because with the use of parallel systems expanding rapidly, system reliability measures are becoming prominent parameters for system performance.

To guarantee fault-free performance it is therefore

necessary to be able to test system components. It is desirable that such test procedures be algorithmic in nature so that automated implementation is possible and in view of widespread LSI/VLSI implementation of most system components, such test procedures should access only the input/output terminals.

The motivation behind the study of short circuit fault of MINs is that this fault is completely absent in the existing literature. Remarkably, this fault has not assumed importance in most fault diagnosis studies inspite of the fact that short circuit between two tracks (primarily adjacent) is one of the chief causes of defects in LSI/VLSI circuits. The study of short circuit fault will truly complete the fault diagnosis of single fault of baseline network.

[A82] mentions about short circuit fault behaviour restricted to the input/output lines of an SE which can be modelled by an equivalent fault of the SE. But a short circuit among adjacent tracks may, depending on the VLSI layout, translate to a logical short circuit fault among any generally located links. We have succeeded in conclusively diagnosing short circuit fault between two links of a baseline network.

The fault diagnosis of short circuit fault in a group of three links has also been completed, with the aim at solving the general problem. As the conclusions in section 3.7 indicate, the number of subcases for higher order short circuit fault (i.e. more than three short circuited circuited links in a group )increase rapidly and more importantly, it subsumes the fault behaviour of the lower order cases. Hence we could not pursue the problem for higher order.

The results of this study summarised are as follows:

1. Short circuit fault needs at most 2 log N tests for detection, in an NxN network having only S-mode and X-mode valid states of its SEs.

- 2. A baseline network with a two-link short circuit fault needs at most  $4\lceil \log_2 N \rceil + 4$  tests for diagnosis.

- 3. A baseline network with a three-link short circuit fault needs at most  $4\lceil \log_2 N \rceil + 6$  tests for diagnosis.

- 4. The short circuit fault can be distinguished from single SE fault except in a few cases.

- 3.2 Fault Model, Upper Bound on the Number of Tests and Test Vector Generation

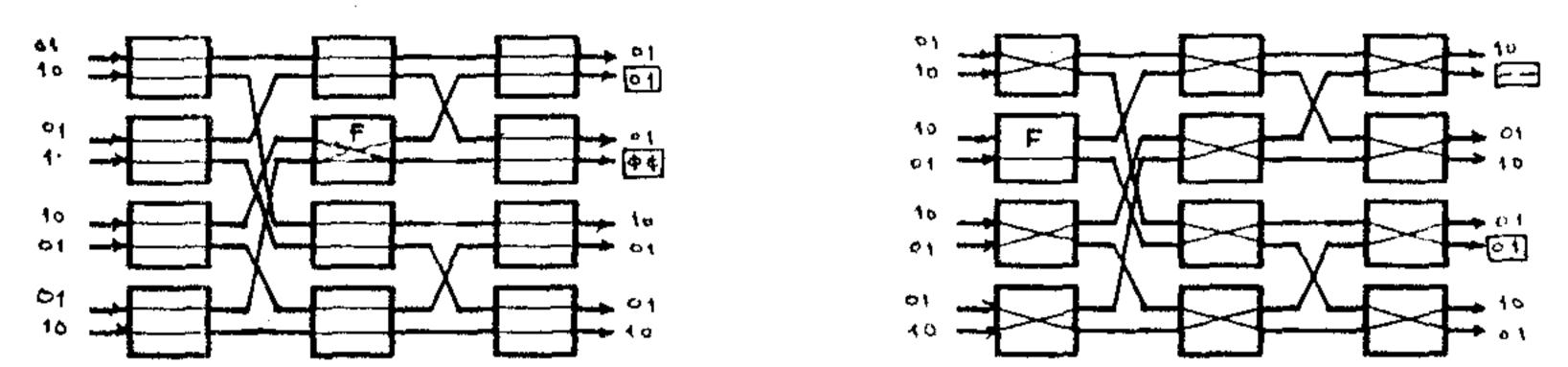

The logical value of a short circuited link is denoted by  $\Phi$  (c.f. def.2). The paths on which the short circuited links lie will give a  $\Phi$  response at the corresponding outputs when the test vector provides complementary test inputs to these paths and the short circuited links lie on different paths. The short circuit fault becomes transparent otherwise. This can be confirmed by a simple example of a 4x4 baseline network shown in fig. 13.

Thus the short circuit fault behaviour can be characterised as :

- a) Fault is visible when the short circuited links lie on different paths which receive complementary inputs.

- b) Fault is transparent when either the short circuited links lie on different paths which receive same test inputs or the short circuited links lie on the same path.

Upper bound on the number of tests :

Since we assume that the value of \$\psi\$ is an arbitrary but consistent assignment of 0 or 1, whenever a short circuit fault is visible with a given test vector, the faulty response will be observed only at some of the paths involved in the short circuit. To get hold of the other faulty paths we use the test strategy of testing the network in the same control setting with the complementary test vector. This is similar to the pair of tests in S-phase and X-phase discussed in definition 4.

Henceforth, we will always bear in mind that 'For a visible short circuit fault at least two faulty outputs will be observed with complementary test vectors.'

Therefore to test for a short circuit fault we need to ensure that all pairs of links in the network receive complementary test inputs.

Lemma 1: For an NxN MIN having S-mode and X-mode as valid states of its SEs, at most  $\lceil \log_2 N \rceil$  test vectors are needed to ensure that all pairs of links belonging to the same stage receive complementary test bits.

Proof: Let f(k) be the number of test vectors needed for the stated purpose. Our goal is to find f(N).

Now any test vector applied to an NxN MIN will have k 0's and (N-k) 1's, 0≤k≤N. With such a test vector all such pair of links of the input side one of which receives a 0 test bit and the other a 1. get tested for short circuit fault. Further tests are required to test short circuit fault among the group of links that received a 0 (size k) and the group that received a 1 (size N-k) independently. Hence we can write the following recurrence relation:

$f(N) \le 1 + \min (\max (f(k), f(N-k)))$

Clearly, as f(k) is a nondecreasing function the optimum value of k is  $\lceil N/2 \rceil$ , so that

$f(N) \leq 1 + f(\lceil N/2 \rceil)$

The solution of this equation is  $f(N) \leq \lceil \log_2 N \rceil$ .

Thus it can be concluded that all the pairs of input lines of a MIN can be provided complementary test bits using at most [log\_N] test vectors.

Now in any MIN having S-mode and X-mode as valid states of its SEs, all links of any stage have a one-one corresspondence with the links of the input side. Hence any pair of links belonging to the same stage will receive complementary test bits when their corressponding links at the input side do so. This concludes the proof.

Q. E. D.

This upper bound cannot be improved because at least [log\_N] test vectors are necessary to guarantee complementary test bits to any pair of links of the same stage.

Lamma 2 : For the baseline network :

- i) any two paths, one in S-phase and the other in X-phase share at most one link in common and and

- ii) if two links lie on the same path in one of the phases, they lie on different paths in the other phase.

Proof: Let the network have N input/output lines, N=2".

1. Let P be a path in S-phase and Q be a path in X-phase.

Let  $P_{o} = (p_{n-1} \dots p_{o})_{o}$  and  $Q_{o} = (q_{n-1} \dots q_{o})_{o}$  be their stage 0 links respectively. The proof is by contradiction.

Assumption: Let P,Q share more than one link, say one at stage i and the other at stage j,  $0 \le i, j \le n$ , where stage n denotes the output side. Then addresses of the links  $P_i, Q_i$  and  $P_j, Q_j$  lying on the path P,Q respectively will be

$$P_i = p_0 \dots p_{i-1} p_{n-1} \dots p_i$$

and  $Q_i = \overline{q}_0 \dots \overline{q}_{i-1} q_{n-1} \dots q_i$ , ...(a)  $P_j = p_0 \dots p_{j-1} p_{n-1} \dots p_j$  and  $Q_i = \overline{q}_0 \dots \overline{q}_{j-1} q_{n-1} \dots q_j$ . ...(b) w. 1. o. g., let i(j and since  $P_i = Q_i$  and  $P_j = Q_j$  equating the corressponding bits we get

$$p_{m} = q_{m}$$

,  $i \le m \le j-1$ , {from (a)}

$p_{m} = \overline{q}_{m}$ ,  $i \le m \le j-1$ , {from (b)}

contradictioni

Therfore P,Q share at most one link.

If they do share one link, say at stage i,  $0 \!\! \le \!\! i \!\! \le \!\! n$  , then the addresses of input links of P,Q are related as :

$$p_{m} = q_{m}$$

,  $i \le m \le n-1$ ,  $p_{m} = \overline{q}_{m}$ ,  $0 \le m \le i-1$ .

2. This proof follows directly from 1. For if the two links did not lie on different paths in the other phase then one path in S-phase and the other in X-phase will share two links contradicting 1.

Q. E. D.

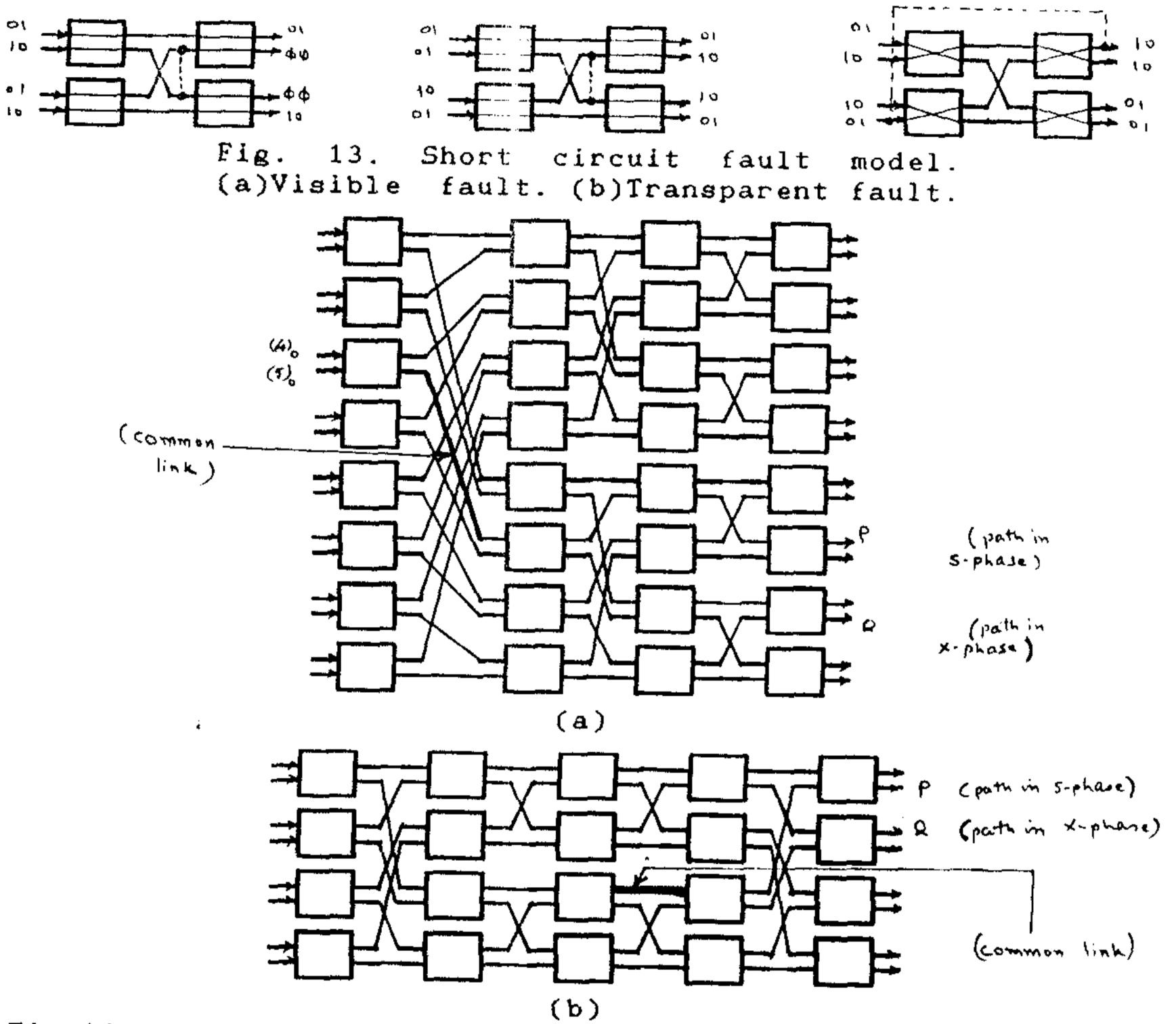

Definition 7: Call two paths intersecting, if they share a common link.

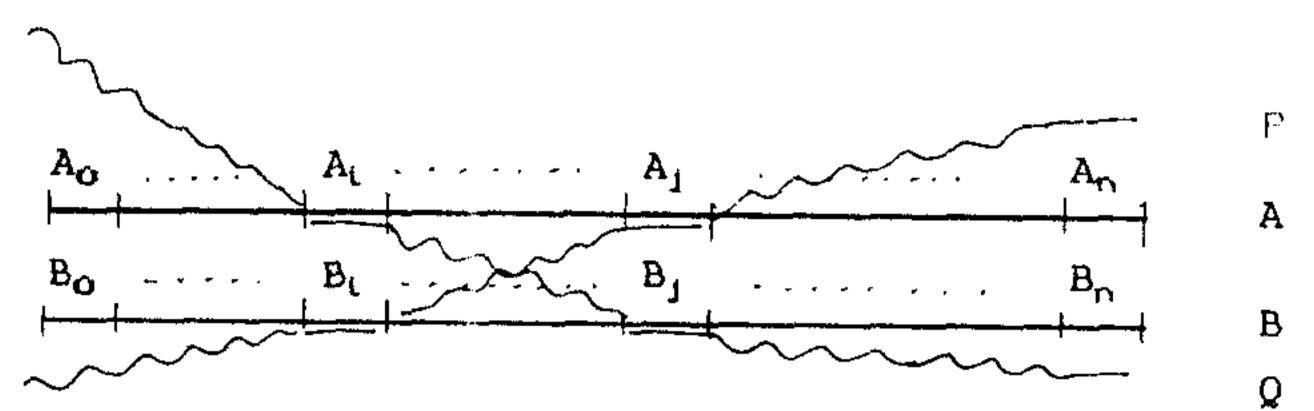

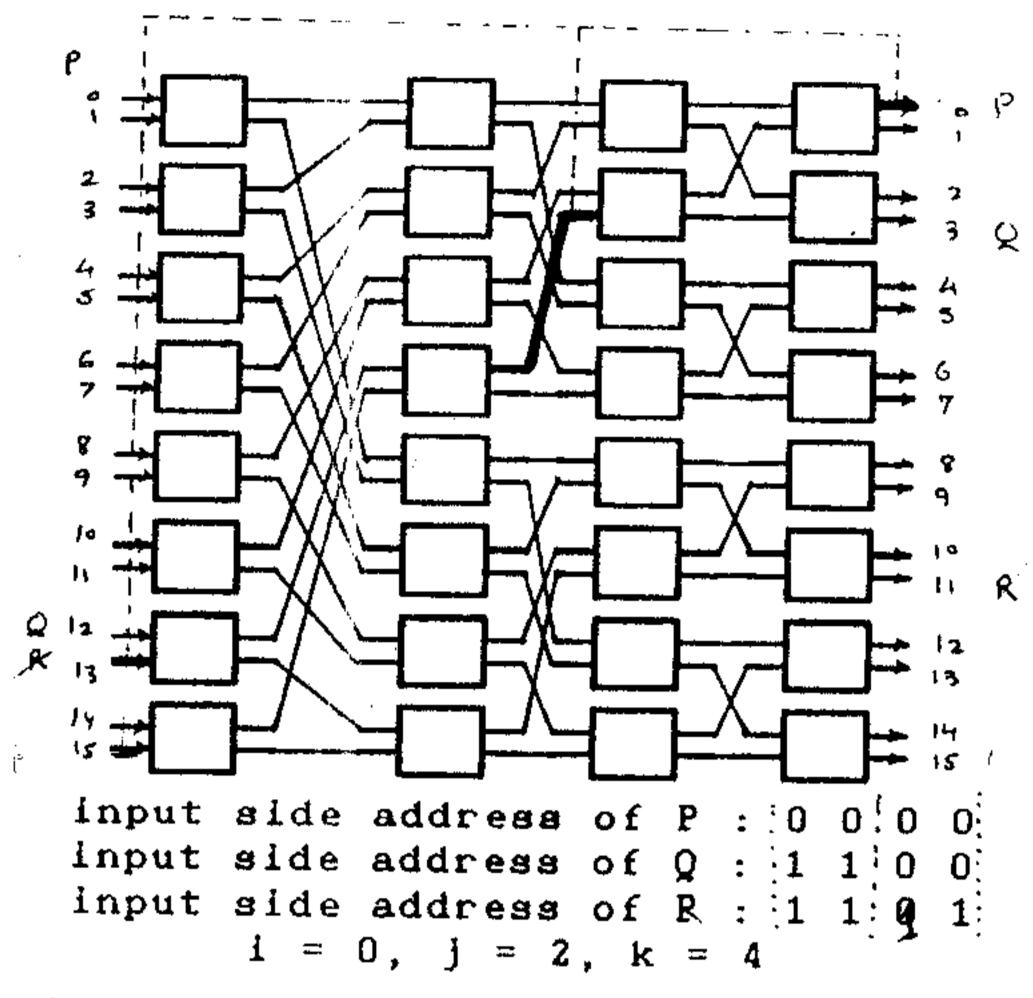

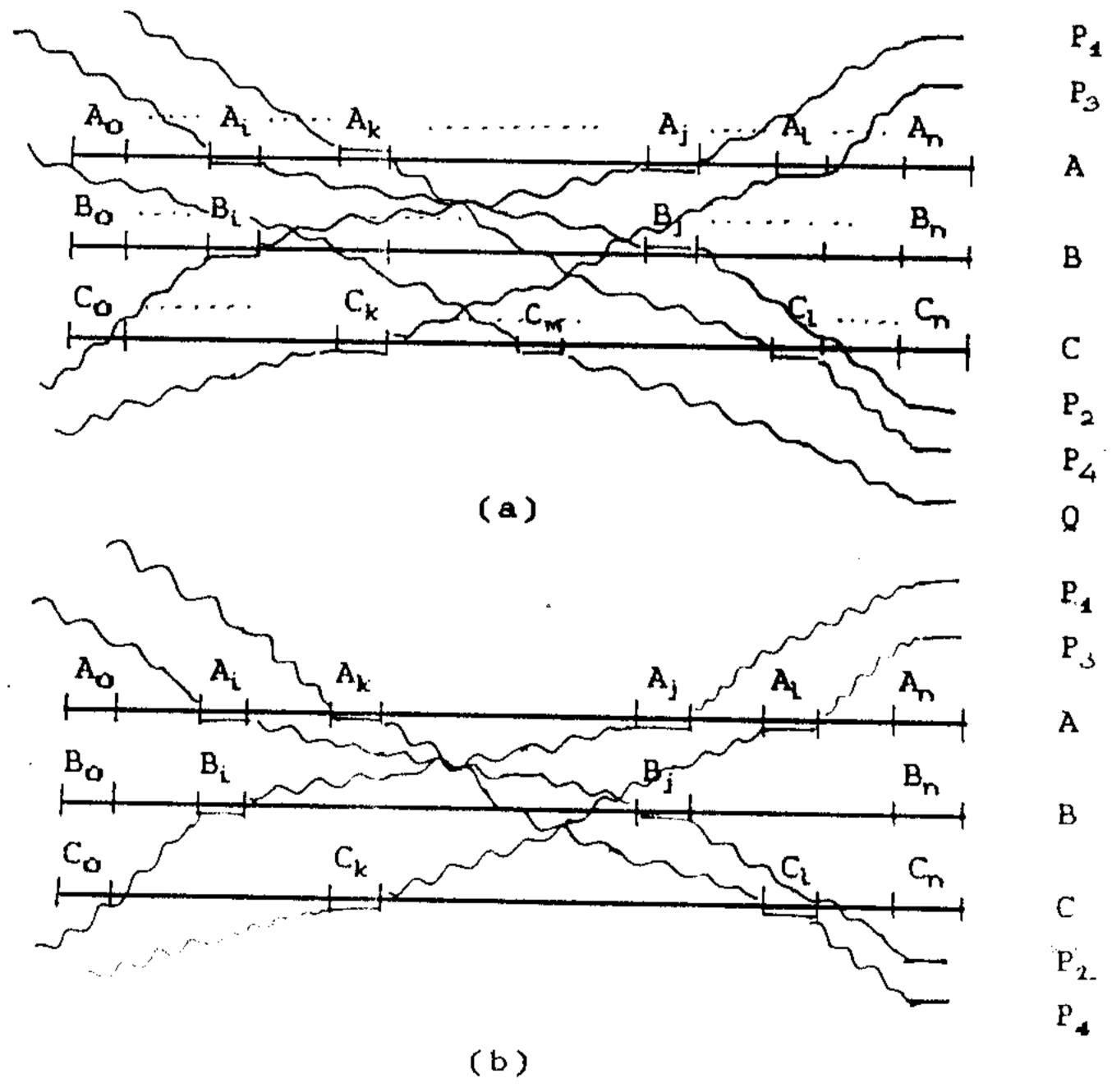

Obviously the intersecting paths must be from different control settings of the MIN. Fig.14 shows intersecting paths in baseline and Benes network. In fig.14(a) P is the path in

Fig. 14. Example of intersecting paths in baseline and Benes networks.

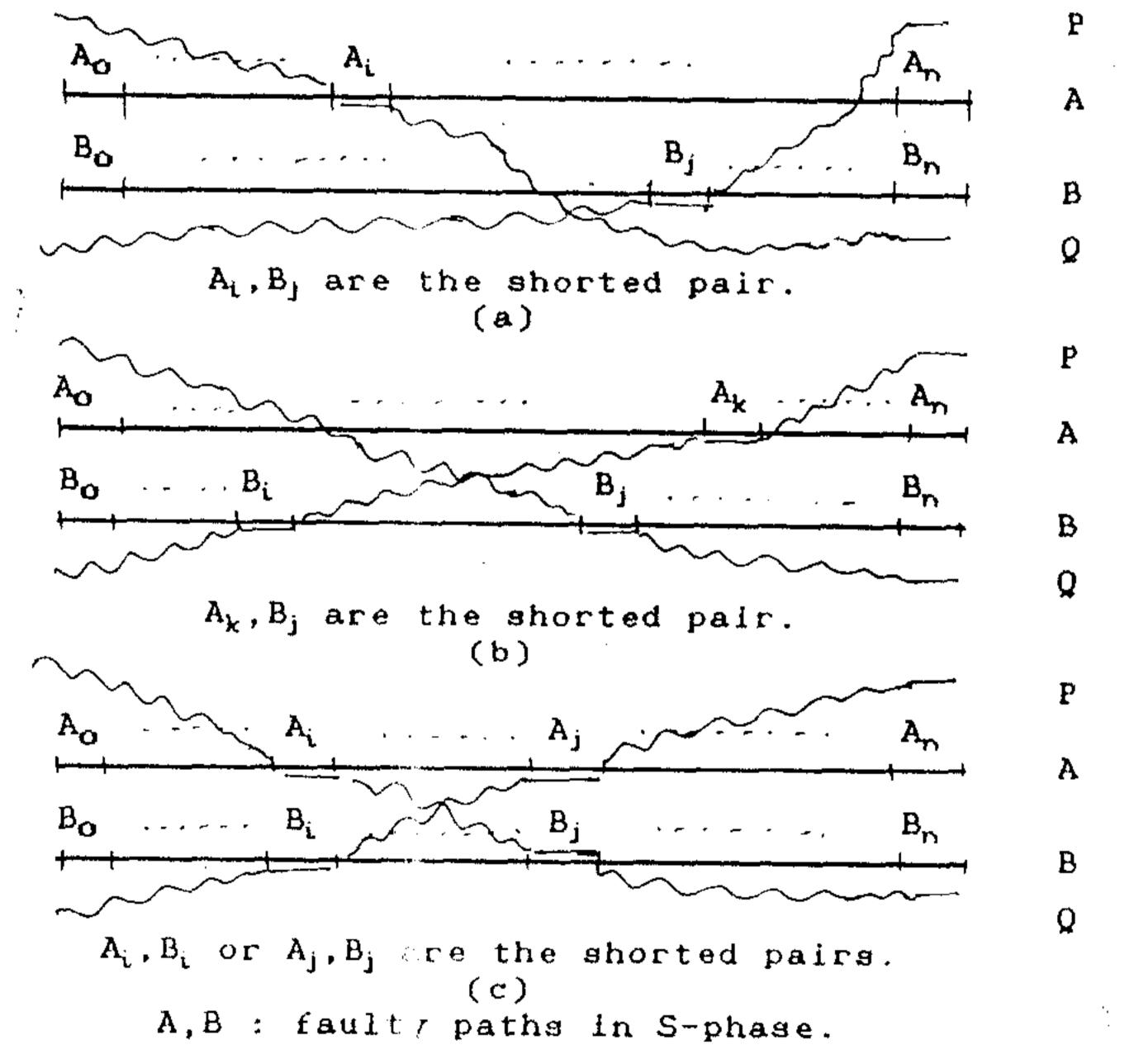

Fig 15. Test vector: generated by algorithm A.

S-phase with input side address  $(5)_{o}$ , and 0 is the path in X-phase with input side address  $(4)_{o}$ .

Theorem 3: Short circuit fault in baseline and Benes network can be detected in at most  $2\lceil \log_2 N \rceil$  tests.

Proof: Lemma 1 gives the upperbound on the number of test vectors that will ensure complementary test bits to any pair of links that belong to the same stage.

Now for any MIN having S-mode and X-mode as valid states of its SEs, there is a one-one correspondence, in any control setting of the MIN, between a link of the MIN and an input line of the MIN given by the mapping:

g : any link L --- input link of the path containing L.

So any two links L and L' will receive complementary test bits when g(L) and g(L') do so. If g(L) = g(L') then the fault becomes transparent.

So any pair of links that lie on different paths in any control setting of such a MIN will receive complementary test bits in at most [log\_N] tests.

Choosing the S-phase as the MIN control setting, lemma 2 ensures that any pair of links will lie on different paths in at least one of S-phase and X-phase.

Hence in particular, the short circuit fault in baseline and Benes network can be detected in at most 2 [log N] tests.

Q. E. D.

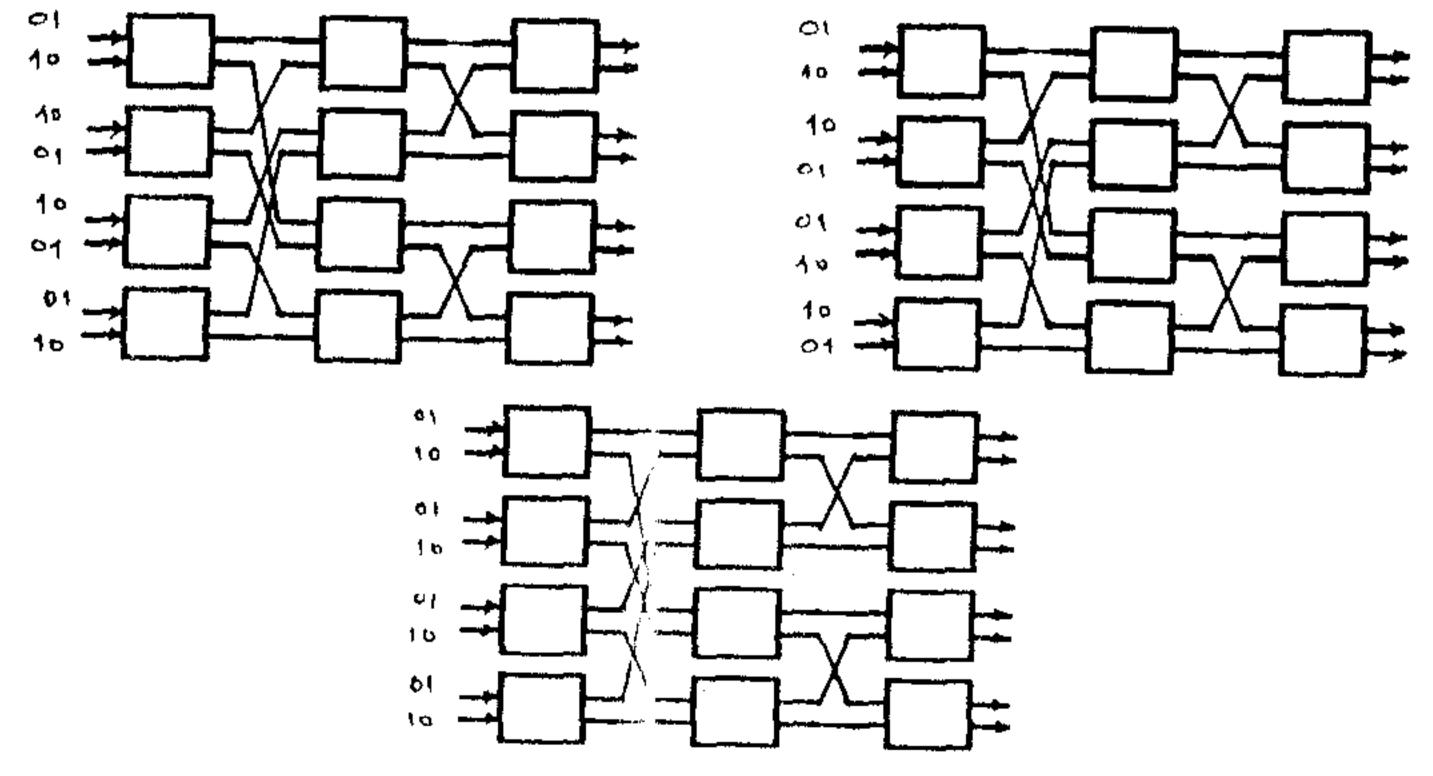

The following algorithm generates the test vectors for detecting single short circuit as well as single SE fault.

Algorithm D : Test vectors to test NxN baseline network,  $N=2^n$

- 1. For i = n downto 1 do

- Classify the input lines into odd and even lines based on the i-leftmost bits of their address.

- 3. Even lines receive a test bit 1, odd lines receive a test bit 0.

endfor

end.

Fig. 15 gives the test vectors generated for a 8x8 baseline.

# 3.3 Diagnosis of Single Fault of Baseline Network

We now discuss the diagnostic procedures for single short circuit fault jointly with the SE fault. The first iteration of algorithm D generates the same test vector as that of algorithm A. The test procedure is modified as follows:

- (i) For every test vector generated by algorithm D, test the network with that test vector and its complement in both S-phase and X-phase.

- (ii) Based on the discussion in sec 3.4 and 3.5 additional tests are done appropriately for diagnosing the fault.

Note that if single SE fault exists, it will be observed with the test vector generated in the first iteration of algorithm D itself. During any subsequent tests, if we observe a faulty output, only then its complementary test is required to get hold of all the faulty paths. Otherwise, the complementary test of the subsequent tests can be skipped.

The test procedure discussed above will cause at least two faulty output responses in a phase if the fault is visible in that phase with the given test vector. A single short circuit fault can have k-short circuited links,  $2 \le k \le N \log_2 N$ . We have studied and given fault diagnosis procedures for k=2 and k=3. The conclusions of section 3.7 discuss the difficulties for k>3.

# 3.4 Short Circuit Fault among Two Links in Baseline Network

The fault can be classified on the basis of output responses as follows:

- 1. Nonseperated two-response fault: There are two faulty outputs in one phase, the other phase is fault-free.

- 2. Four-response fault: There are two faulty outputs in each phase.

# 3.4.1 Diagnosis of Nonseperated Two-response Fault