# Routing Algorithms for Channels, Switchboxes and MCM's in VLSI Layout Design

Dissertation submitted for the degree of

Doctor of Philosophy

of the

Indian Statistical Institute

Sandip Das

Advanced Computing and Microelectronics Unit Indian Statistical Institute 203, B. T. Road, Calcutta - 700 035 INDIA

(Revised)

**DEDICATION**

To my parents

#### Contents

| 1 | Introduction                                               | ]  |

|---|------------------------------------------------------------|----|

|   | 1.1 Background                                             | ]  |

|   | 1.2 Scope of the Thesis                                    | 3  |

|   | 1.2.1 Channel routing                                      | 3  |

|   | 1.2.1.1 Over-the-cell routing                              | 4  |

|   | 1.2.1.2 Via minimization                                   | 6  |

|   | 1.2.2 Channel routing in Manhattan-diagonal model          | 7  |

|   | 1.2.3 L-shaped channels, staircases and switchboxes        | 8  |

|   | 1.2.4 Routing in multi-chip modules (MCM)                  | ç  |

|   | 1.3 Conclusion                                             | 11 |

| 2 | Review                                                     | 12 |

|   | 2.1 Introduction                                           | 12 |

|   | 2.2 Fabrication Factors                                    | 13 |

|   | 2.3 Global Routing                                         | 14 |

|   | 2.3.1 Different design styles                              | 15 |

|   | 2.3.2 Existing methods for global routing                  | 16 |

|   | 2.4 Detailed Routing                                       | 18 |

|   | 2.4.1 Routing considerations                               | 19 |

|   | 2.4.2 Routing models                                       | 20 |

|   | 2.4.3 Channel routing                                      | 21 |

|   | 2.4.3.1 Single row routing problem                         | 22 |

|   | 2.4.3.2 Single layer routing algorithm                     | 22 |

|   | 2.4.3.3 Two-layer channel routing algorithm                | 23 |

|   | 2.4.3.4 Multi-layer channel routing algorithm              | 25 |

|   | 2.4.3.5 Via minimization and over-the-cell channel routing | 26 |

|   | 2.4.4 L-shaped channel and switchbox routing               | 27 |

|   | 2.5 MCM Routing                                            | 28 |

| 3 | Over-the-cell Channel Routing                              | 30 |

|   | 3.1 Introduction                                           | 30 |

|   | 3.2 Formulation of the Problem                             | 30 |

|   | 3.2.1 Basic steps                                          | 31 |

|   | 3.2.1.1 Initial terminal selection                         | 31 |

|   | 3.2.1.2 Over-the-cell routing                              | 33 |

|   | 3.2.2 The proposed cost function                          | 36 |

|---|-----------------------------------------------------------|----|

|   | 3.3 Heuristic Algorithm                                   | 37 |

|   | 3.3.1 Method                                              | 37 |

|   | 3.3.2 Complexity of the algorithm                         | 38 |

|   | 3.4 Experimental Results                                  | 38 |

| 4 | Via Minimization in Channel Routing                       | 40 |

|   | 4.1 Introduction                                          | 40 |

|   | 4.2 Layout Modification                                   | 42 |

|   | 4.3 Scope of Modification                                 | 45 |

|   | 4.4 Via Minimization Algorithm                            | 49 |

|   | 4.5 Experimental Results                                  | 51 |

|   | 4.6 Conclusion                                            | 52 |

| 5 | Channel Routing using Manhattan-Diagonal Model            | 56 |

|   | 5.1 Introduction                                          | 56 |

|   | 5.2 Main Results                                          | 57 |

|   | 5.3 Preliminaries                                         | 57 |

|   | 5.4 Channel Routing in Reserved Layer MD Model            | 59 |

|   | 5.4.1 Formulation                                         | 59 |

|   | 5.4.2 Algorithm: 1 (Reserved layer MD router)             | 64 |

|   | 5.4.3 Experimental results                                | 65 |

|   | 5.5 Routing in Unserved Layer MD Model                    | 66 |

|   | 5.5.1 Resolving cyclic conflict in vertical constraints   | 66 |

|   | 5.5.2 Theme of the algorithm                              | 67 |

|   | 5.5.3 Algorithm: 2 (Unreserved layer MD router)           | 68 |

|   | 5.5.4 Experimental results                                | 70 |

| 6 | Routing in L-Shaped Channels, Switchboxes, and Staircases | 74 |

|   | 6.1 Introduction                                          | 74 |

|   | 6.2 Routing in L-shaped Channels                          | 75 |

|   | 6.2.1 Scheme for L-channel routing                        | 76 |

|   | 6.2.2 Triangular channel routing                          | 77 |

|   | 6.2.3 L-channel router MD-L                               | 81 |

|   | 6.2.3.1 Experimental results                              | 83 |

|   | 6.3 Routing in Switchboxes and Staircases                 | 88 |

|   | 6.3.1 Switchbox routing                                   | 88 |

|   |                                                           |    |

|   |                                                           |    |

|   |                                                           |    |

.

.

.

| 10  | List of Publications of the Author related to this Thesis | 131 |

|-----|-----------------------------------------------------------|-----|

| 9 B | Biblography                                               | 116 |

| 8   | Conclusion                                                | 113 |

|     | 7.6 Conclusion                                            | 112 |

|     | 7.5 Experimental Results                                  | 111 |

|     | 7.4.3 Removal of redundant vias                           | 110 |

|     | 7.4.2 Permutation of tracks                               | 109 |

|     | 7.4.1 Flipping of layers                                  | 108 |

|     | 7.4 Via Minimization                                      | 108 |

|     | 7.3.2.3 Routing of multi-terminal nets                    | 107 |

|     | 7.3.2.2 Routing of two-terminal nets                      | 103 |

|     | 7.3.2.1 Routing inside a block                            | 102 |

|     | 7.3.2 Routing of nets                                     | 101 |

|     | 7.3.1 Ordering of nets                                    | 98  |

|     | 7.3 Proposed Routing Technique                            | 98  |

|     | 7.2 Preliminaries                                         | 95  |

|     | 7.1 Introduction                                          | 94  |

| 7   | Via Minimization in MCM Routing                           | 94  |

|     | 6.4 Conclusion                                            | 93  |

|     | 6.3.2 Staircase routing                                   | 92  |

|     | 6.3.1.1 Experimental results                              | 90  |

|     | 6.3.2 Staircase routing                                   | 9   |

#### Acknowledgment

I intend to give vent to my profound feeling of gratitude to Professor Bhargab B. Bhattacharya who evoked in me a deep insight into the way to concentrate to this novel course. His perennial and constant guidance to find the wayout from the entangled labyrinth deserves no less expression.

I shall be lacking in my gratitude in case of any lapse from properly mentioning the contributions of Professor Bhabani P. Sinha for the suggestions and encouragement to overcome as and when frustration and problems overtook me.

No less worth mentioning are the help and assistance I had received from Professor Mihir K. Chakrabarti, Professor Jayasree Dattagupta, Dr. Nabanita Das, Dr. Susmita Sur-Kolay, Dr. Subhas C. Nandy and Professor Malay K. Sen at the various stages of progress of the work.

I do not find proper words to express my thanks for the invaluable assistance I had received from my friends Dr. Krishendu Mukhopadhyaya, Dr. Srabani Sen Gupta, Dr. Debesh Das, Dr. Susanta Chakrobarti, Dr. Rajib Das, Dr. Mallika De and Arijit Bishnu.

I shall prove ungrateful if I fail to mention about Mrs. Sumita Sinha and Mrs. Sarmistha Bhattacharya who had been encouraging me during my long course of research.

Last but not the least, I thank my parents, my brothers, my sister, my wife and my daughter for being themselves and making me what I am today.

January 20, 2000 Indian Statistical Institute Calcutta

Sandip Das

# Chapter 1

## Introduction

## 1.1 Background

The term *Very Large Scale Integration (VLSI)* reflects the capability of semi-conductor industry to fabricate a complex electronic circuit consisting of millions of components on a single silicon substrate. The growth of semiconductor technology in recent years has been described by "Moore's law", enunciated in the late 1960's, which projected quadrupling of components in a chip in every three to four years. Several factors contributed to this tremendous growth: (i) reduction of line width of the basic device and interconnection wires due to the development of high-resolution lithographic techniques and improved processing capabilities, (ii) increase in the size of the silicon wafer due to improved reliability of processing, (iii) growth of the accumulated circuit, and (iv) layout design experience. Better understanding of system level design issues leads to improved architectures exploiting the current technology, and helps in designing efficient electronic design automation (EDA) tools for logic synthesis, circuit layout, simulation, verification, and testing.

Microelectronics technology is advancing very rapidly. The design styles and tools are also undergoing a continuous evolution. The custom design style incorporates maximum flexibility; the designers have at their disposal the entire array of design tools, i.e., logic capture, layout, design verification, simulation, timing verification, placement and routing.

VLSI technology plays a major role in the development of complex electronic systems. As a result of continuing progress in semiconductor technology, around 100,000 to several millions of transistors can now be put on a single micro-chip. New design methods for VLSI are therefore of constant need to cope with this increased design complexity.

The VLSI design process spans a diverse spectrum of disciplines in physics, chemical engineering, electrical engineering, and computer science. Because of the diversity of tasks and design issues, a systematic approach to breaking the process into a number of design layers and subtasks is essential. Typically, the top-down design of a chip consists of the following stages:

- (i) design specification

- (ii) functional design

- (iii) logic design

- (iv) circuit design

- (v) physical design

- (vi) fabrication on semiconductor chips.

Each stage consists of synthesis, analysis and verification, and iterations may be necessary in order to eliminate errors. Layout design is essentially a stage of physical design where behavioral and structural representations of an electronic system are translated to geometric shapes to be used during fabrication. Several problems arise during the layout design of VLSI chips. This includes partitioning the components into homogeneous groups, placement of modules on the floor and finally, routing, i.e., interconnection (wiring) among the modules.

The work reported in this thesis is mainly concerned with the development of new and efficient routing algorithms. Once a circuit is partitioned and elements are placed on board, it is necessary to implement the connection patterns amongst the modules using signal nets.

The objective of routing strongly depends on the nature of the chip. For general purpose chips, it may be sufficient to minimize the total wire length in order to reduce the chip area. For high performance chips, total wire length may not be a major concern. Instead, one may want to minimize the length of the longest wire to minimize the delay in signal propagation and, to reduce crosstalk to enhance its performance. The presence of large number of vias (contact holes across layers) is undesirable from fabrication and circuit performance point of view. So, via minimization also plays an important role in designing routing algorithms. Similar other parameters need to be considered depending on the design goals.

Unfortunately, efficient algorithms satisfying all these conflicting goals are in general hard to find. Several researchers identified different sub-problems for example, row routing, channel routing, switchbox routing, global routing, etc., and attempted to solve these problems either in isolation or in totality. Even in many simple situations,

an optimal solution is hard to find. In fact, most of these layout optimization problems have been proved to be NP-hard [S93]. Algorithms for solving such problems may give optimum results in polynomial time in some special situations, but in most of the cases, they remain intractable. In this thesis, our goal is to identify new types of routing problems, investigate them critically, and to develop efficient algorithms based on graph theory, combinatorics and related mathematical tools, and finally, to implement them for industrial use.

## 1.2 Scope of the Thesis

Channel routing is one of the most important and probably one of the most popular phases of physical design for VLSI chips as well as PC-boards. One of the earliest algorithms in this area was due to Hashimoto and Stevens [HS71]. Since then, various methods were extensively studied and applied to many different technologies. It may be noted that with the advent of availability of multiple routing layers, the classical channel routing problem seems to have lost its full significance. However, the basic algorithms are useful for routing in a system-on-a-chip environment, as well as in an MCM. In this thesis, we focus on the following problems, and propose new techniques for solving them:

- 1. Over the cell channel routing;

- 2. Via as well as wire length minimization in channel routing problem;

- 3. Channel routing in manhattan diagonal model;

- 4. L-shaped channel routing;

- 5. Switchbox routing;

- 6. Routing in multi-chip modules (MCM).

Descriptions of these problems are summarized in the following sections. Novel techniques and data structures have been utilized for their modeling. The proposed methods, based on graph algorithms, and computational geometry incorporate many new features, and experiments on benchmarks demonstrate their superiority to the existing ones from the viewpoint of running time, space requirement, and generality.

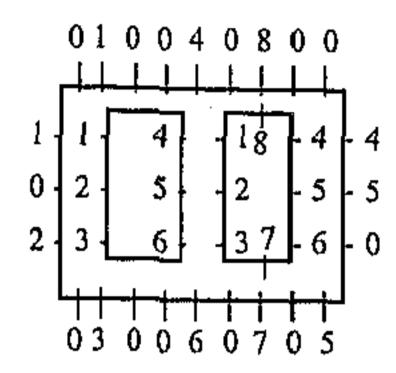

## 1.2.1 Channel routing

A channel is a routing region bounded by two parallel rows of terminals. Without any loss of generality, it is assumed that the two rows are horizontal. Each terminal is assigned a number which represents the net to which the terminal belongs to, and it appears on the top and bottom boundaries of the channel. Zeros represent vacant terminals which do not belong to any net. The netlist of a channel is the input to most of the channel routing algorithms.

The horizontal (vertical) dimension of the routed channel is called the channel length (channel width). In channel routing problem, the goal is to find the interconnections of all the nets in the channel in the specified area. Generally, two or more layers are available for routing. Change of layers for nets is done through holes called vias. The main objective of the channel routing is to minimize the channel width. Additional objective functions are minimization of the number of vias used in a multilayer channel routing, minimization of wire length, etc. In grid-based reserved layer models, the horizontal wire segments appear on tracks which are vertically equidistant inside the channel. Here, the objective essentially is the assignment of horizontal segments of nets to the tracks. Vertical segments are used to connect horizontal segments of the same net in different tracks with the pins appearing along the boundaries of the channel. In the unreserved layer model for two-layer routing, vertical and horizontal wires may pass through both the layers. In this situation, though the width of the channel reduces drastically, the routing becomes complicated.

The first theoretical bound of the track requirement is given by Kawamoto and Kajitani [KK79], where they suggested a column-by-column routing algorithm that guarantees routing with an upper bound on the number of tracks equal to the density plus one, where the density of a channel routing instance is the highest congestion over all columns. The congestion of a column is the number of nets passing through that column. In this method, additional columns may occasionally be needed to complete the routing. The first algorithm developed for channel routing was the left-edge algorithm, proposed by Hashimoto and Stevens [HS71] which uses a reserved layer model and does not allow doglegs and any vertical constraints. Ho, Iyenger and Zhenq [HIZ91] developed a simple but efficient heuristic channel routing algorithm which is greedy in nature and can be generalized to switchboxes and multi-layer problems.

#### 1.2.1.1 Over-the-cell routing

.· .·

The total area in the standard cell design style is equal to the sum of the total cell area and the total channel area. For a given layout, the total cell area is fixed. Thus, the total area of a layout can only be reduced by decreasing the total channel area. Conventionally, in two-layer layout, cells appear in a single metal layer. Routing is done through both the metal layers in the channel area. As several channel routers have been developed that complete routing with the number of tracks very close to the channel density, no further improvement in the layout area is possible, if routing is done only through channels.

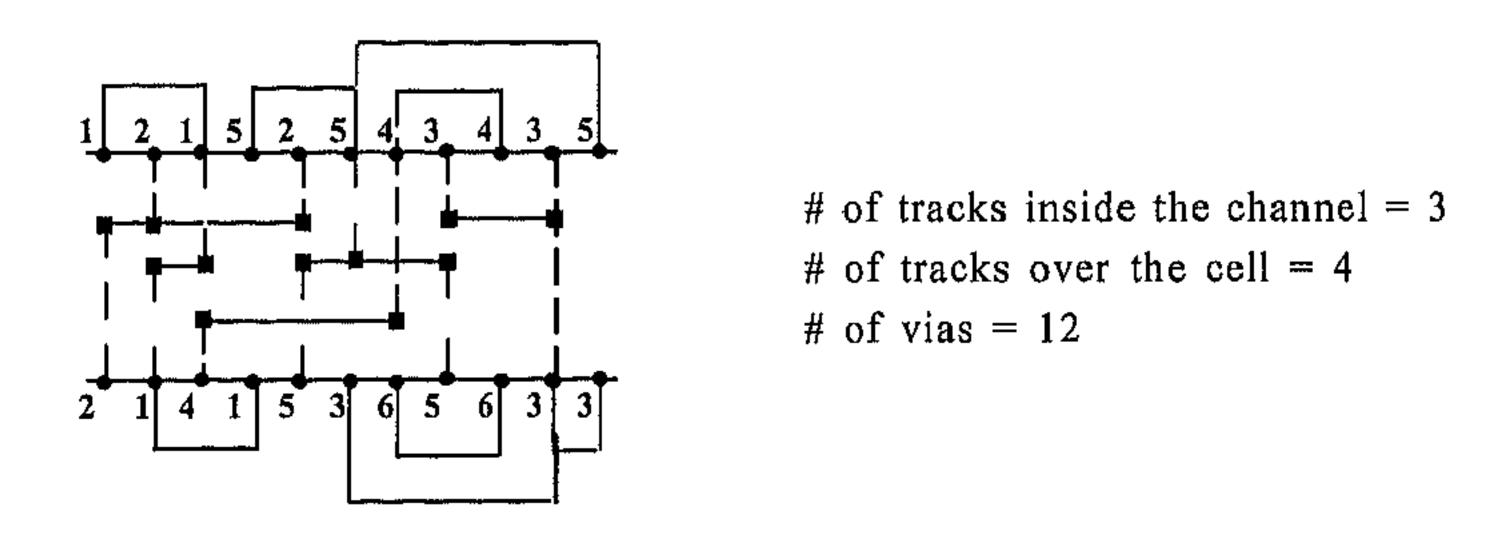

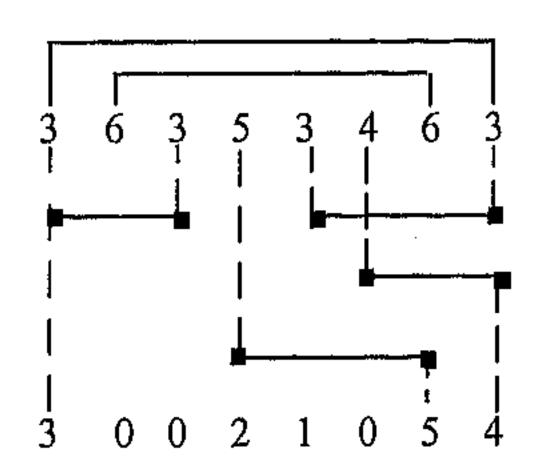

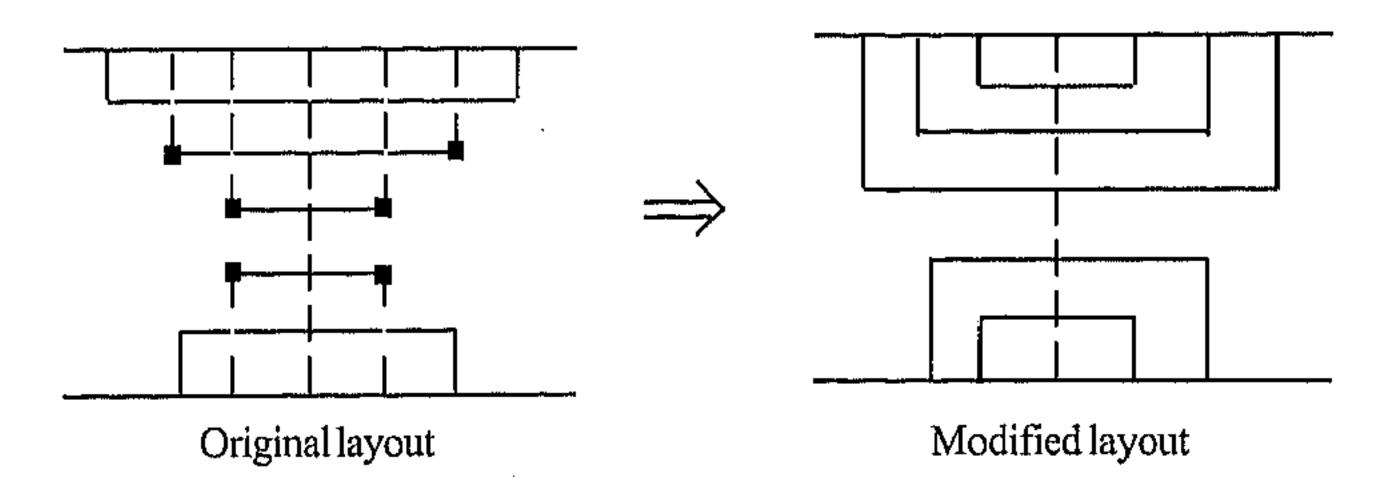

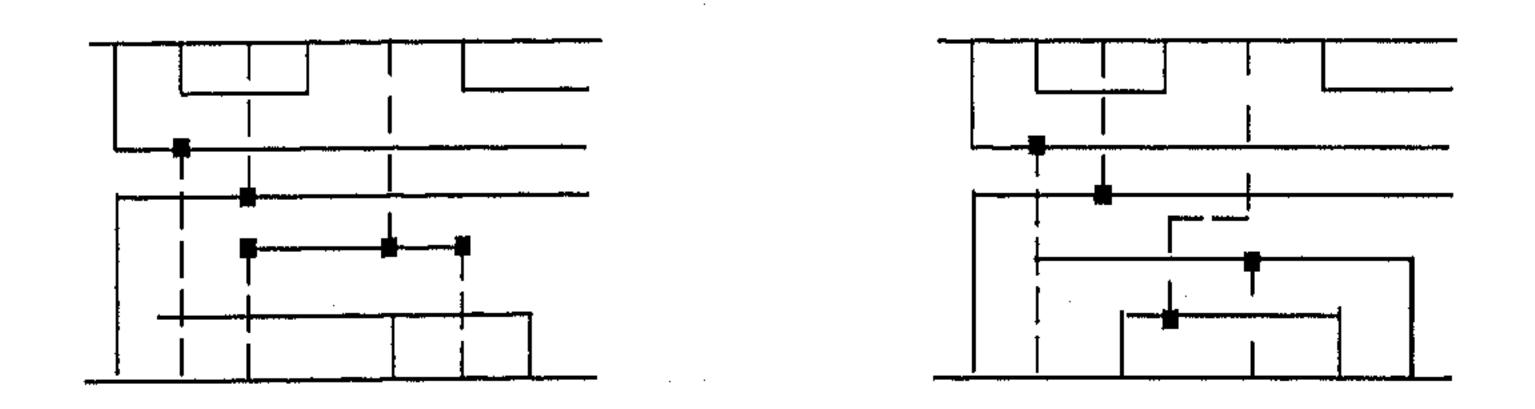

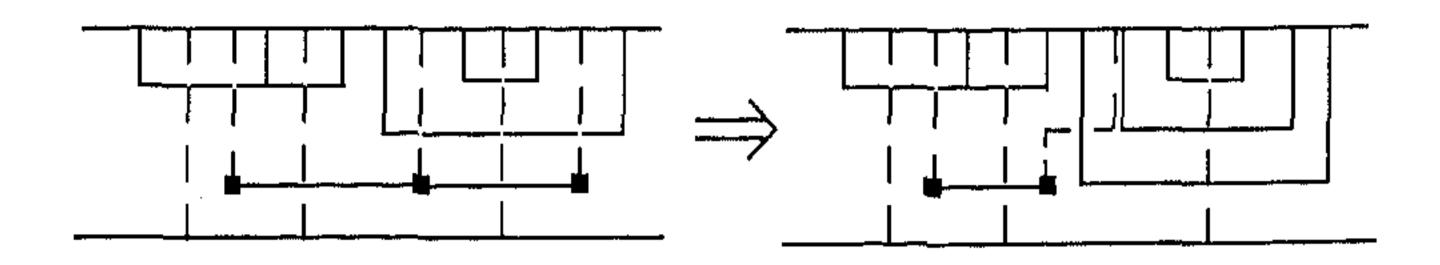

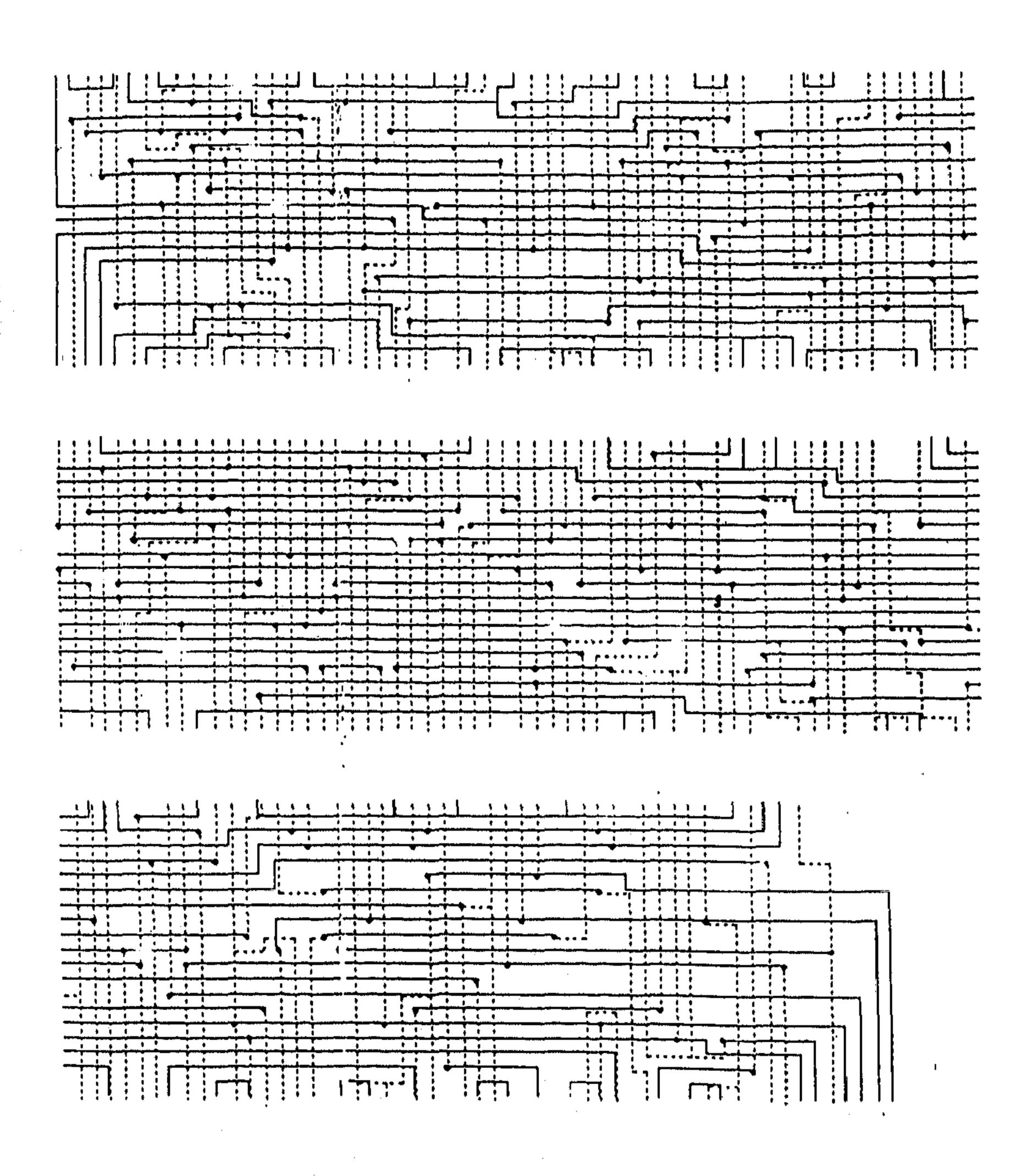

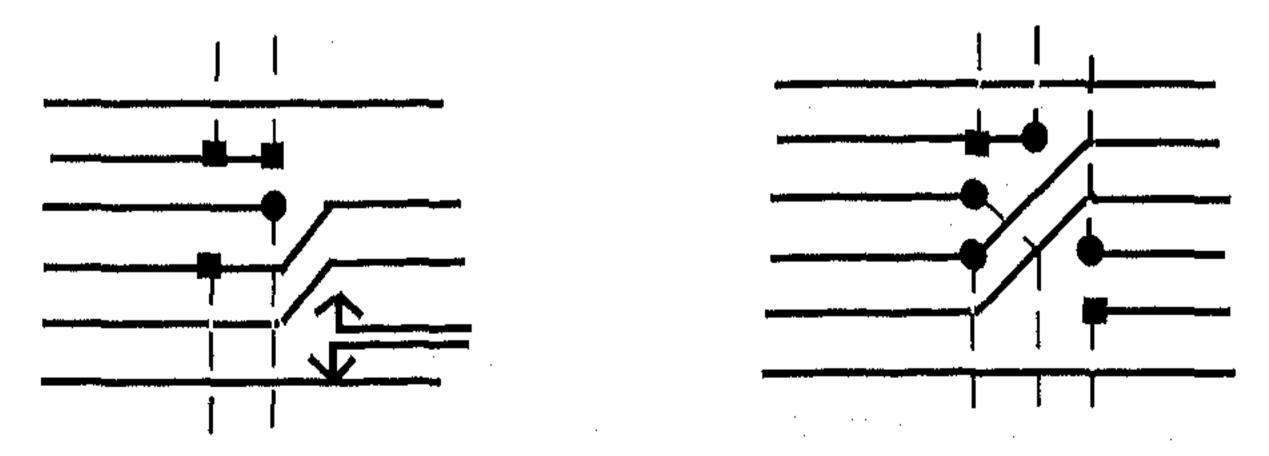

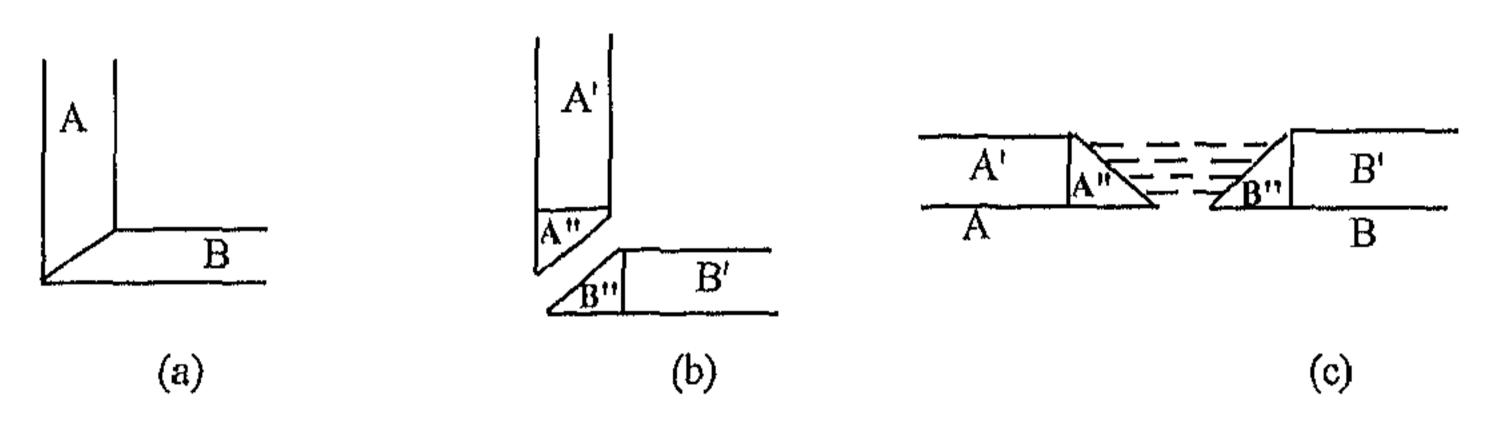

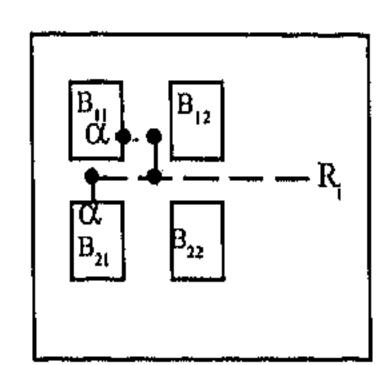

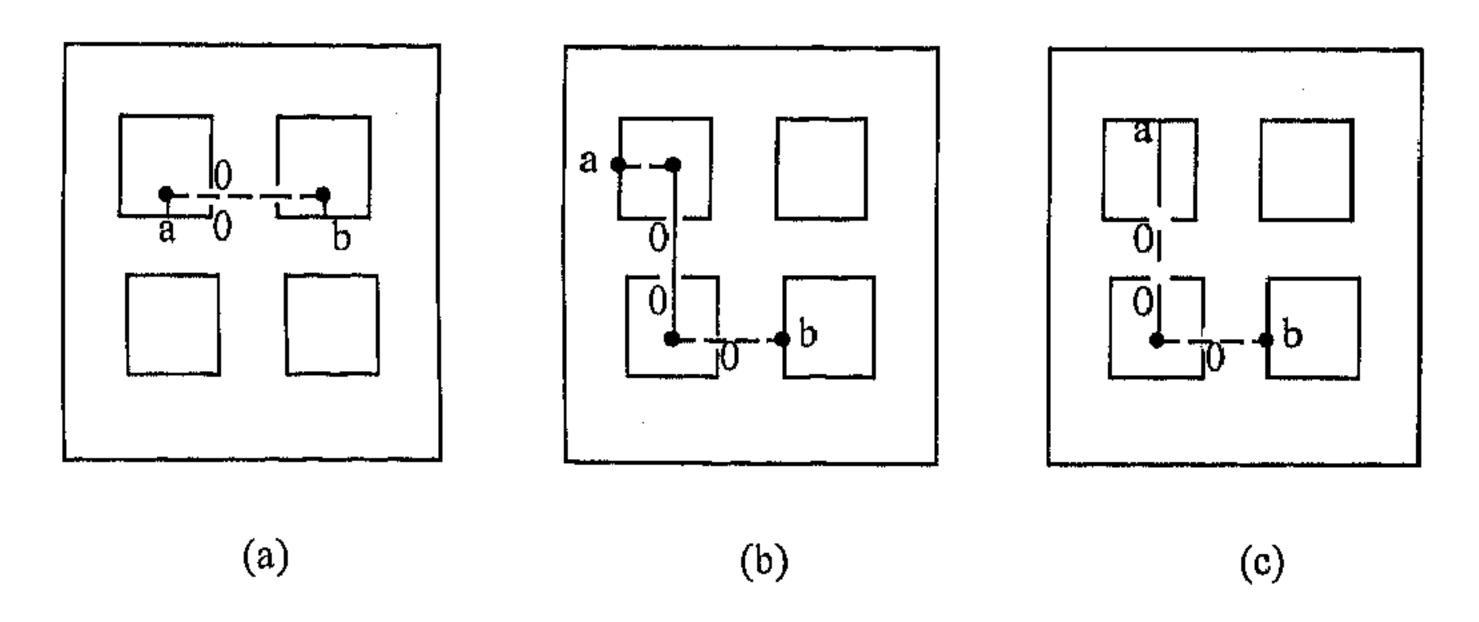

With the advent of two-and-half layer technology used in the layout design of standard cells, several channel routers use the extra routing area available outside the channel for interconnections. It is already mentioned that no cell is placed in the channel area in either region, and cells are placed in a single layer in the cell area. So, in a two layer model, the cell area in one layer remains unused. Reduction in layout area is only possible if the unused portion of the cell area is utilized during routing. Such routing methodology is referred to as *over-the-cell* routing in the literature. An example of over-the-cell routing is shown in Fig. 1.1.

In this context, the routing problem is to realize the interconnection of nets by means of paths, such that two paths of distinct nets are not allowed to intersect in the same layer. Terminals are accessible only at the edges of the cells. Given a netlist, the objective is to generate a routing with possible over-the-cell interconnections which minimizes the number of horizontal tracks inside the channel i.e., the channel width.

Over-the-cell channel routing problem is known to be NP-hard [S93]. The best known heuristic algorithms for over-the-cell channel routing appeared in [CL88, CPL90], which consist of three major phases in the following sequence: (i) selecting the net segments for routing over-the-cell, (ii) choosing terminals of the nets for routing within the channel and (iii) completion of routing through the channel.

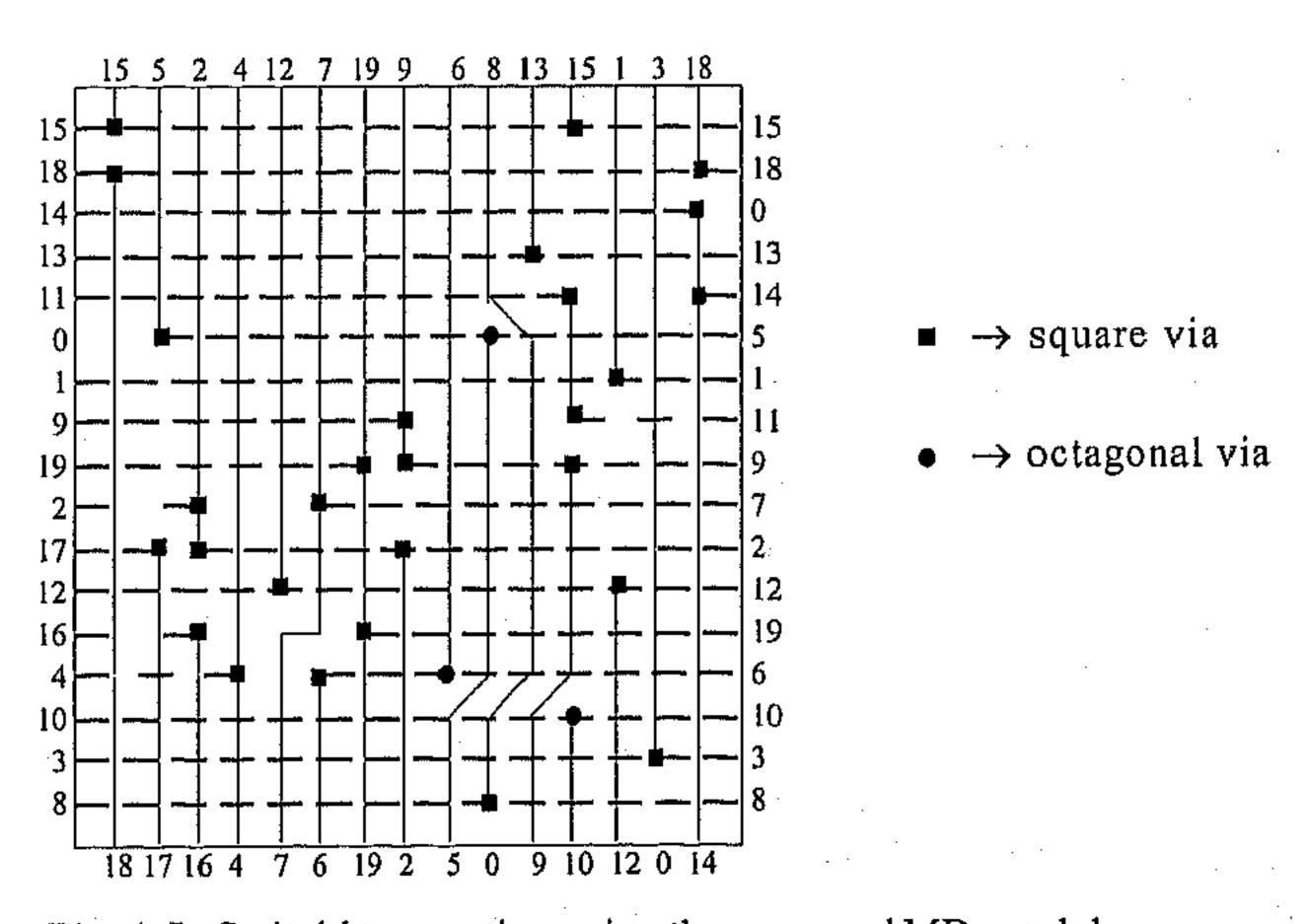

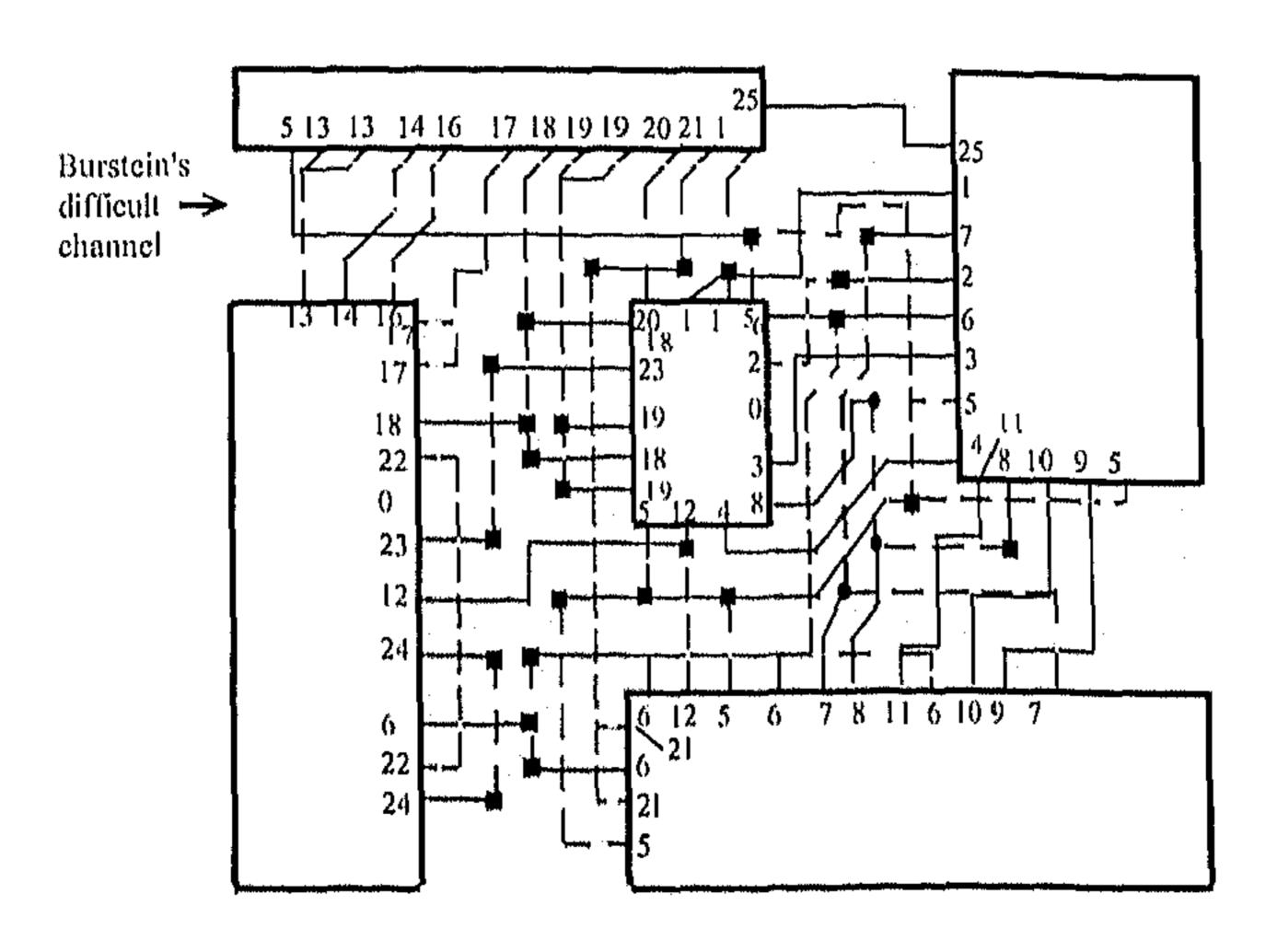

Fig. 1.1: An example of over-the-cell routing

It is easy to observe that the first two steps are highly interrelated. Routing a net over-the-cell may force some other nets to be routed within the cell through the heavily congested area. Thus, maximizing the number of over-the-cell candidates as suggested in [CL88] may not lead to a good solution. In our work [DNB91], we have described a new heuristic algorithm which iteratively selects potential over-the-cell nets with an ultimate objective of minimizing channel width. Experimental evidence shows considerable improvement over earlier results [CL88] in the number of tracks used both inside the channel, and over the cell.

#### 1.2.1.2 Via minimization

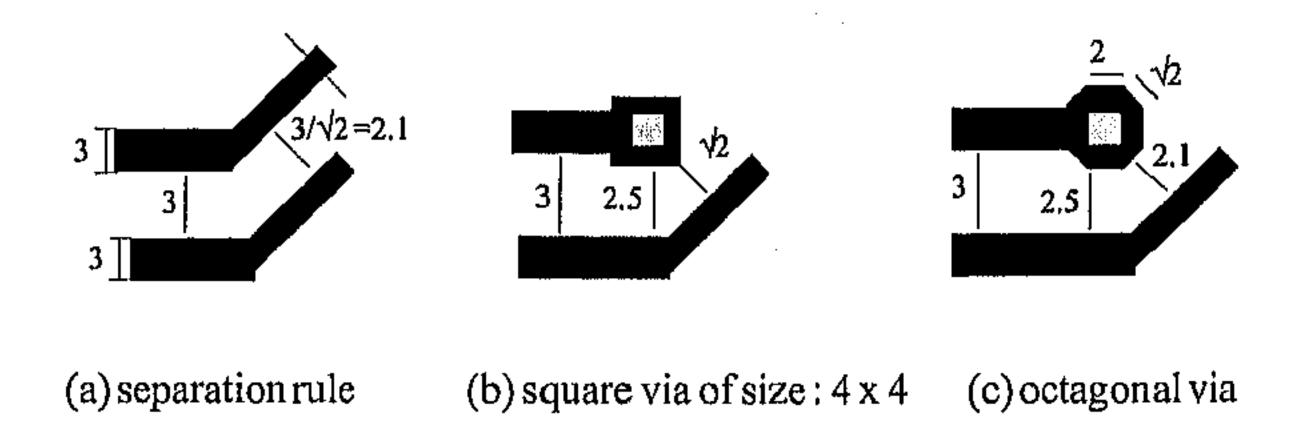

In channel routing, each signal net is formed by the wire segments interconnecting a set of electrically connected terminals. If multiple conducting layers are available for interconnection, the wires of the same net lying in different layers are connected through vias (contact holes). In reserved layer model using two layers, all horizontal wire segments are placed on one layer, and all vertical wire segments are assigned to the other layer. However, this method tends to generate a large number of vias in the final routing solution. The presence of too many via holes may cause certain disadvantages, e.g.,

- (i) besides increasing the manufacturing cost and complexity, vias in a circuit degrade its performance and reliability, and

- (ii) vias require more layout area. In a compactible channel routing, the nMOS design rule requires  $3\lambda$  spacing for path width,  $3\lambda$  for feature separation, whereas,  $(4\lambda \times 4\lambda)$  square area for a via hole in metal layers.

Thus, minimization of via holes leads to considerable improvement in VLSI layout design in terms of chip area, circuit performance and cost [H83]. This is even true if a short run of metal is replaced by polysilicon because the capacitance and resistance of the contact are likely to be greater than those of added polysilicon [CD88].

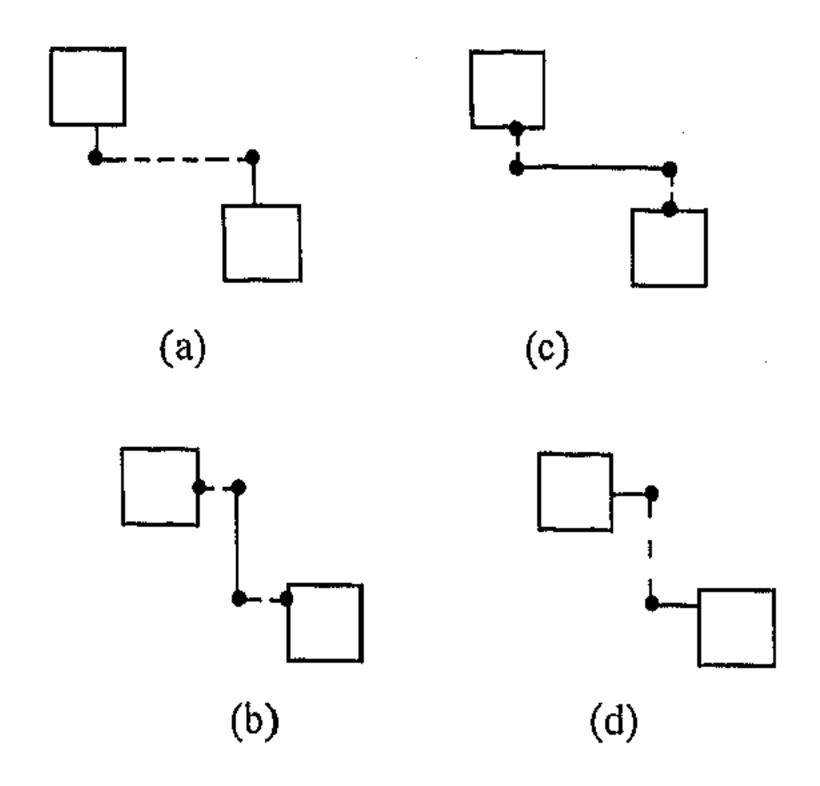

The existing methods for via minimization are classified into two general categories:

- (i) unconstrained via minimization (UVM);

- (ii) constrained via minimization (CVM).

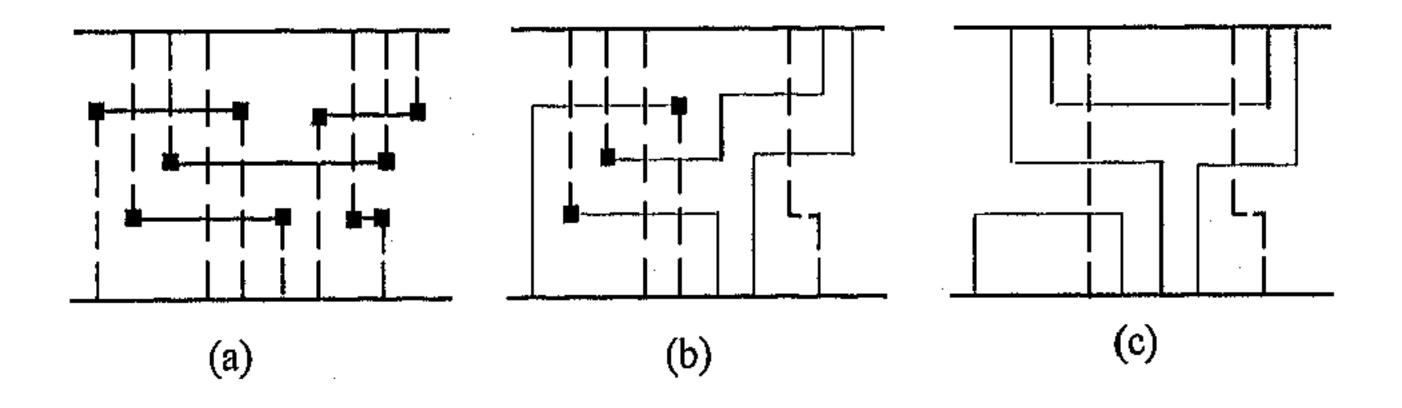

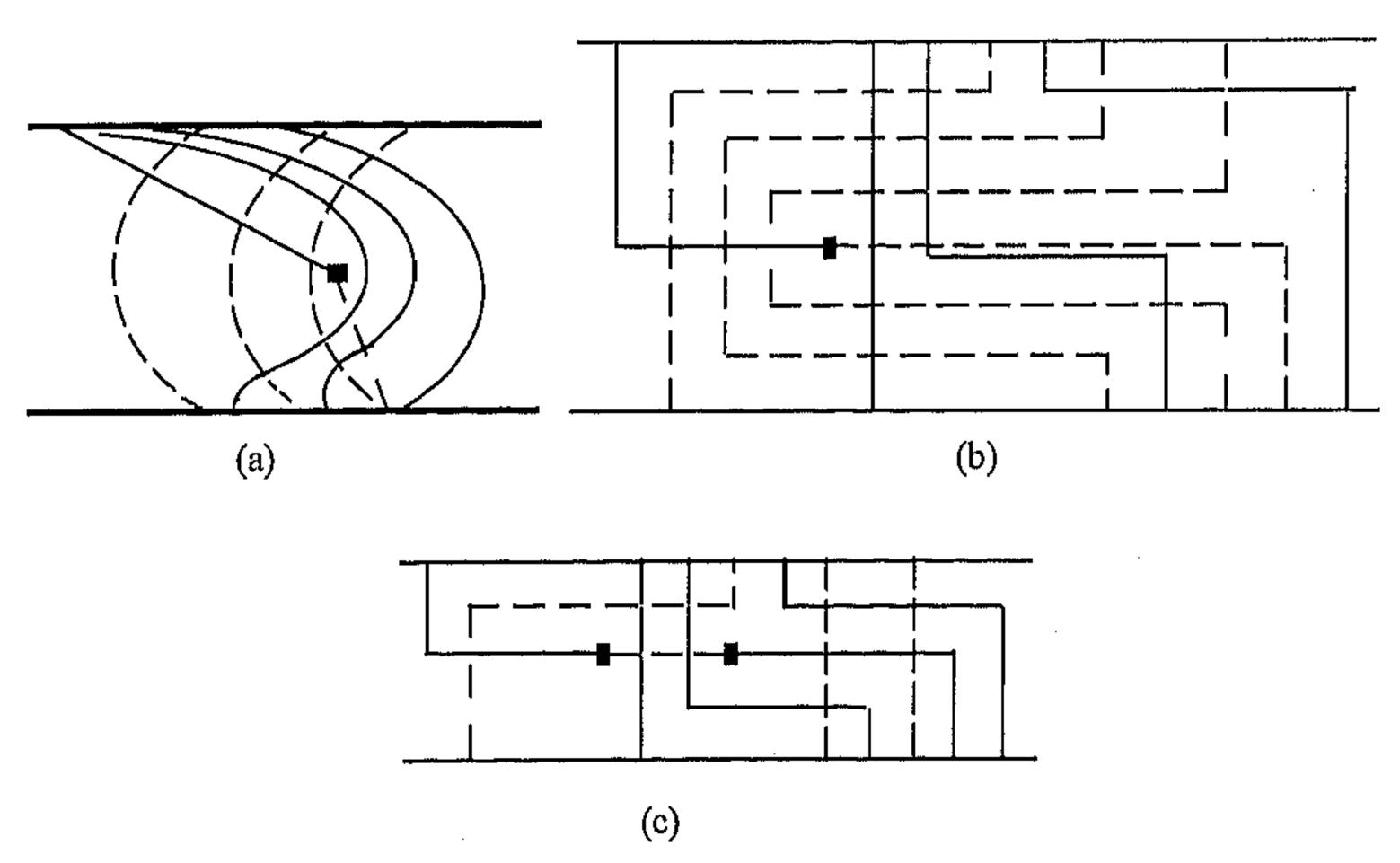

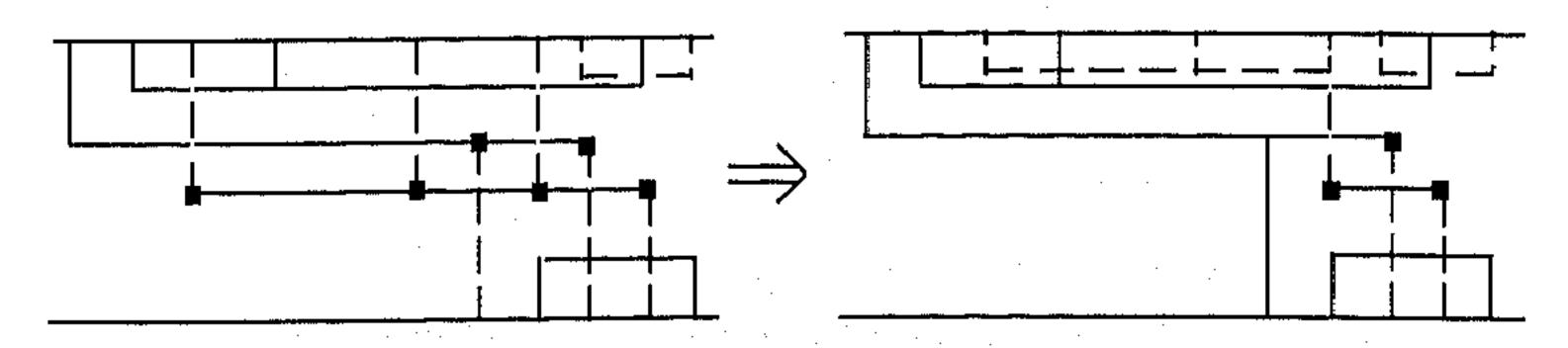

Although in most cases, UVM produces a solution with fewer vias, the layout area

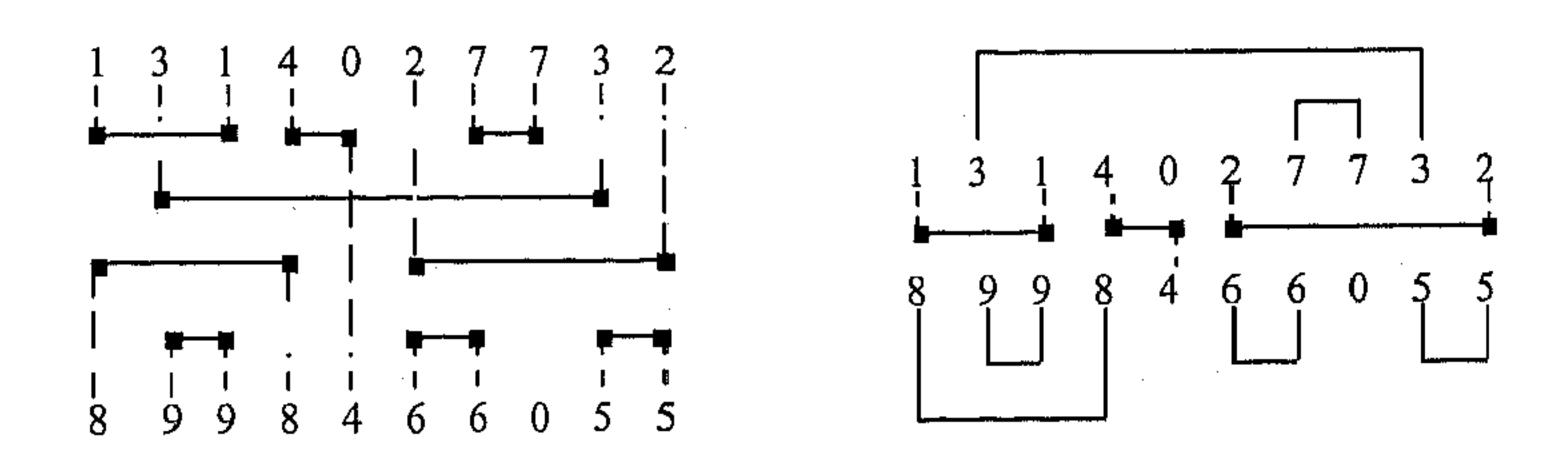

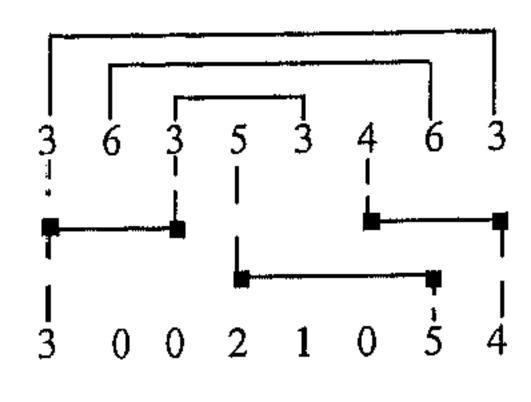

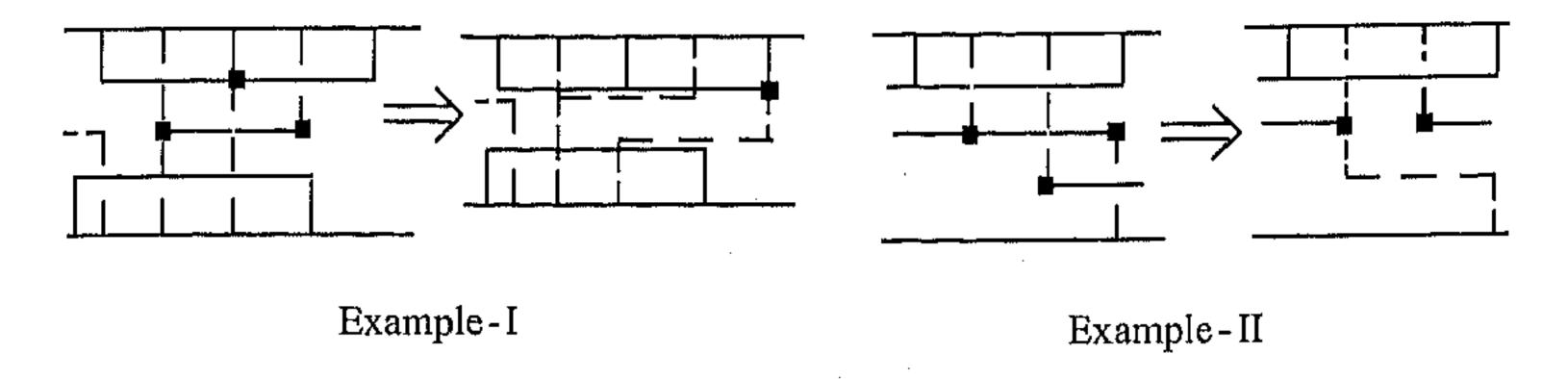

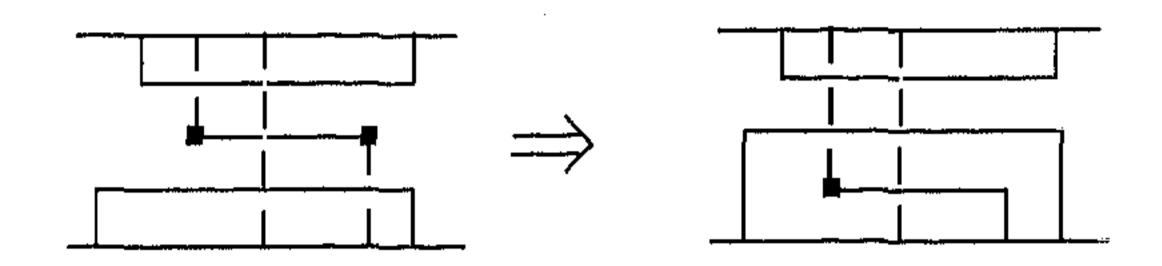

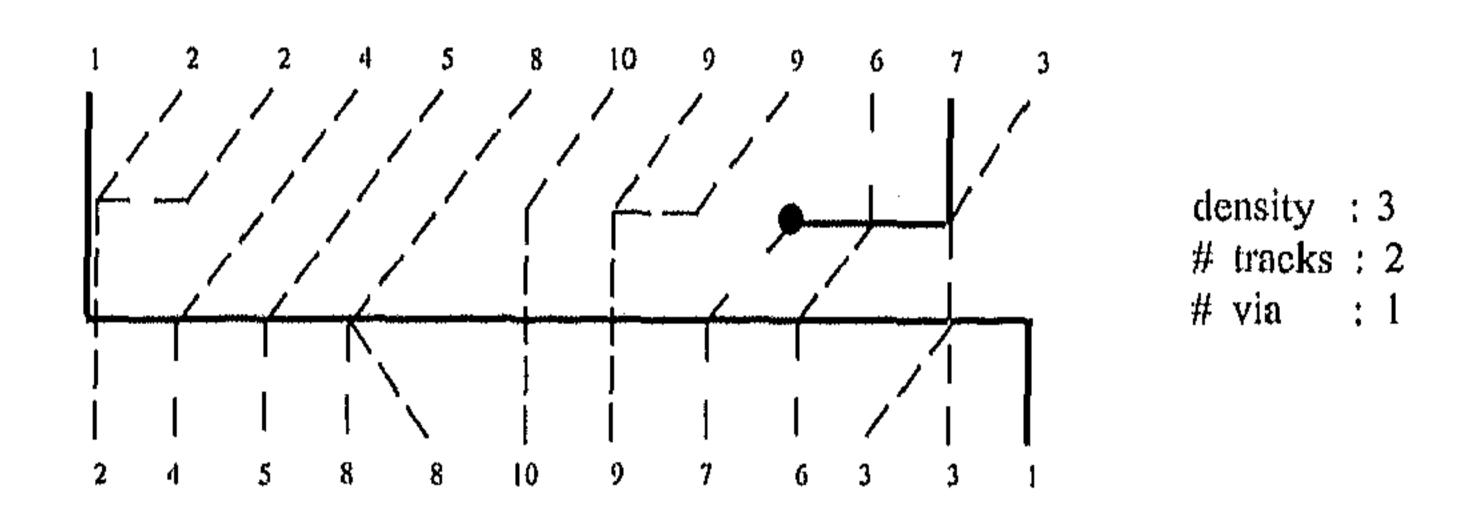

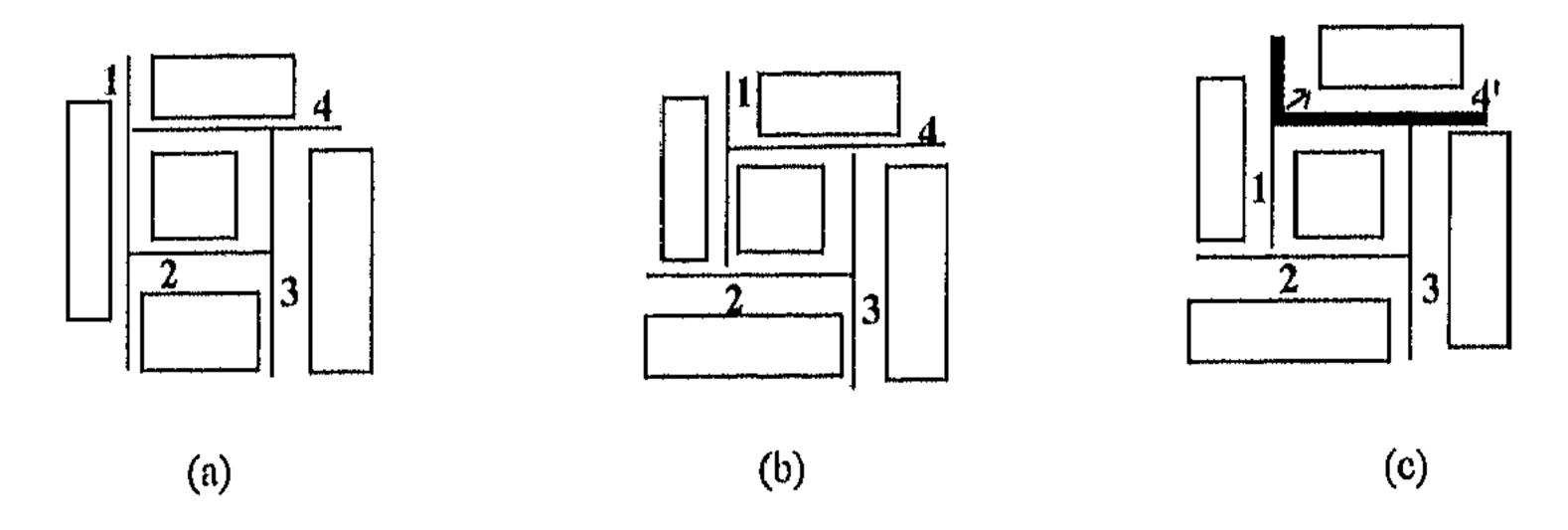

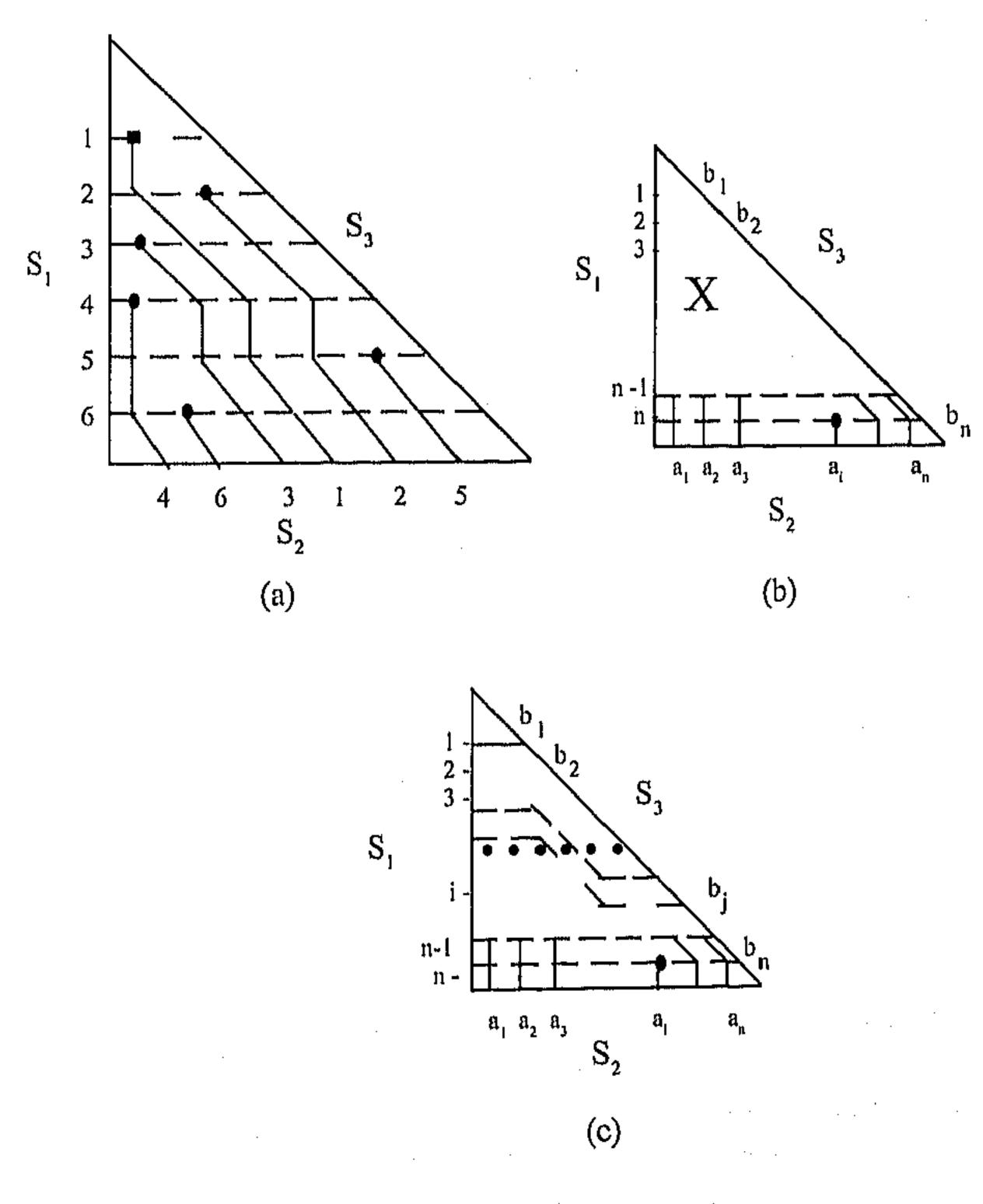

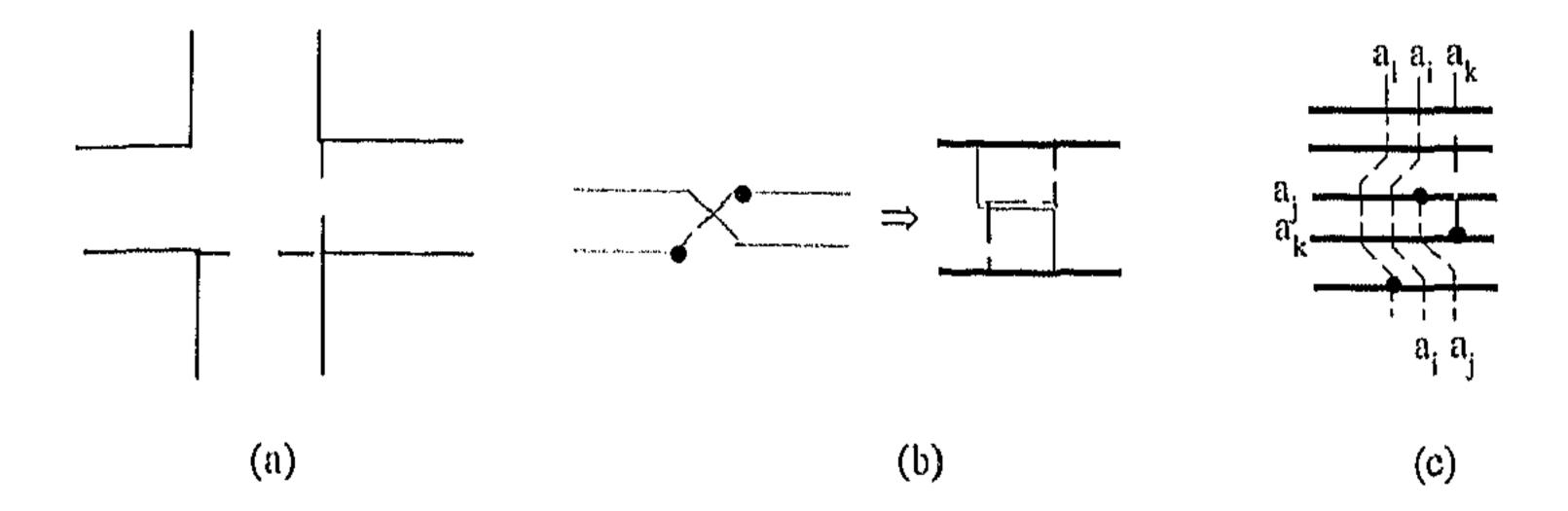

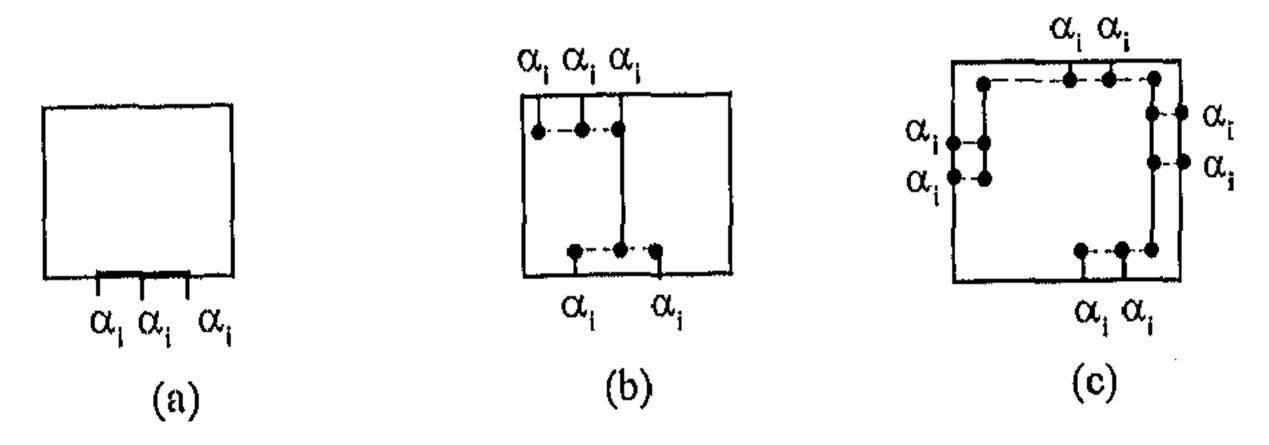

Fig. 1.2: Routing solution of a channel

- (a) before via minimization (# via = 10),

- (b) after via minimization using [TWC91] (# via = 3), and

- (c) another solution with no via

is not compact. An example of a channel, routed without via-minimization, is shown in Fig. 1.2(a). The layout obtained by via minimization algorithm of [TWC91] is shown in Fig. 1.2(b). Further via minimization may be possible with some clever heuristic as demonstrated in Fig. 1.2(c).

An approach to the via minimization technique was first proposed in [L61] based on layout modification followed by maze routing. In the unreserved layer model, via minimization problem is solved in [TWC91]. In this thesis, we have reported a new approach for via minimization [DB93] using the advantages of both CVM and layout modification. Our algorithm outperforms the result (in terms of the number of vias) of [TWC91] for all standard benchmarks without increasing the routing area. For Deutsch's difficult example, we obtained only 190 vias with 19 tracks, which is, to the best of our knowledge, the fewest ever reported. The total wire length also decreases in almost all the cases compared to the solutions of [TWC91].

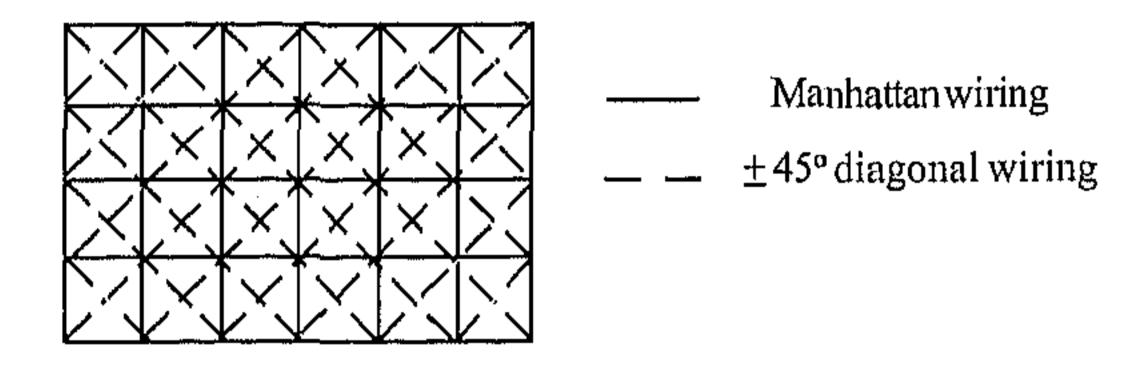

#### 1.2.2 Channel routing in Manhattan-diagonal model

The conventional channel routing algorithms, studied for the last two decades assume horizontal and vertical wire segments for interconnection. Recently, efforts have been made to develop algorithms using non-manhattan geometries. A diagonal model with  $\pm 45^{\circ}$  wires was reported in [LLP89a]. Routing in time square model using  $\pm 60^{\circ}$  wires was considered in [LLP90]. A channel router using both rectilinear and diagonal ( $\pm 45^{\circ}$ ) wire segments was proposed in [CR91, CHS94]. The diagonal model is well supported by the fabrication process and provides better utilization of routing space. It also tends to reduce wire length and hence area and delay. However, the existing algorithms based on this model are either too elementary or inefficient, and therefore, have limited applicability to real life routing problems.

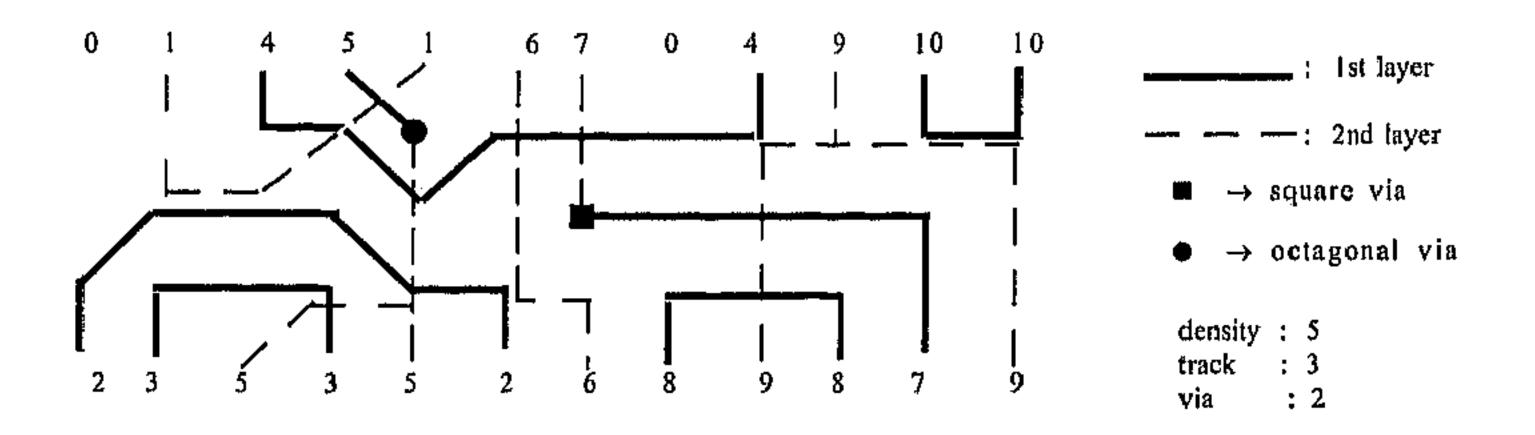

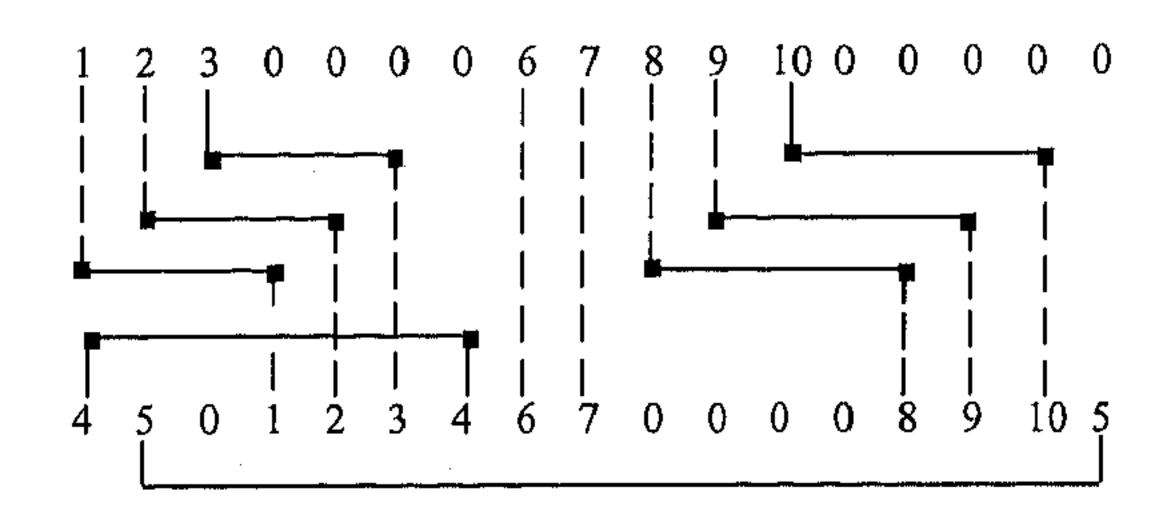

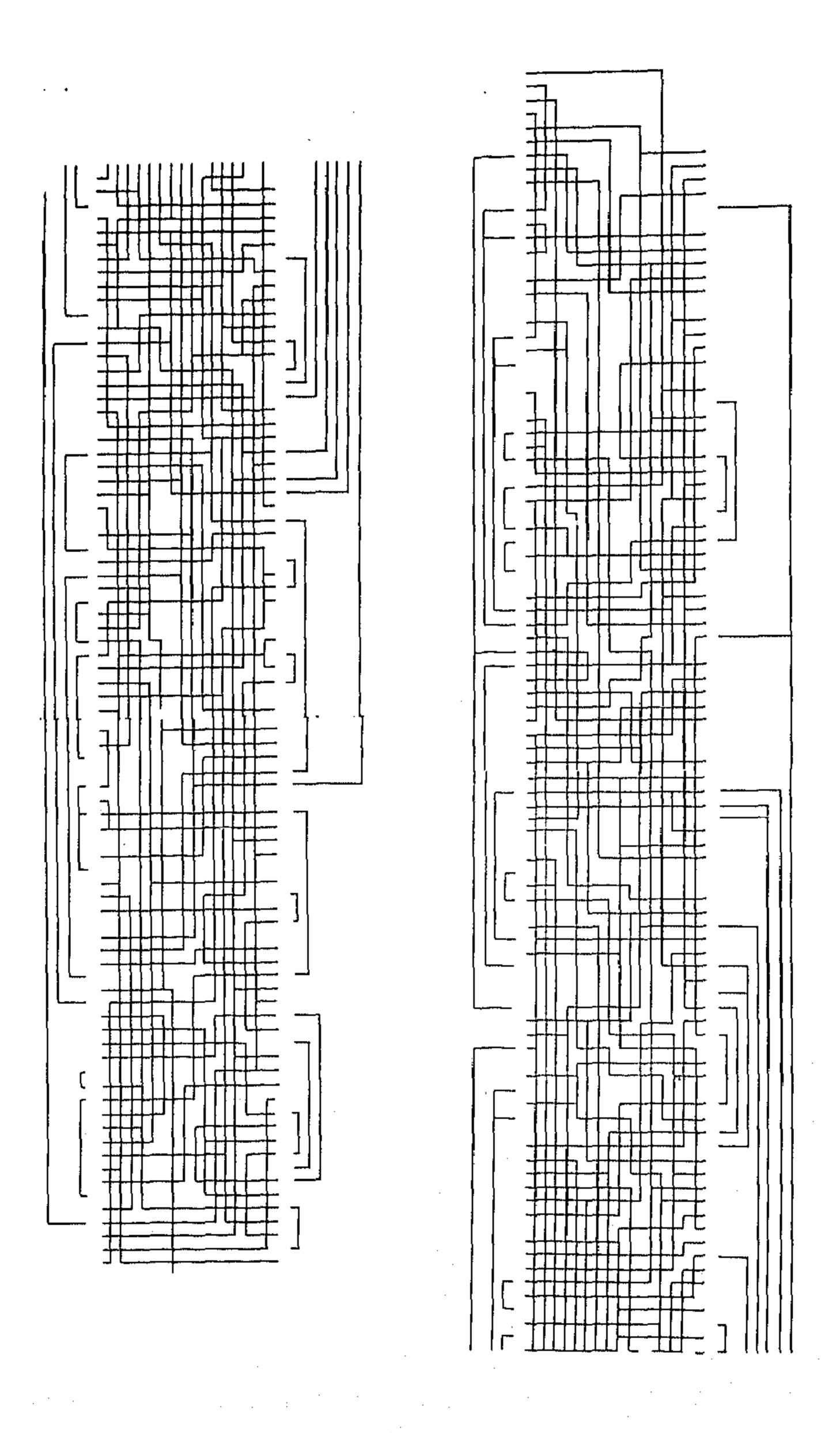

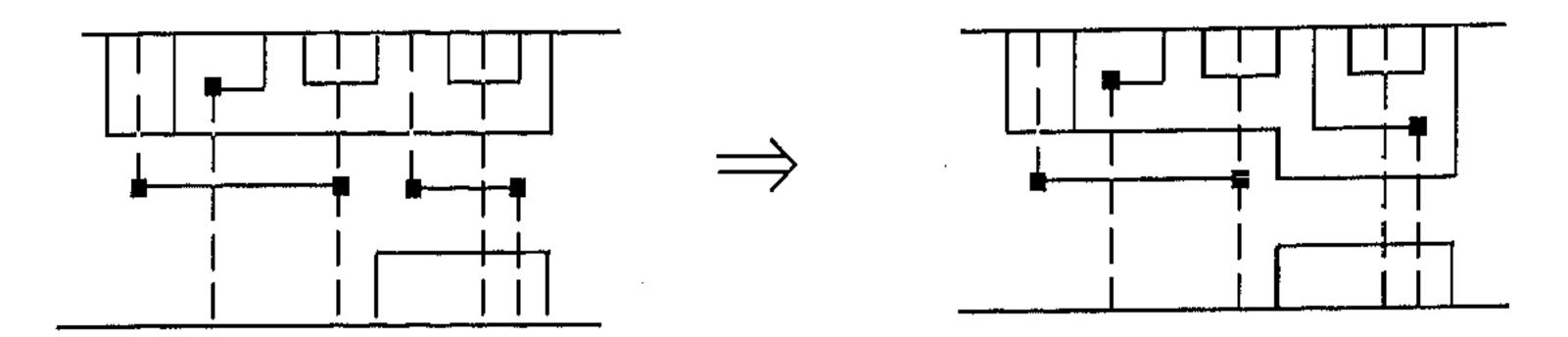

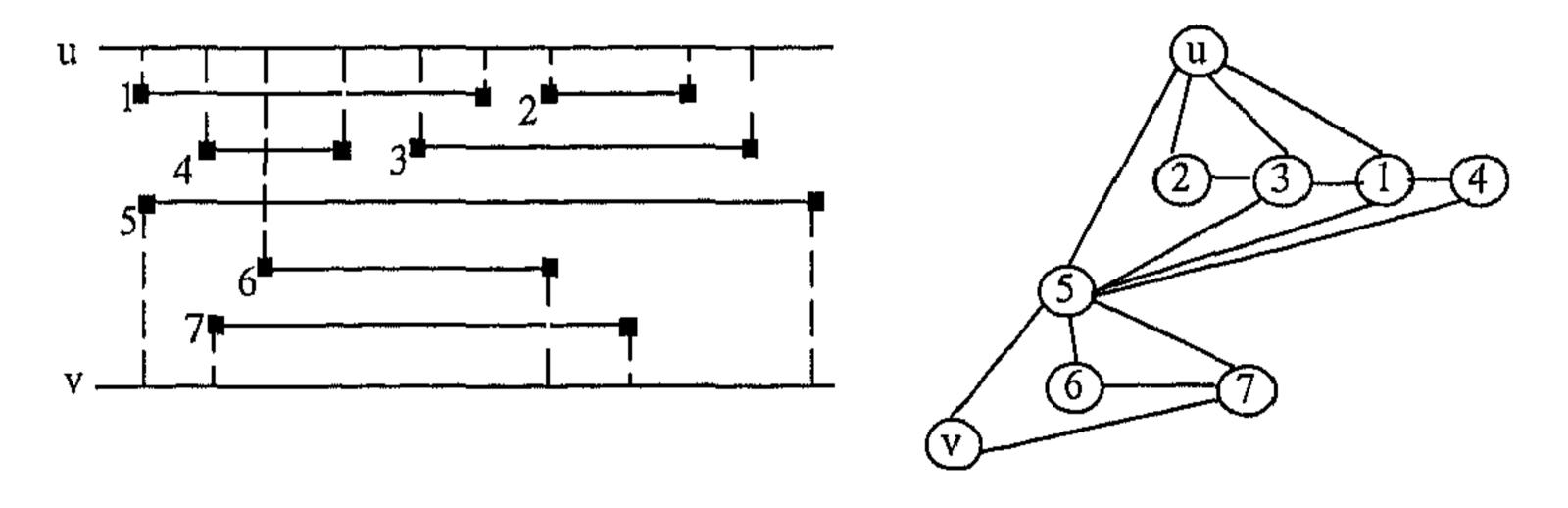

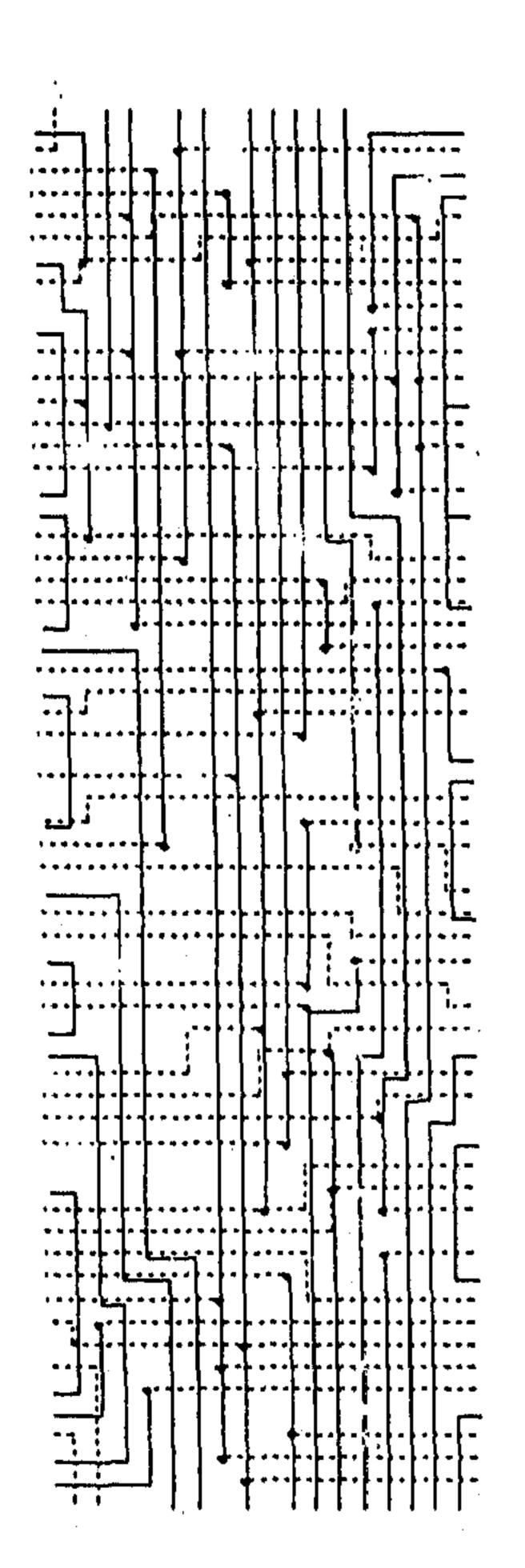

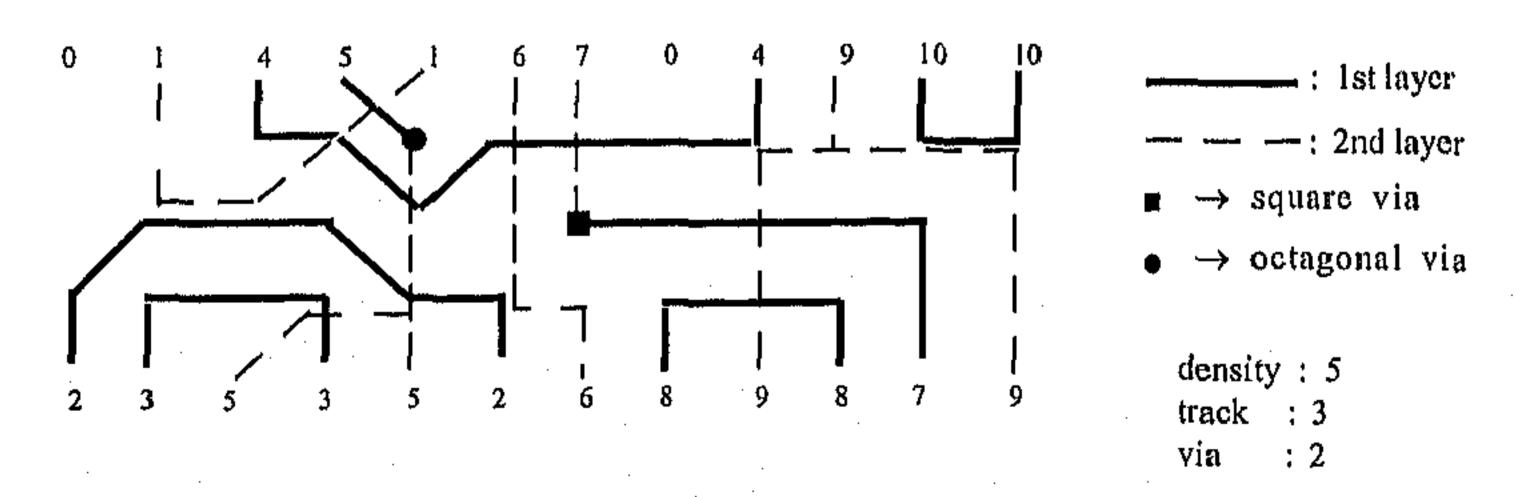

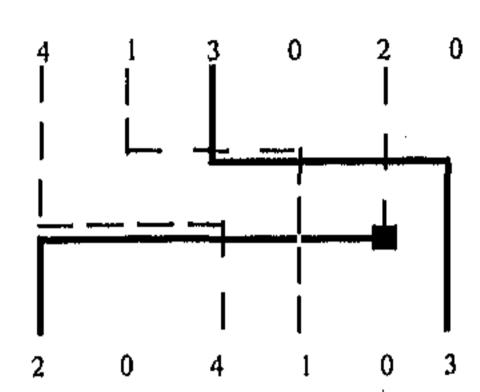

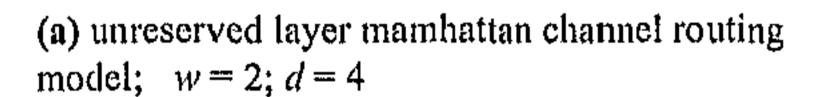

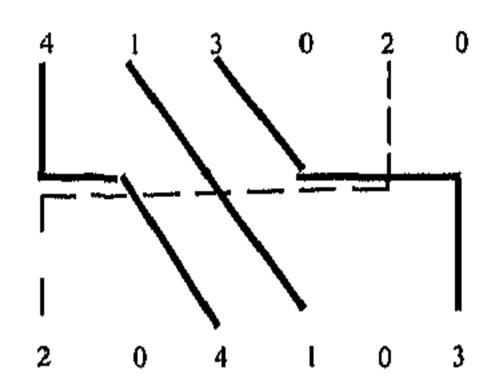

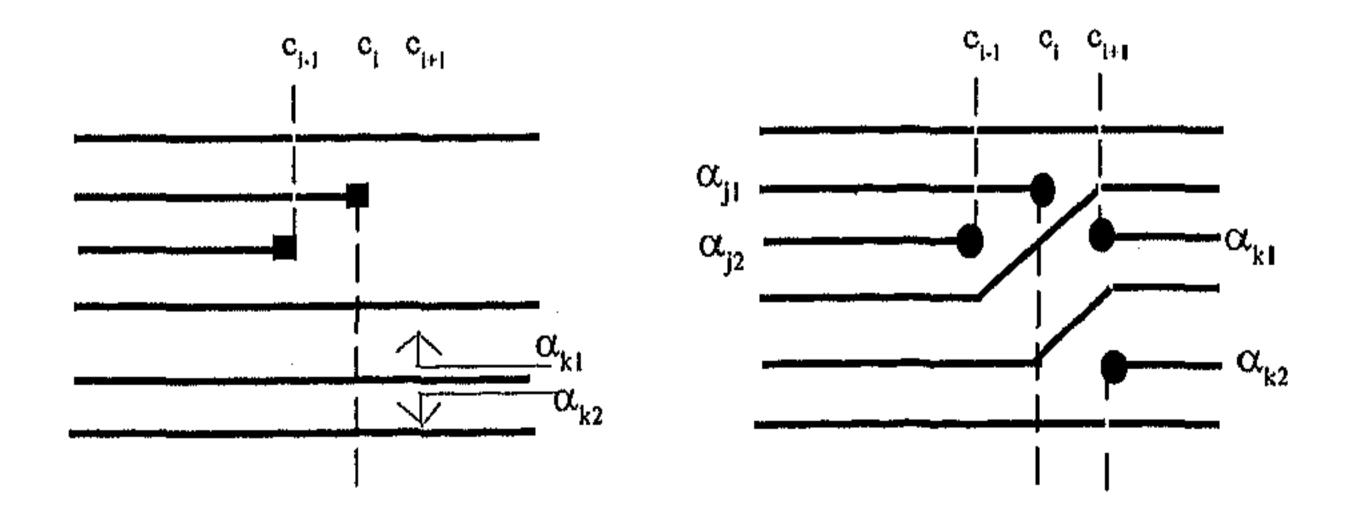

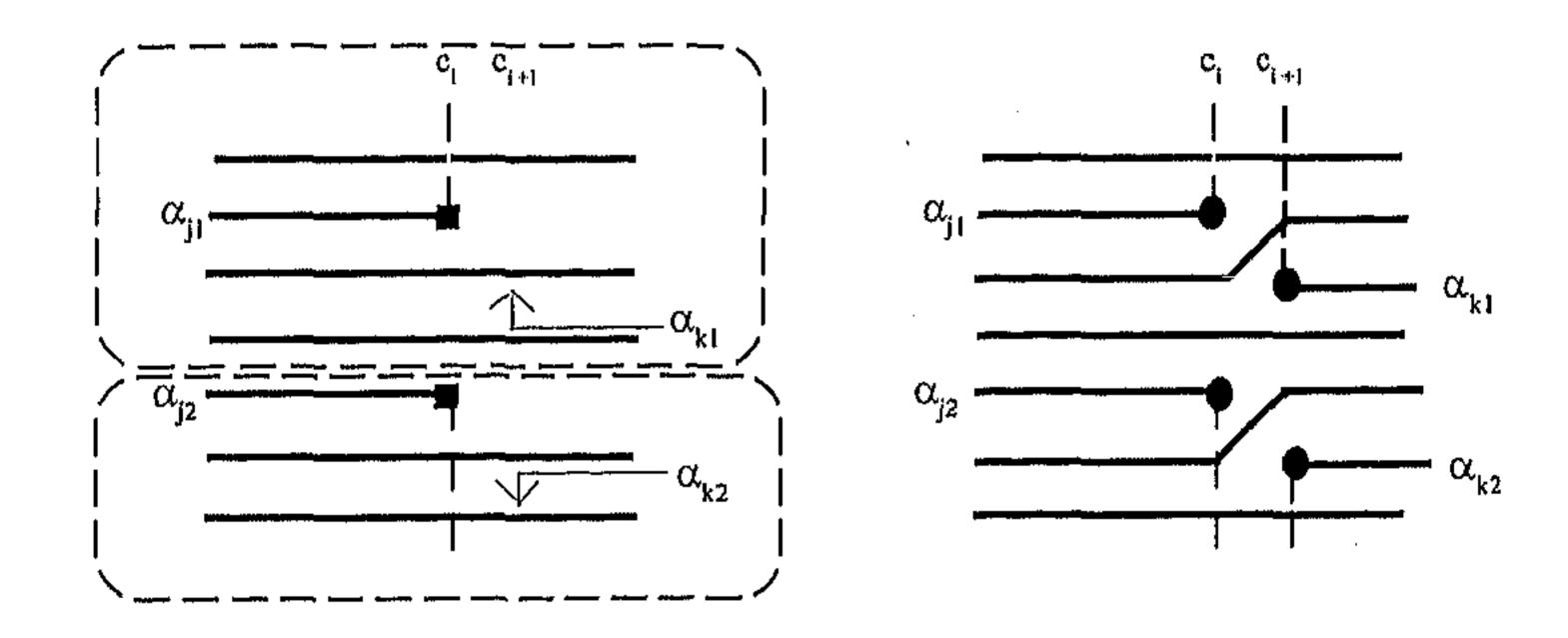

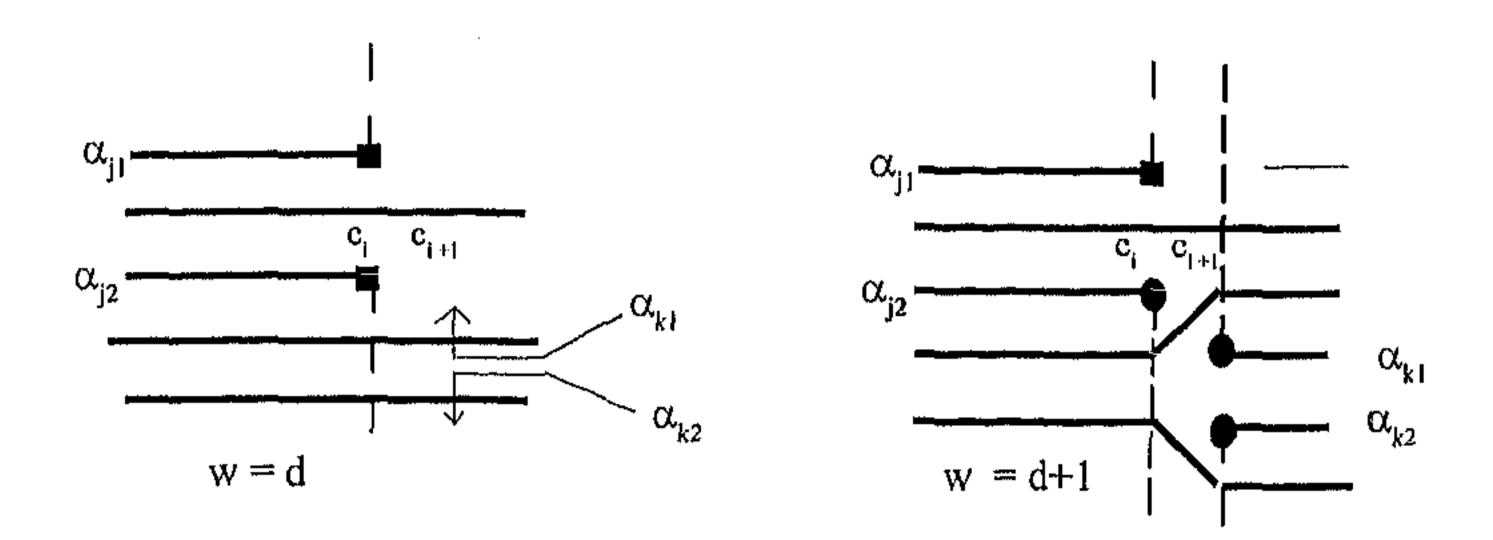

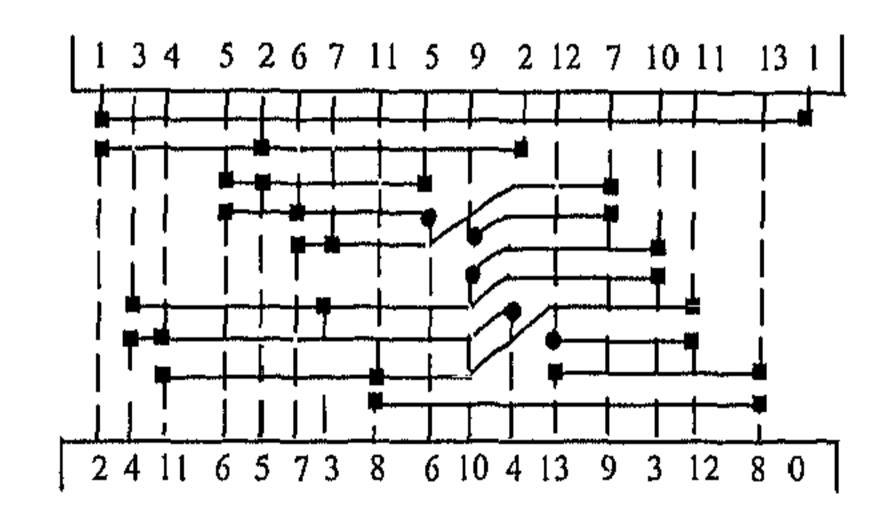

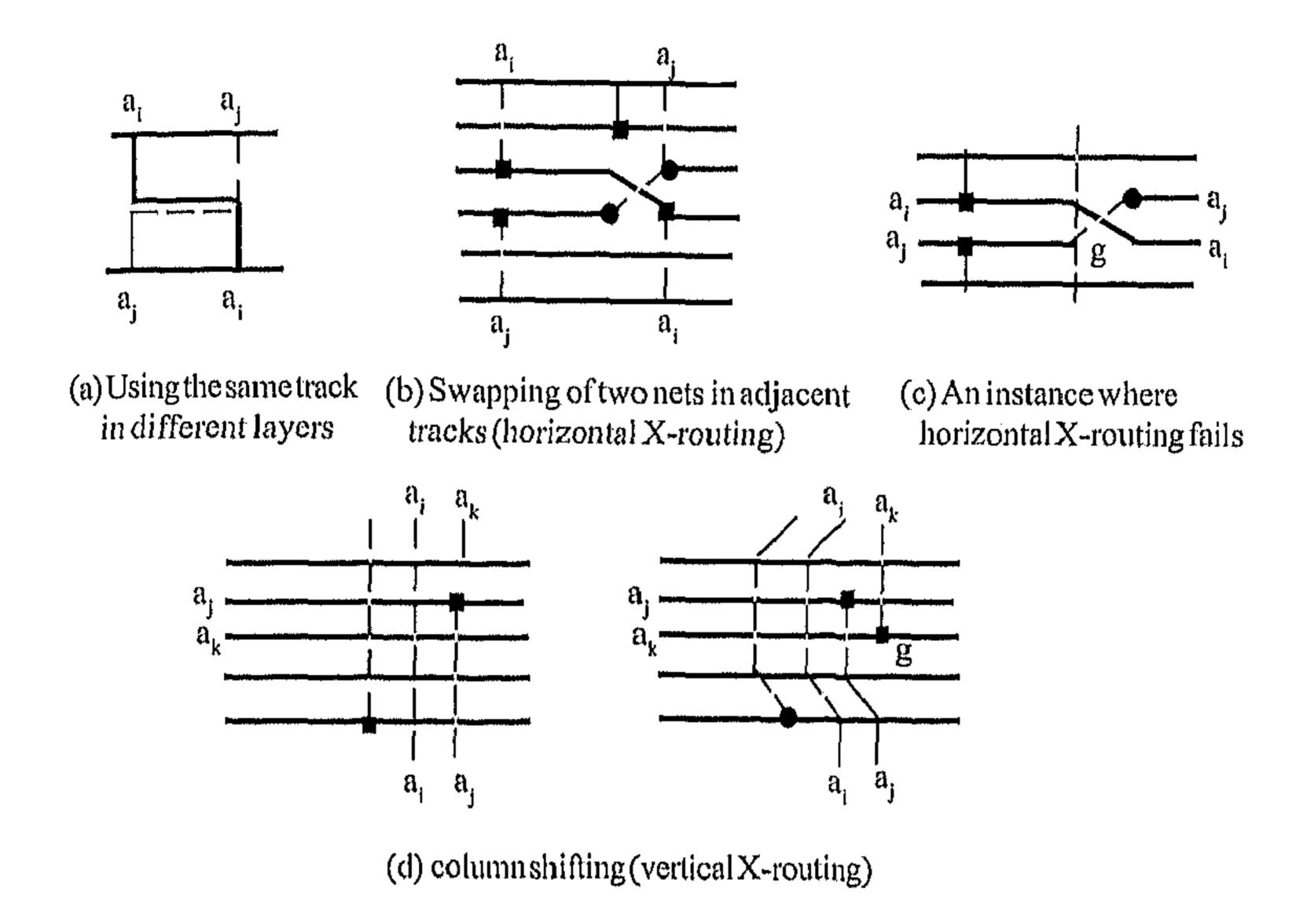

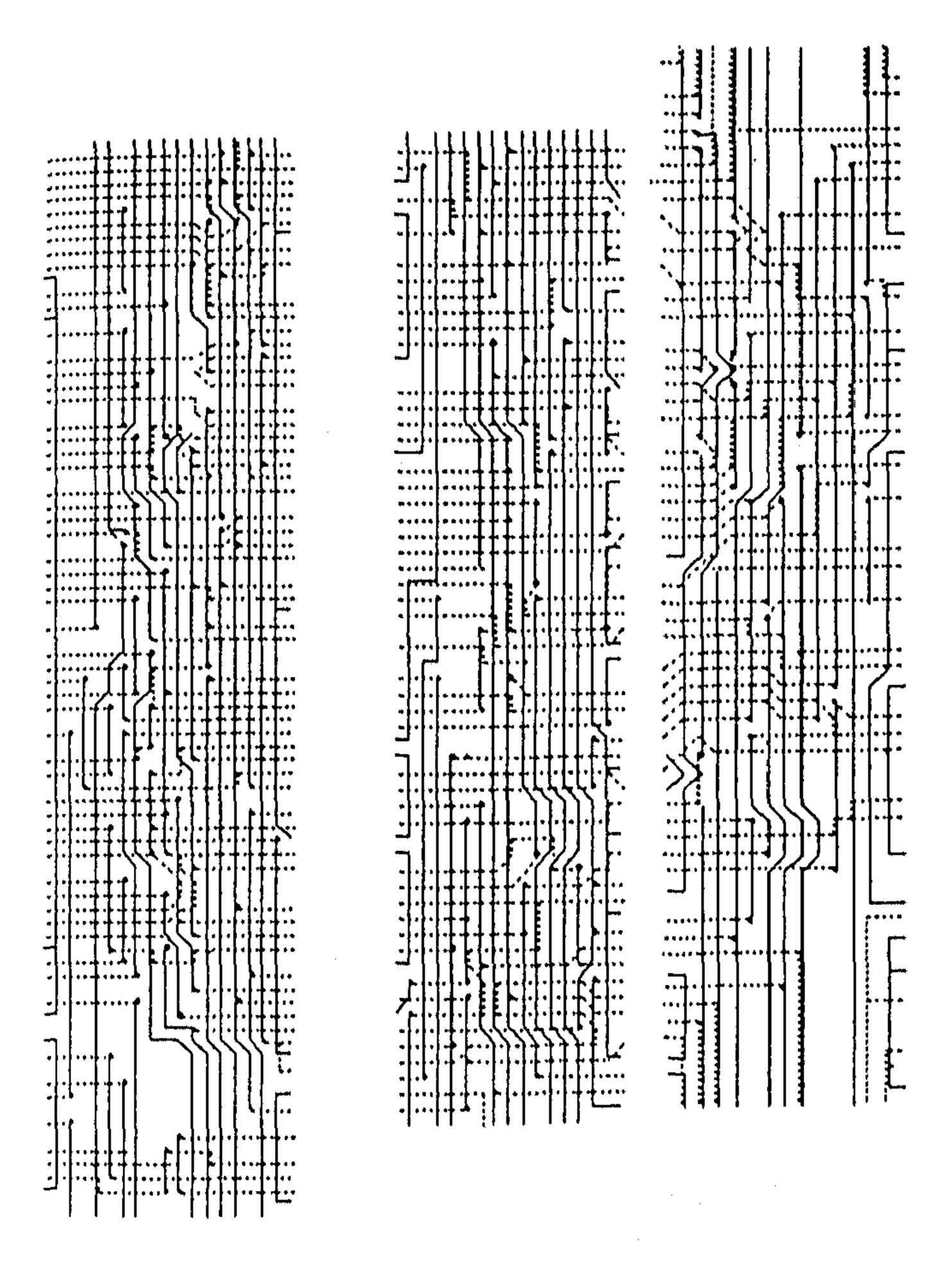

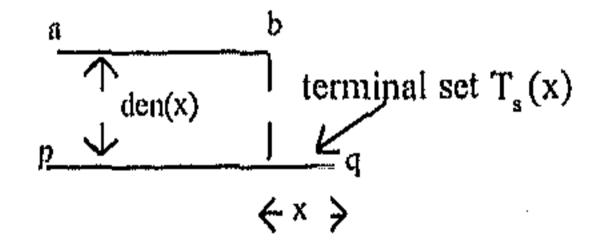

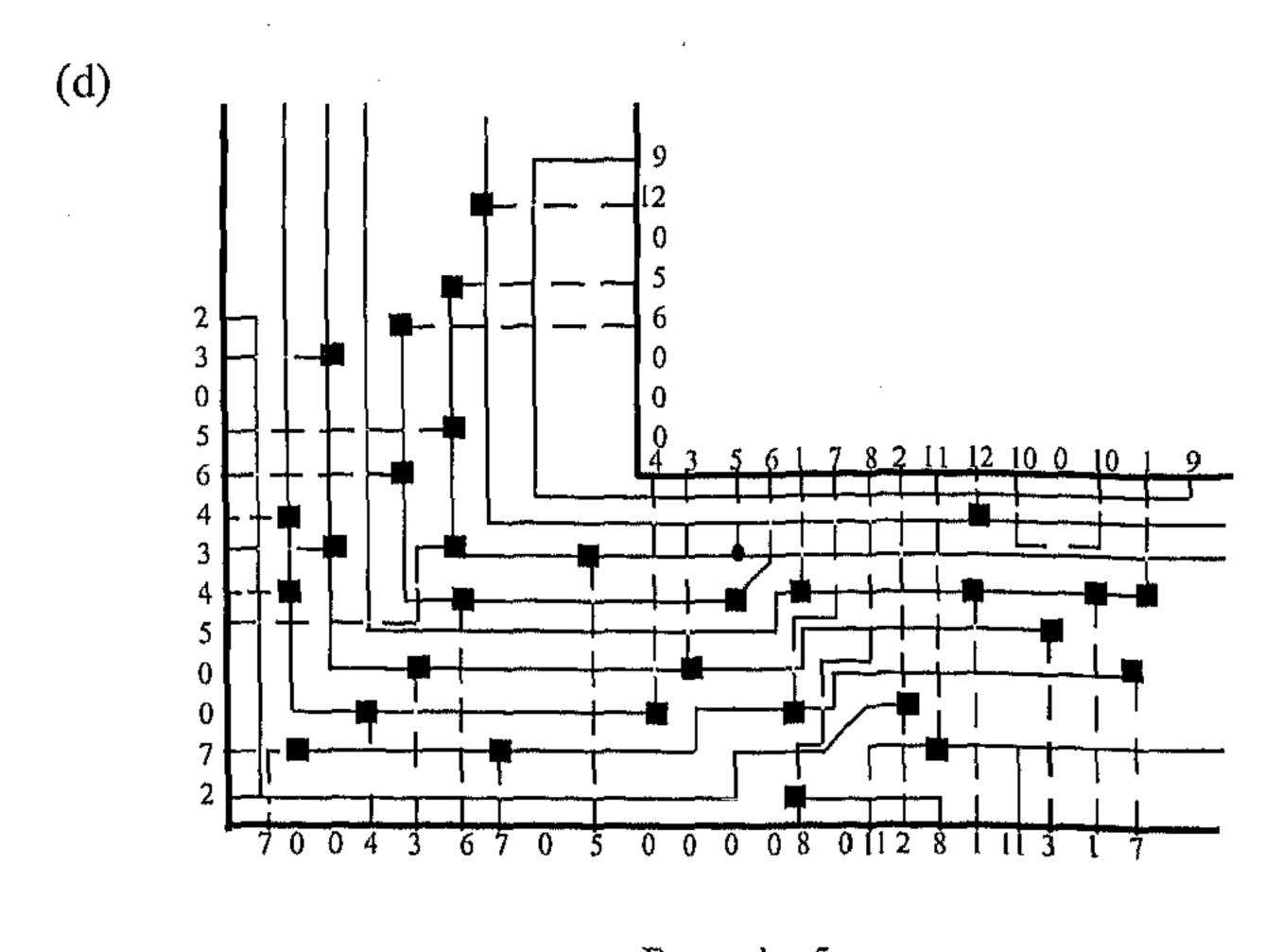

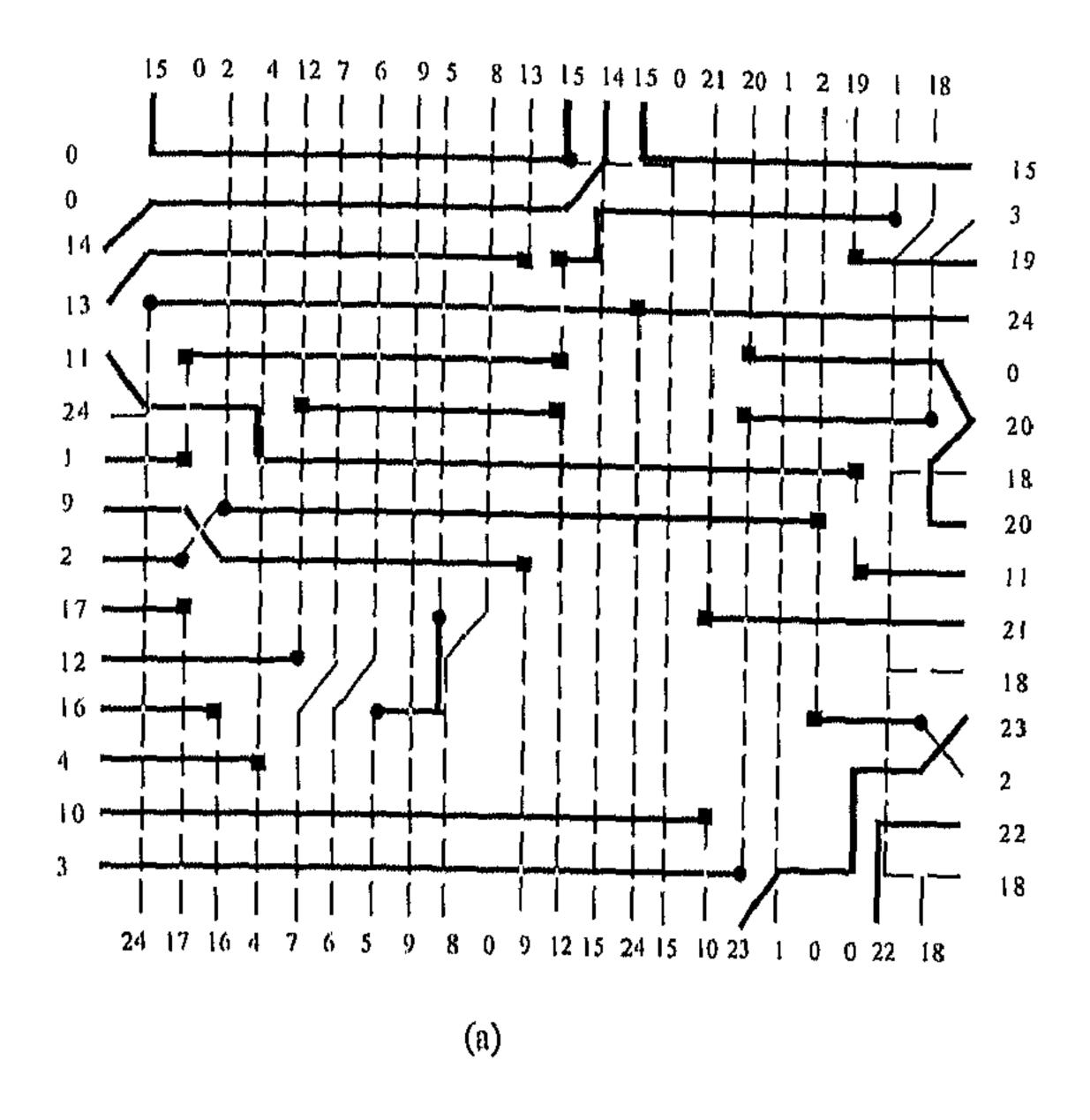

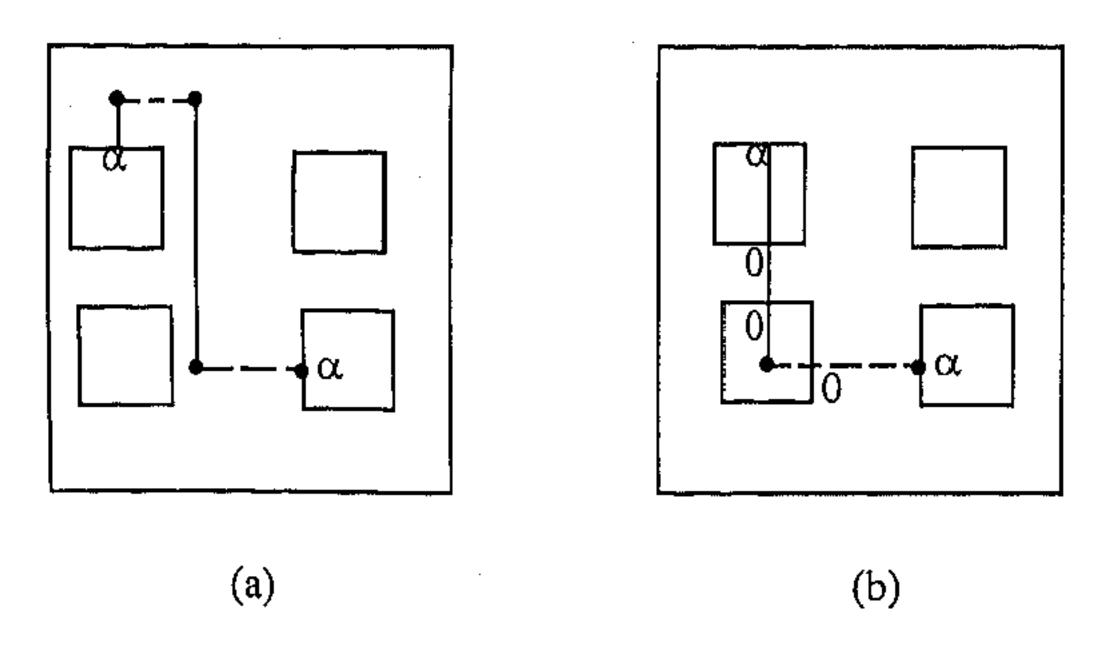

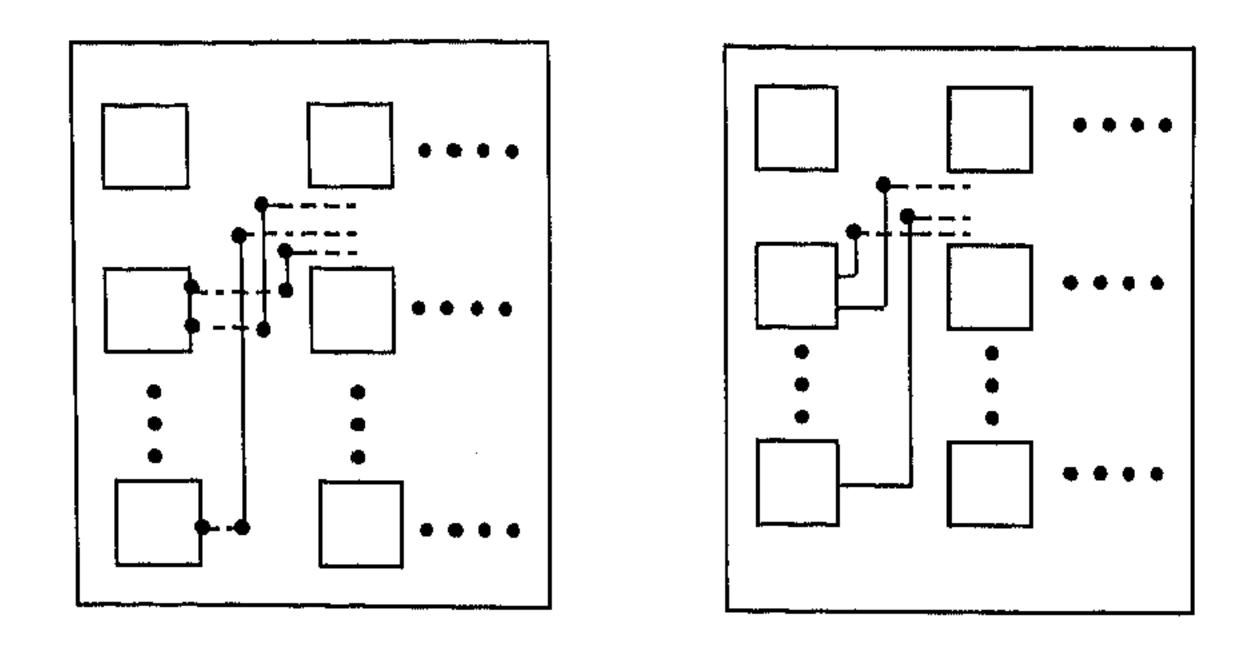

In this thesis, we propose a new approach to channel routing that combines the advantage of both diagonal model and manhattan geometry. We consider two routing layers; the terminals reside along the channel boundary are fixed, and the routing wires are assumed to be of manhattan-diagonal  $(\pm 45^{\circ})$  model (MD-model). First, we consider the reserved layer model (i.e., horizontal and diagonal wire segments are in one layer and vertical wire segments are in other layer), and present a simple O(l.d) time algorithm that routes an arbitrary channel with no cyclic vertical constraints in w tracks, where l is the length of the channel, d is the channel density, and  $d \le w \le (d+1)$ . Next, we describe an output-sensitive algorithm using unreserved layer manhattan-diagonal model, that can route two-layer channels with cyclic vertical constraints using w tracks, in O(l.w) time (i.e., linear in area of the channel). An illustration of our model is given in Fig. 1.3.

Fig. 1.3: Channel routing in unreserved layer MD model

Our proposed algorithm outperforms the methods in [YK82, HIZ91, CR91] both in execution time and in quality of solutions. Experimental results on benchmark examples show very encouraging results. It is also observed that the number of vias used and the wire length is significantly less compared to the via minimizer of [TWC91]. To the best of our knowledge, this work is the first reporting of routing in the MD-model.

#### 1.2.3 L-shaped channels, staircases and switchboxes

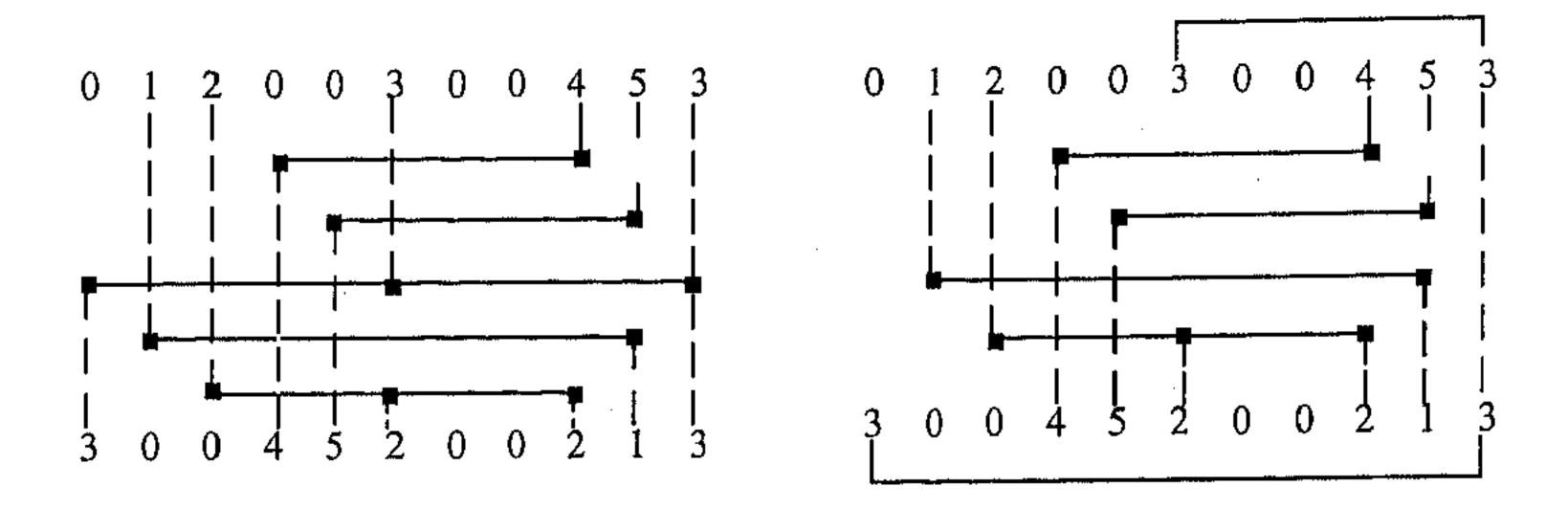

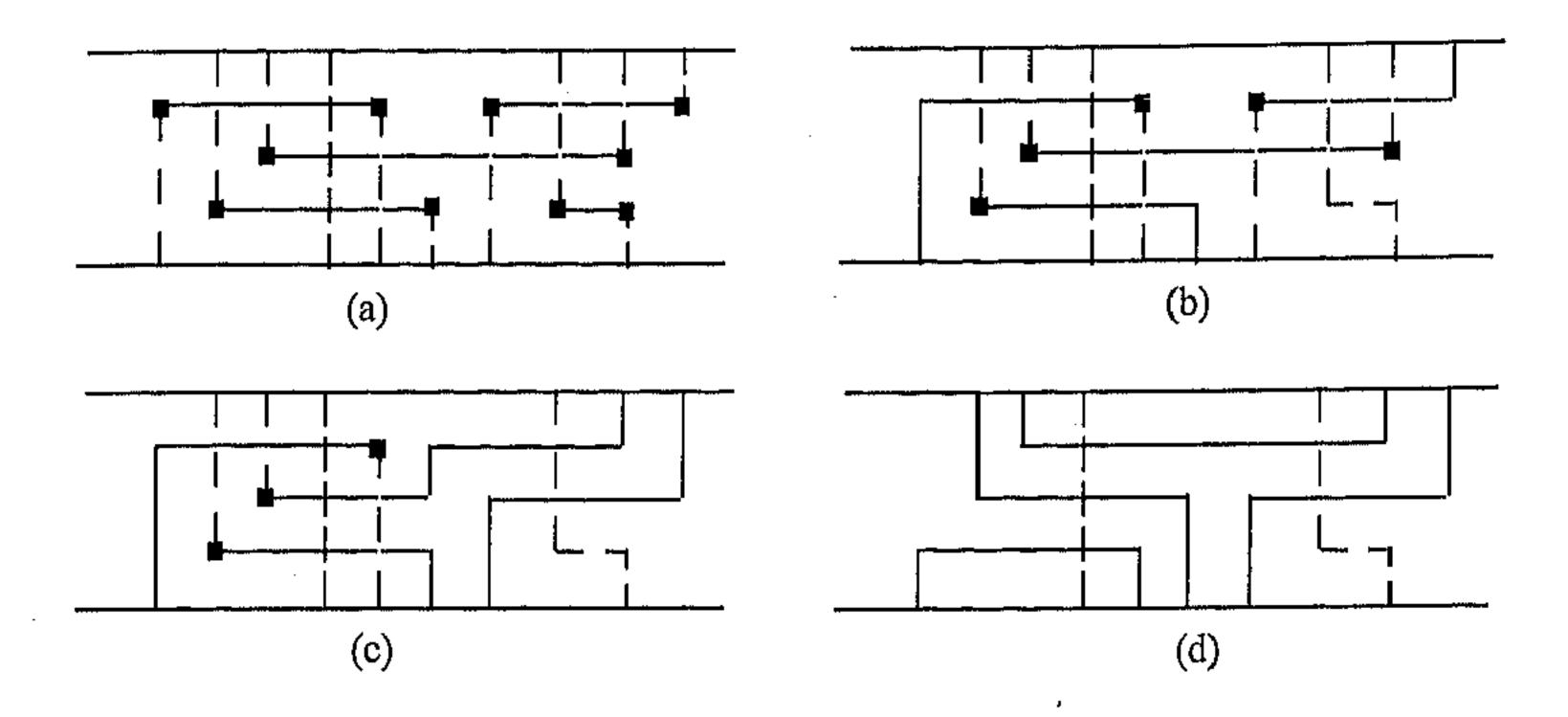

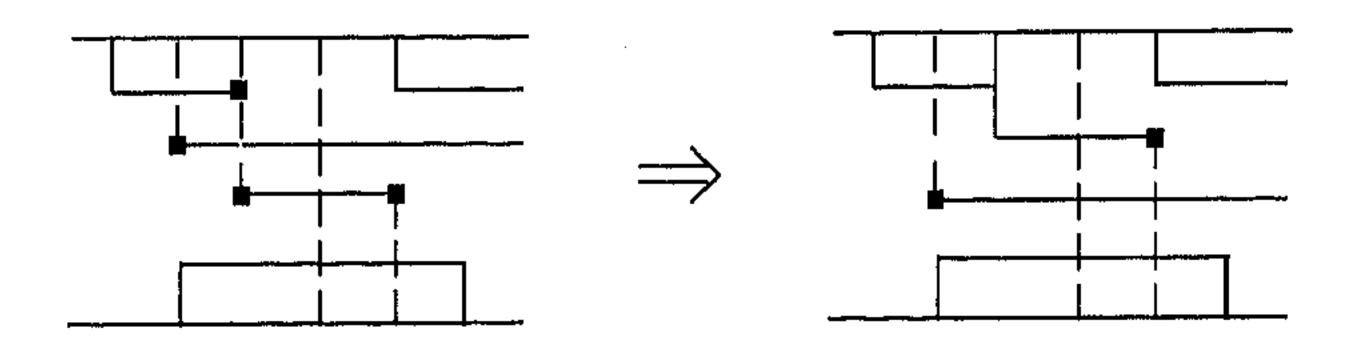

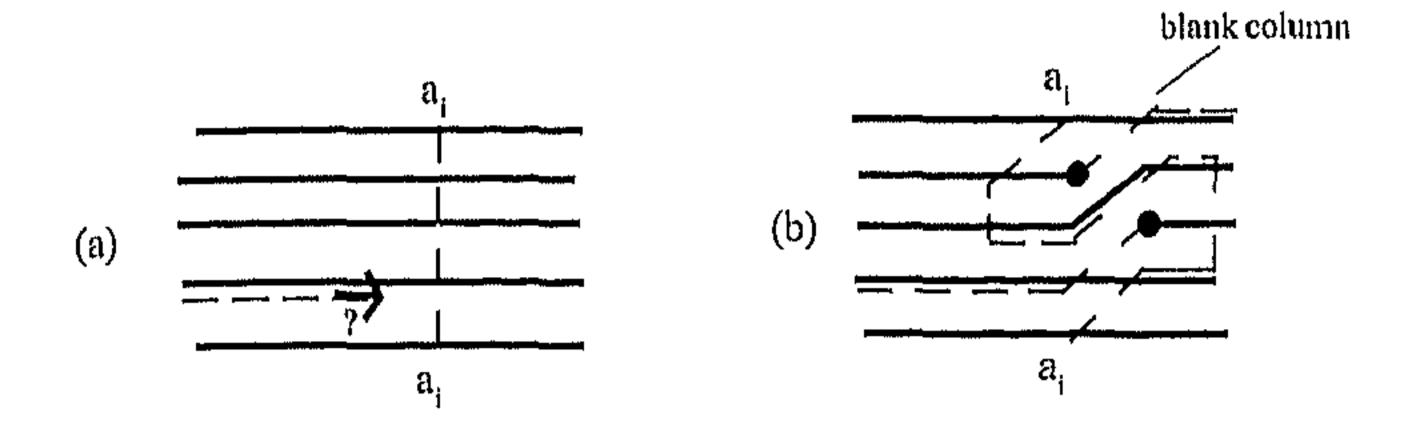

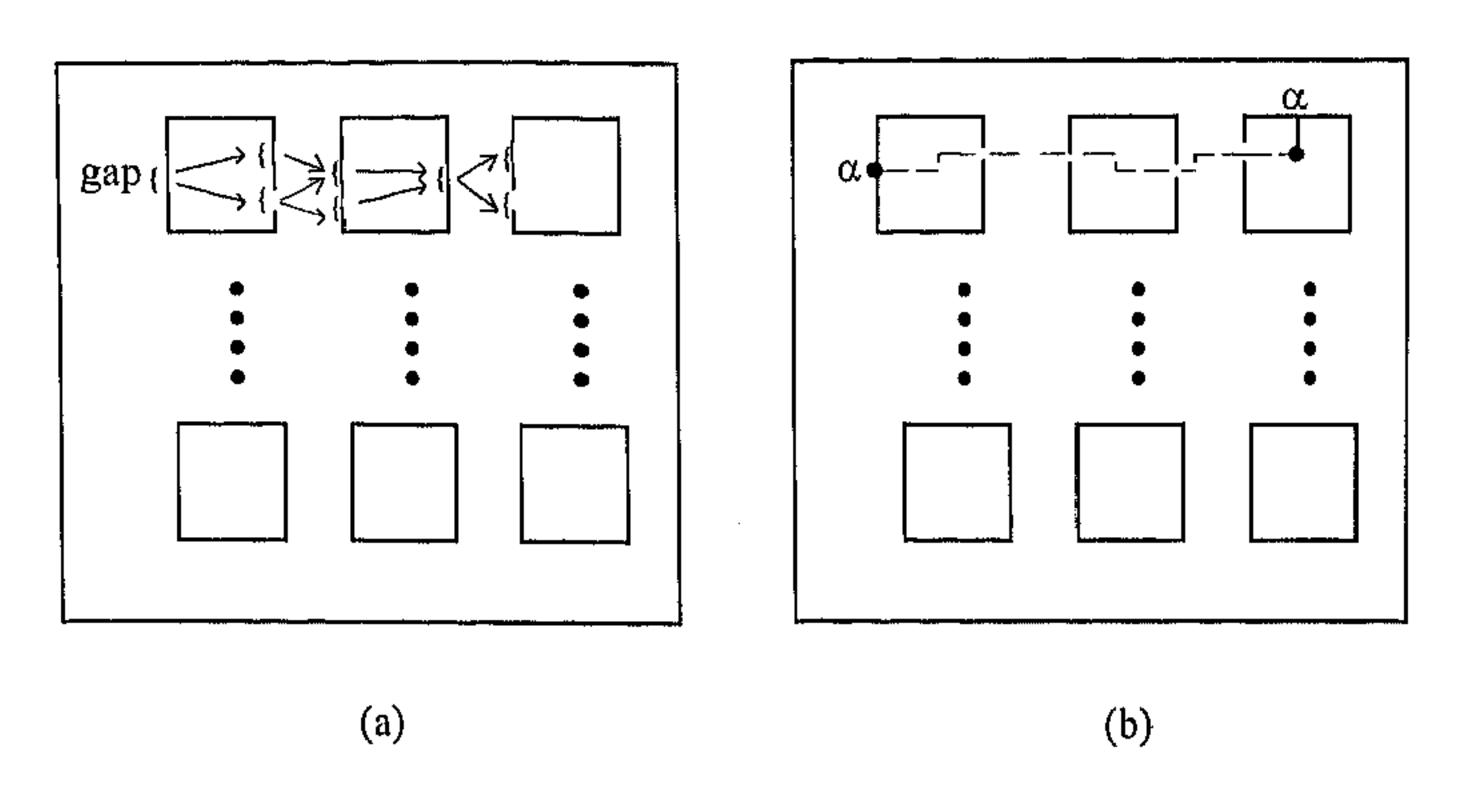

Routing of *L-shaped channels* also arises in many instances. In some routing model, the global routing problem can be viewed as a sequence of L-shaped channel routing problem [C87, CG96]. Here, a net-list along the boundary of an L-shaped channel is given, and the goal is to complete the interconnections minimizing (i) channel area, (ii) the number of vias, and (iii) wire length.

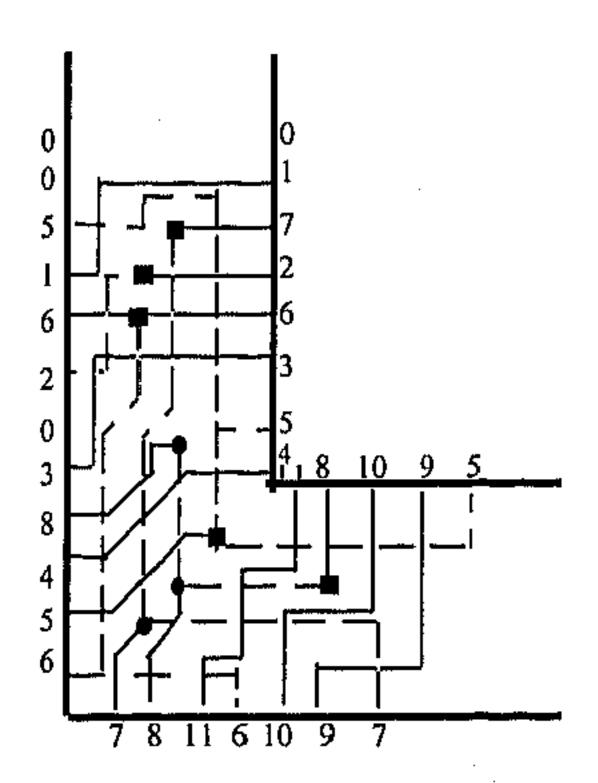

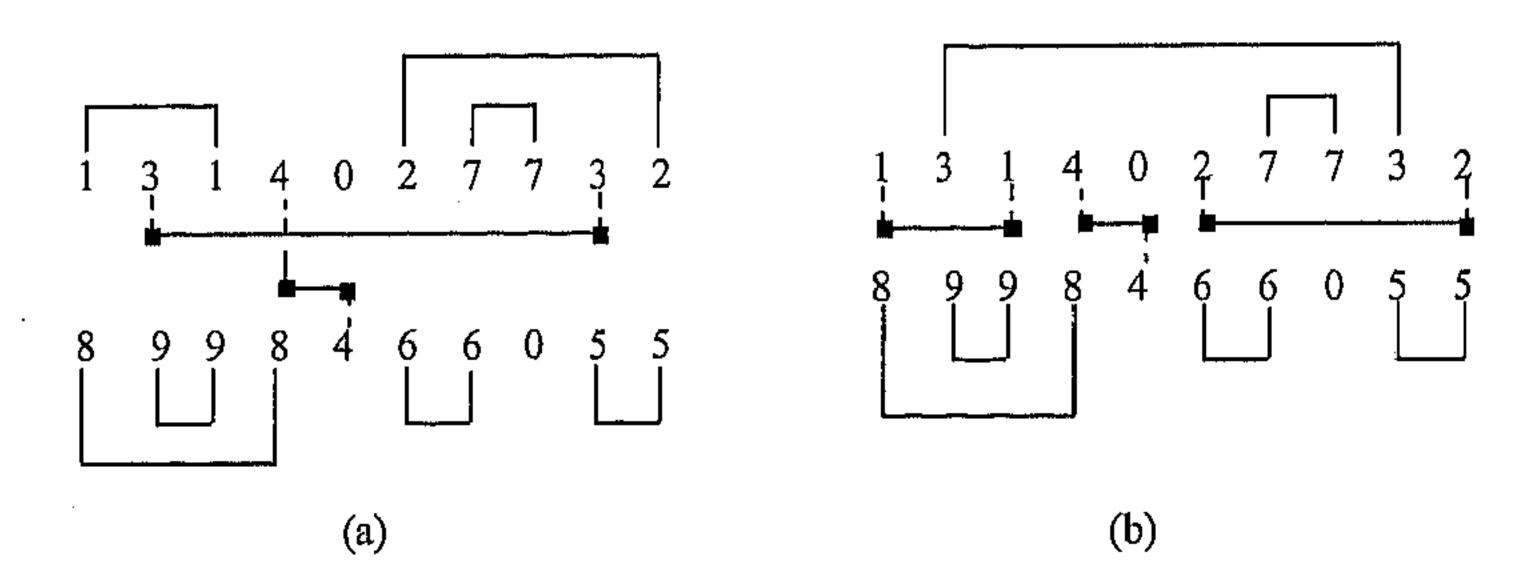

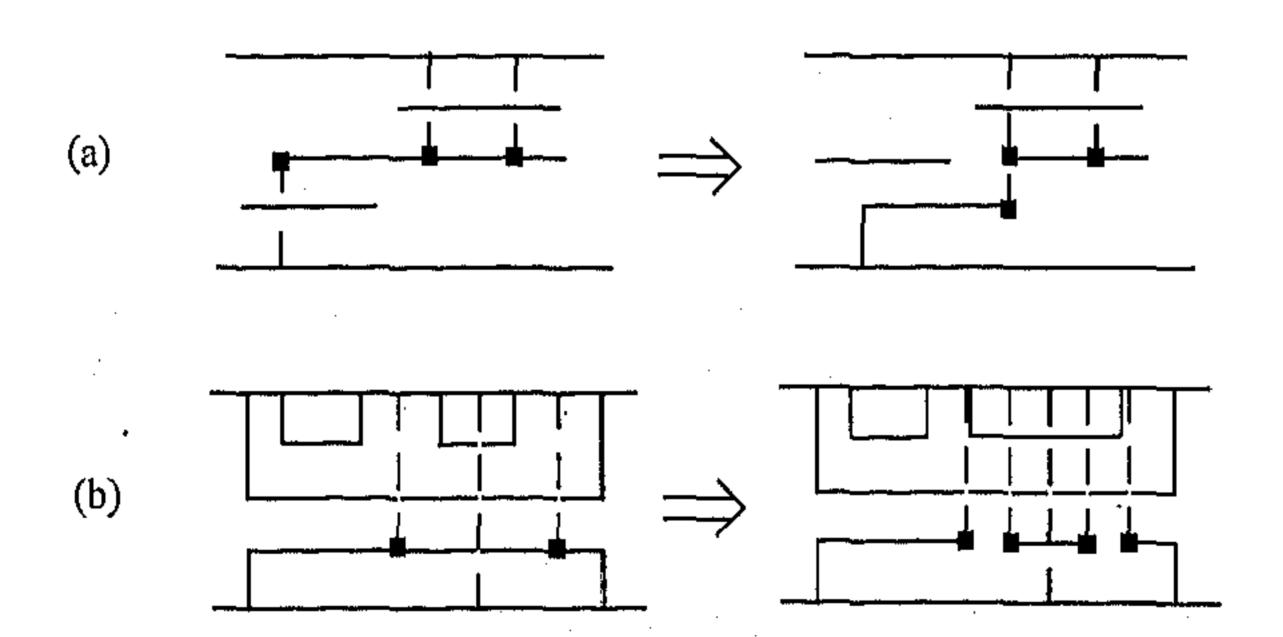

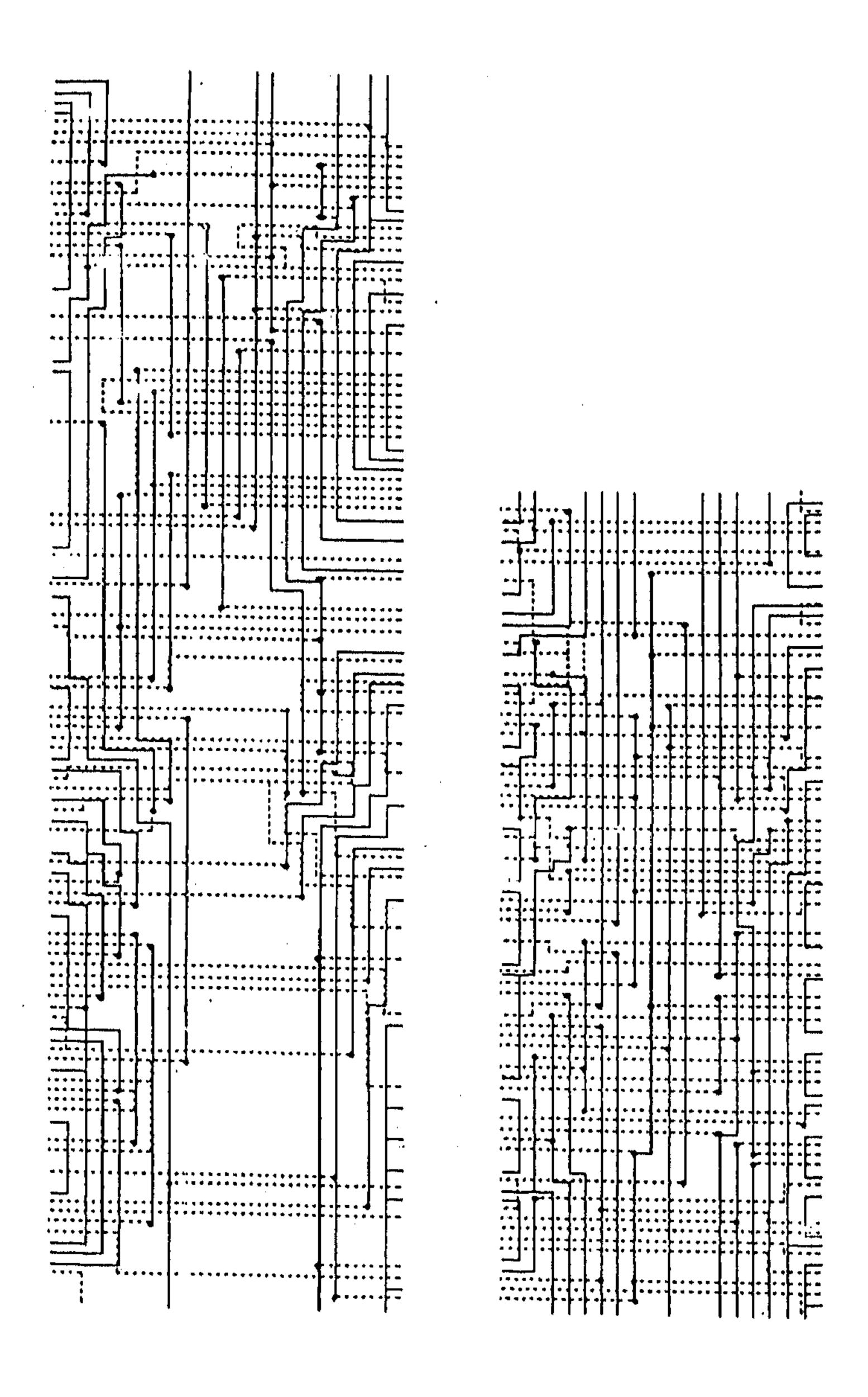

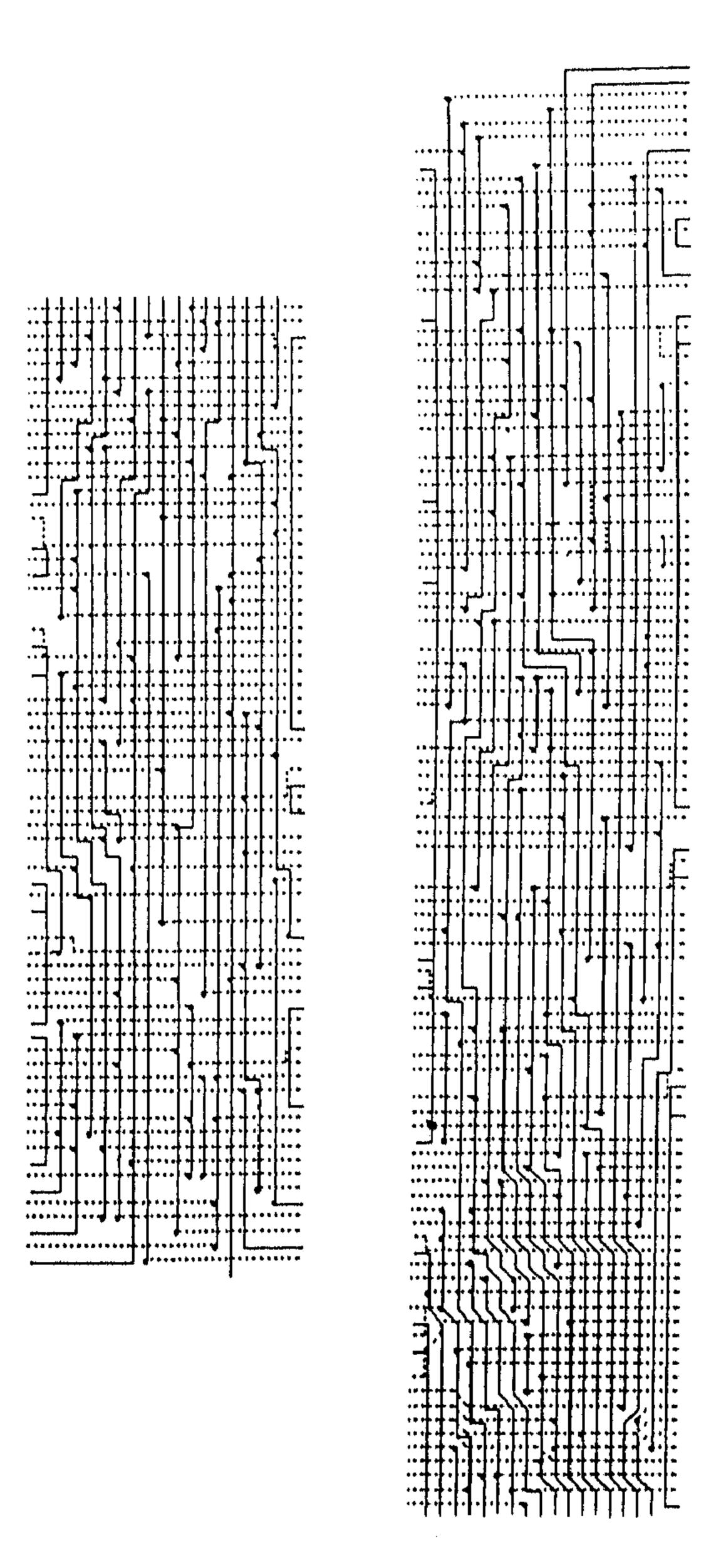

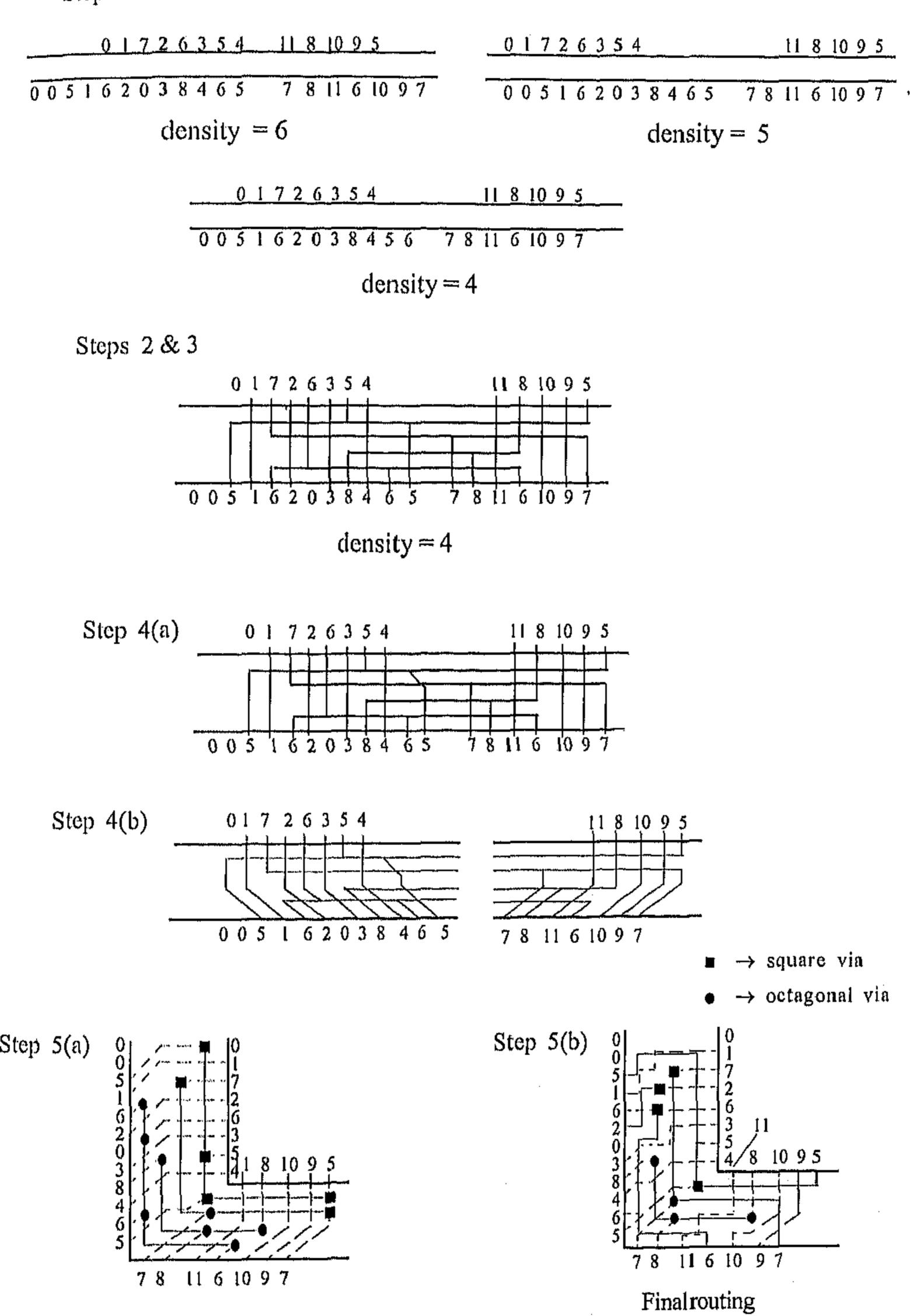

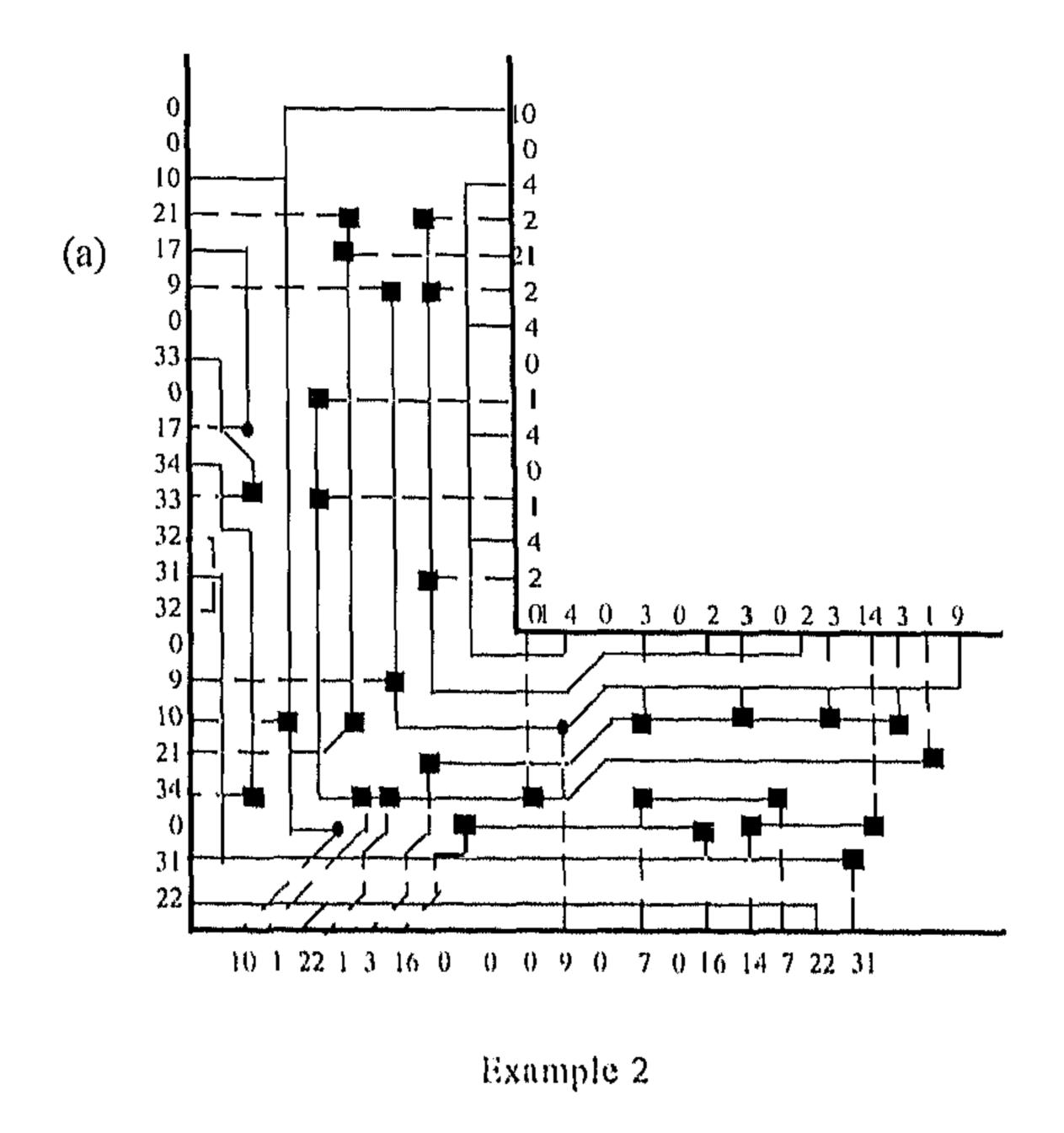

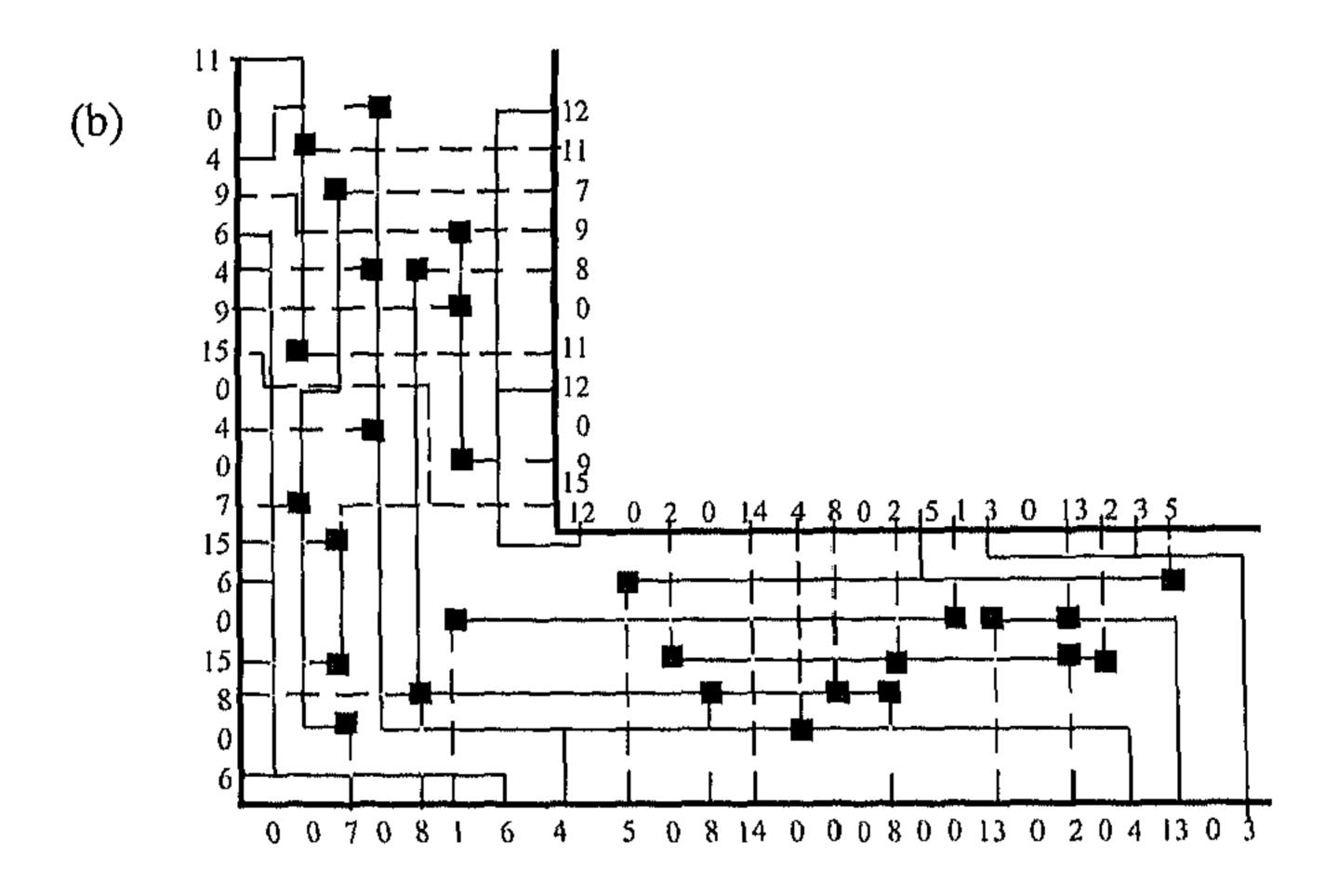

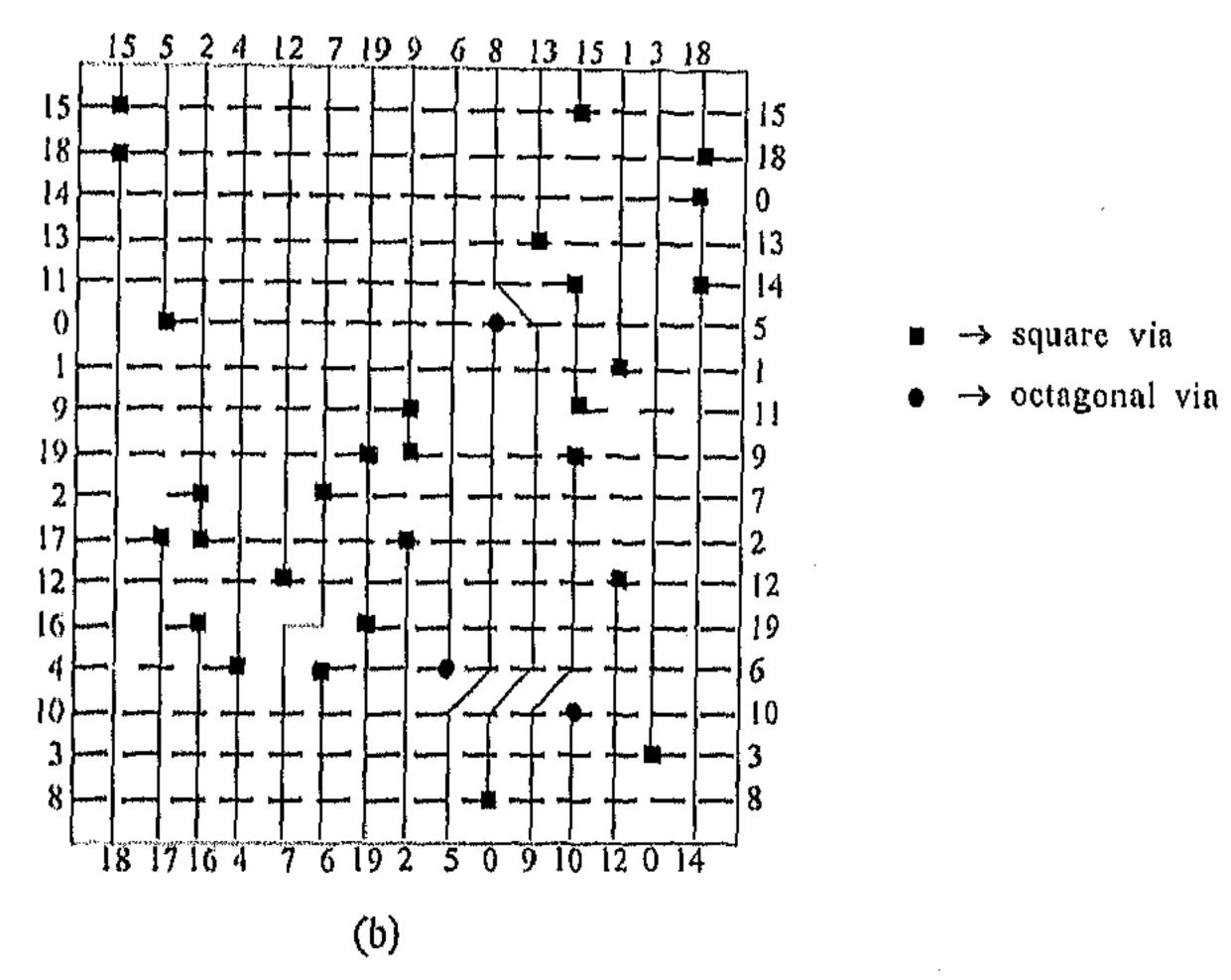

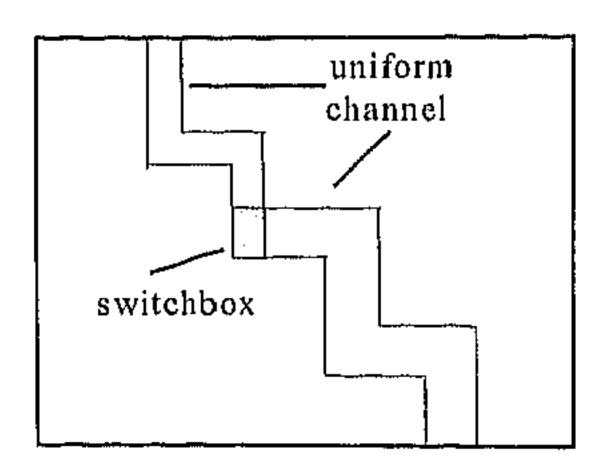

In this thesis, we propose routing algorithms for L-shaped channels, switchboxes and staircases in 2-layer Manhattan-Diagonal model with tracks in horizontal, vertical and  $\pm$  45° directions. The core of our proposed method lies on routing a right triangular region which requires  $O(n^2)$  time, where n is the number of nets which are routed through the triangle. We show that if the L-shaped channel has no cyclic vertical constraint, our algorithm runs in O(ld) time, where l is the length of the L-shaped channel, and d depends on the density of horizontal and vertical parts of the L-shaped channel, and the density of the triangular regions joining those channels. The exact expression for d is given in Chapter 6. Next, a greedy heuristic method is proposed for routing an L-shaped channel with cyclic vertical constraint, which guarantees a routing solution with at most d+1 tracks. The time complexity of the latter method is also O(ld). An example of an L-shaped channel and its routing is shown in Fig. 1.4.

The switchbox routing problem in MD-model is also solved elegantly. These techniques are easily extendible to the routing of staircase channels, and it yields

Fig. 1.4: Examples of L-shaped channel routing using MD-model

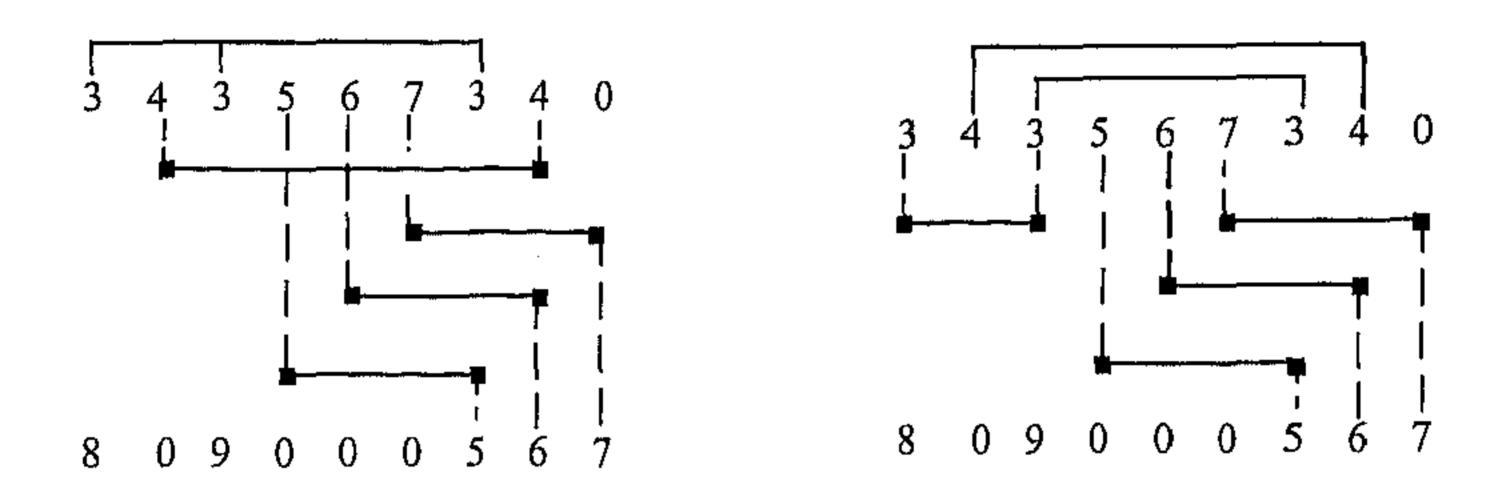

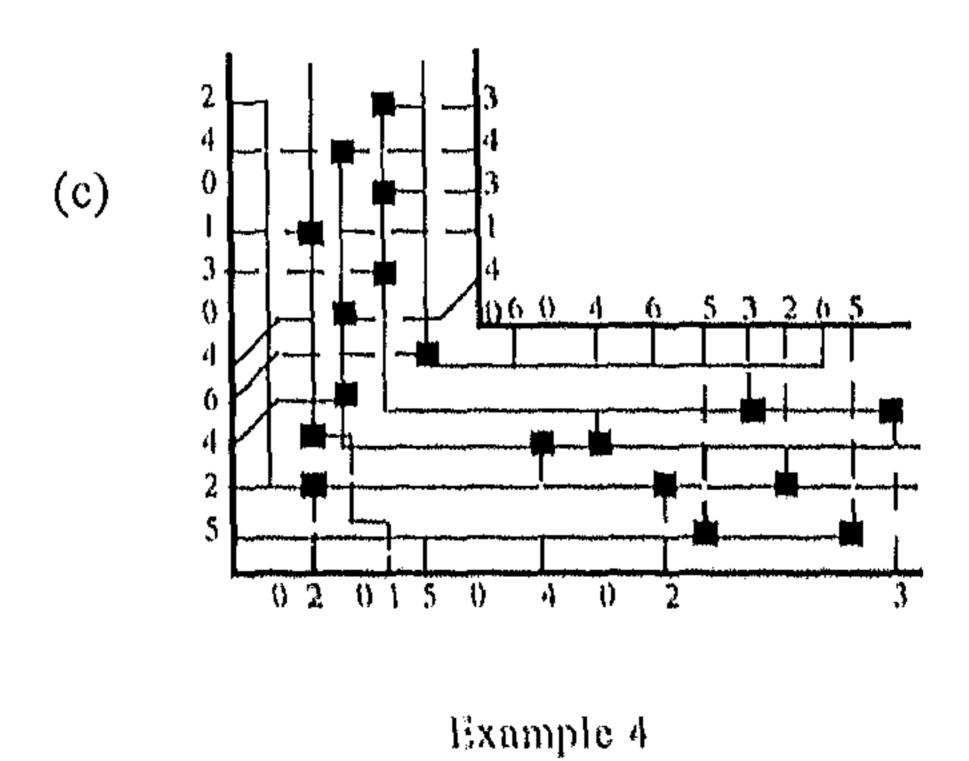

efficient solution to detailed routing in general floorplans [DSB98]. Experimental results show significantly low via count and reduced wire length, thus establishing the superiority of MD-routing over classical strategies used in [CH88]. An example of a switchbox and its routing is shown in Fig. 1.5.

Fig. 1.5: Switchbox routing using the proposed MD-model

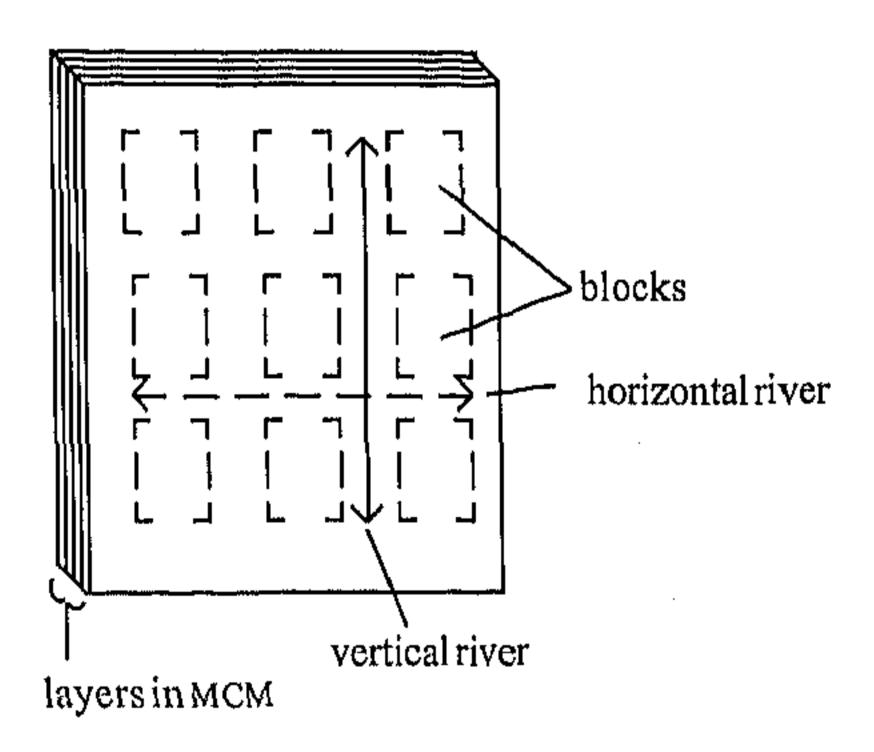

# 1.2.4 Routing in multi-chip modules (MCM)

With rapid decrease of feature size, efficiently packing multiple circuit modules in a single chip has become a promising area of research. Using MCM technology

a large number of functional blocks can be mounted and interconnected on a single substrate. The numbers of distinct nets and terminals are usually very high. A typical MCM may consist of 7000 nets on a grid size of over 2000 x 2000 [KC92]. With the emergence of deep sub-micron technology, the numbers of chip, nets, and terminals per net, in an MCM are likely to increase in the future.

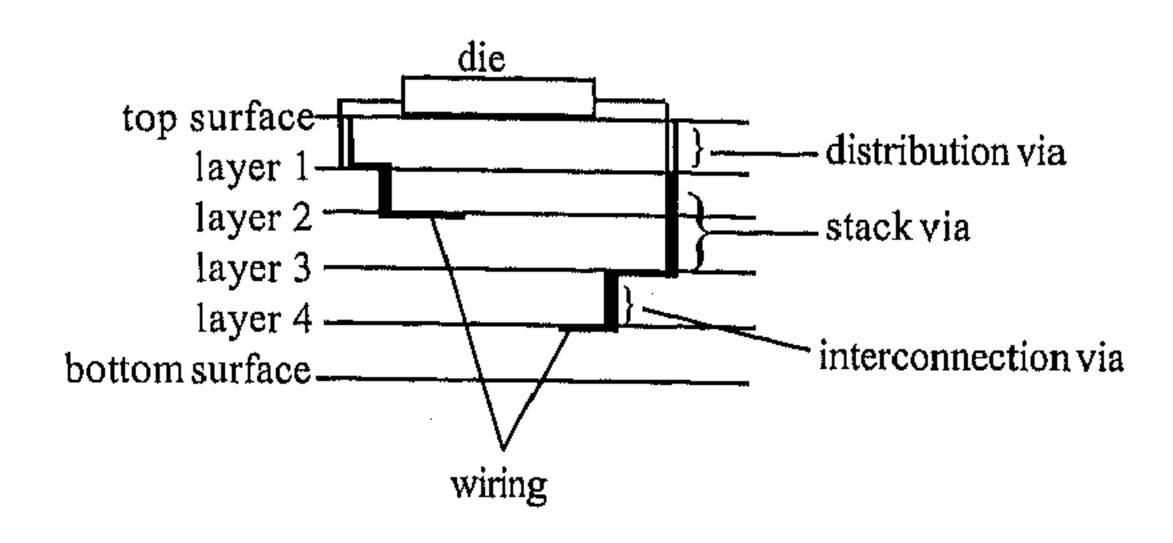

Inside an MCM, the circuit components are mounted on the top layer; other layers are used for pin redistribution and routing. As many layers are usually available for MCM routing, the main objective is to improve performance, i.e., to achieve tight packaging with lower fabrication cost, satisfying the constraints on net length, net separation, via size, via separation, etc. Thus, the primary goal is to minimize the number of vias, wire length, cross talks, delay in signal propagation, with the secondary objective of reducing the number of routing layers in the MCM.

Several approaches to MCM routing have been proposed recently [CLRS94, SBP95]. A pair of routing layers is considered at a time, and the yet unrouted terminals are projected on them through stack vias. Khoo and Cong developed SLICE [KC92] and V4R [KC95]; in the latter method, at most four vias are used for routing each two-terminal net in a non-monotone fashion. Multi-terminal nets are transformed into two-terminal nets. Another algorithm, called SEGRA, was proposed in [CRN97]. It uses a plane sweep technique and splits each multi-terminal net into two-terminal nets considering a minimum spanning tree among its terminals.

In [DNB99], we introduce an improved method of MCM routing. For high performance routing, one has to minimize the number of vias and wire length. To minimize the number of vias, we first route the nets having more terminals, through the layers that are closer to the top, such that a large number of nets is routed with short pieces of wires. To take care of the delay factor, we also route the farthest terminals of a net through the layers closer to the top, and explore subsequent layers if they are unavailable. The proposed algorithm consists of three phases. First, we preprocess the nets to determine a routing order. We estimate the cost of a feasible wiring for each net by constructing a minimum-bend rectilinear steiner tree among its terminals, avoiding the obstacles on the concerned layer. The wire length and the number of terminals of the net are used to define a metric called average path length. The ordering of nets for actual routing in the next phase depends on the average path length. In order to reduce delay for some important nets, one may need to change the order. In the next phase, actual routing is done assuming a reserved layer model. Nets are routed following the order as obtained in the first phase. After the completion of routing in the current layer-pair, the

unrouted terminals are projected in the next layer-pair and the same routing technique is adopted keeping the order of nets invariant. This process continues until all the terminals are routed. Our technique uses significantly less number of vias, which can be further reduced in the third phase, where we improve the routing by flipping and other techniques.

#### 1.3 Conclusion

In this thesis, we have reported various new results on channel routing in Manhattan as well as in Manhattan-diagonal model. Novel algorithms for switchbox and L-shaped channel routing problems have also been formulated and studied in this thesis.

We have explored many new combinational and geometric properties of routing problems and found interesting results based on which routing algorithms for channels, switchboxes and L-shaped channels have been proposed. Experimental results on benchmark examples demonstrate that the proposed algorithms outperform the existing ones both in execution time and in quality of solutions. A routing technique for multichip-modules has also been developed based on computational geometry. This algorithm achieves significant reduction in via count and wire length for MCM benchmarks.

# Chapter 2

## Review

#### 2.1 Introduction

Two important factors responsible for minimizing layout area of a VLSI circuit are:

- (i) circuit design which attempts to reduce the number of transistors keeping the functional behavior unaltered, and

- (ii) physical design of the circuit targeted to improve the geometric layout.

To reduce the complexity, the physical design phase of a VLSI circuit is split into five major steps, e.g., partitioning, floorplanning, placement, routing and compaction. A brief description of these steps is given below.

- 1. Partitioning: A chip may contain several millions of transistors. Layout design of such a circuit cannot be handled if the entire circuit is considered as a whole. This problem is nicely tackled by partitioning the circuit into a set of functional blocks (modules). Partitioning of large circuits is a hierarchical process. In each level, the blocks of its previous level are further partitioned into smaller sub-blocks. Partitioning of a block considers a set of important factors such as, the size and number of the sub-blocks, number of interconnections between the sub-blocks, etc. The set of interconnections among the sub-blocks are referred to as a netlist. The occurrence of the same signal net in different blocks is referred to as terminals. In the routing phase, the objective is to devise an efficient way of connecting the terminals of the same net using a set of available layers, satisfying a set of predefined constraints.

- 2. Floorplanning: After the partitioning phase, the size of each block is determined by the number and the type of components in that block.

Usually the blocks are assumed to be rectangular. In the floorplanning phase, the topology of the layout (the relative positions of the functional blocks on the chip) is determined based on the interconnection information among the circuit modules, so as to minimize the total area of the chip, and to reduce routing congestion.

- 3. Placement: The arrangement of components inside a block may be customized considering the interconnection pattern among its neighboring blocks. So, a set of possible aspect ratios is specified with each functional block before the placement phase. The floorplanning phase suggests the geometric adjacency among the functional blocks. The goal of the placement phase is to position the functional blocks on a floor of minimum area such that, the 100% interconnection between the blocks is feasible. Initially, a feasible placement of the blocks is determined considering an estimate of required routing space of different routing regions. It may actually results an unroutable layout. So, iterative improvements may be necessary during the placement process.

- 4. Routing: The objective routing phase is to complete the interconnection among blocks according to the specified netlist. The goal of this phase is to complete the connections among the pins of each net satisfying different constraints and optimizing different performance criteria.

- 5. Compaction: After the routing phase, an attempt is taken to reduce the layout area by compressing the layout from all directions parallel to the four boundaries of the rectangular floor defining the circuit. During the compaction process, the size of each circuit modules should remain unaltered. A substantial compaction reduces the wire length, which in turn reduces the signal delay between the components of the circuit. The compaction process must ensure that no design and fabrication rule are violated during the process.

The thesis is mainly concerned with the design and development of various routing techniques. In the rest of this chapter, we review the past works reported in this area.

## 2.2 Fabrication Factors

Continuing progress in the scale of integration has resulted in incorporation of a large number of functions in a single chip that increases the chip area,

and corresponding deterioration of performance. An immediate remedy is the minimization of interconnection area which reduces the die size. A router should also consider the following factors to achieve high performance goals.

Delay: Reduction of line width of the interconnection wires due to the development of high-resolution lithographic techniques generates high resistance through interconnection wires, and as a consequence it results in higher delay in a longer path in comparison to that in a shorter one. In a synchronous circuit, limitations on circuit speed are determined, in general, by the delay of the longest path through the functional blocks, and the presence of clock skew among the synchronizing circuit components. Thus to enhance the performance of the circuit, it is necessary to minimize the maximum wire length, and an efficient clock routing that achieves minimum clock skew.

Yield: The yield is the percentage of IC's fabricated on an wafer, which are free from faults and operate at or above the desired frequency and reliability. The yield can be enhanced by fabricating a larger number of dies on a single wafer by reducing die size. This also minimizes the waste area on the wafer surface. From the physical design point of view, the potential area for yield enhancement includes minimization of total wire length, routing with less number of jogs, net separation to reduce cross talks, via minimization, to name a few.

Cost: Minimization of die size and increase in the yield, reduce the cost of a chip. Thus enormous effort is needed to produce dies of minimum size with simultaneously improved performance, yield and cost and which are free from manufacturing defects.

A VLSI chip may contain several millions of transistors, and there may be several hundreds of possible routing paths for each net. This makes the routing problem computationally hard. To reduce the complexity of the routing phase, it is traditionally divided into two major phases, namely global routing and detailed routing.

# 2.3 Global Routing

Global routing, or in other words the loose routing, is the preliminary step of the complete routing process. Here the entire routing region is split into a set of sub regions (e.g., channels of different shapes, switchboxes, etc.),

depending on the layout style. A sequence of routing regions is assigned to each net without specifying the exact geometric layout of wires. The goal is not only 100% routing of all the nets, but also to minimize the total wire length / routing area. A detailed survey of various global routing techniques is given below.

#### 2.3.1 Different design styles

The objective functions for global routing depend on design styles. In this subsection, we discuss the standard design styles.

Full-custom: This is the most general design style where the functional blocks (of arbitrary sizes) may be placed at any location on the chip floor in a non-overlapping fashion. This allows very compact design; however, the process of automating a full-custom design style is more complex than other restricted models. The problem of routing is also very difficult since the routing regions are not symmetric. However, the routing space may be allowed to be redefined by slightly perturbing the placement of blocks. Here, the role of compaction is significant for area minimization of the entire circuit after routing is completed.

Standard cell: The standard cell design style is somewhat simpler than a full-custom design style. A circuit is partitioned into a set of predefined sub-circuits, called cells, which are available in the standard cell library. These cells are assumed to be rectangular and of same height. They are placed in rows, and the space between two adjacent rows is called a channel. The channels are used for routing the signal nets that appear among the cells lying on the same row or in adjacent rows. If a net appears in two cells appearing along the boundary of different channels, the interconnecting wire passes through the feedthroughs. A feedthrough is an empty space (cell) between a pair of topologically adjacent cells in a row, and it may be created wherever it is necessary during the routing process.

Gate Arrays: In gate array design, the entire wafer is prefabricated with an array of identical gates or cells. These cells are separated by both vertical and horizontal spaces called channels. Each functional block is mapped onto a prefabricated cell on the wafer, during the partitioning/placement phase. Now, the task of the router is to establish the connections between the prefabricated cells through the horizontal and vertical

channels. Note that, here the number of tracks allowed for routing in each channel is fixed. As a result, the purpose of routing is simply to complete the connections rather than minimize the area.

FPGA: It is a new approach to ASIC design that can significantly reduce manufacturing turn around time and cost. In general, an FPGA consists of a regular array of programmable logic blocks interconnected by a programmable routing network. A programmable logic block can be programmed by the user to act as a small logic module. Given a circuit, user can program the programmable logic module using an FPGA programming tool. One of the advantage of FPGAs is reprogrammability. In FPGA, a data channel is provided, which allows easy transfer of the new logic function and reprogramming the FPGA. Partitioning, placement and routing are three main steps for the physical design automation of FPGA. The partitioning problem mainly depends on the architecture in which the circuit has to be implemented. Placement problem in FPGAs is very similar to the gate array placement problem. The routing in FPGAs is to find a connection path and program the appropriate interconnection points.

## 2.3.2 Existing methods for global routing

The common problem of global routing for all the three design styles is to find the shortest path for connecting the terminals of a net placed in different blocks. The first work in this direction is the maze routing algorithm due to Lee [L61] and Moore [M59]. The algorithm is simple and it guarantees an optimal solution, if at least one such path exists. But as this algorithm is grid based, it requires a large amount of storage and its performance degrades rapidly as the number of grid points increases. Thus, this algorithm is very inefficient for a large full custom design problem. Numerous attempts have been made to modify Lee's algorithm to reduce its memory requirements [A67]. Soukup [S78] modified Lee's algorithm by proceeding towards the target through the grid points in a depth-first manner until an obstacle is encountered; a breath-first search method is then used to get around the obstacle. The depth-first search then resumes its motion towards target. The problem specification may however have some special requirements which do not permit fully automated routing. An interactive maze router [AS88] is available for this purpose, where restricted human interactions are allowed.

A heuristic algorithm using A\* search technique was proposed by Hadlock

[H77] to improve upon the speed. A widely applicable line-probe algorithm was developed by Makami and Tubachi [MT68], and essentially the same algorithm was independently proposed by Hightower [H69]. The basic idea of a line probe algorithm is to reduce the size of memory requirement by using isothetic line segments during the search process, instead of grids. The time and space complexities of these algorithms are O(L), where L is the number of line segments produced by the algorithms. In [ZLI96], an efficient algorithm for obstacle avoiding rectilinear shortest path among multi-terminal nets is proposed. This algorithm combines implicit strong connection graphs among the terminals of nets, and applies  $A^*$  search method to get an excellent routing solution. In all these methods, congested channels are assumed to be expanded as required. If the channel congestions are predefined, one may adopt the "rip-up and reroute" or "shove aside" techniques, as proposed in [B79, DK82].

All the algorithms we have considered so far, are related to routing of two terminal nets. These approaches can be extended to multi-terminal nets, but they involve large time and space complexities. Routing of multi-terminal nets is based on constructing a rectilinear steiner tree. The problem of finding a minimum-cost rectilinear steiner tree is NP-hard [GJ77]. The rectilinear steiner tree problem can be solved in polynomial time if the points appear on a set of axis-parallel lines, or on the boundary of the rectangular floor [AGH77]. Hwang [H76] has shown that the ratio of the cost of a minimum spanning tree to that of an optimal rectilinear stainer tree is no greater than 3/2. Good heuristic algorithm for finding the rectilinear steiner trees are available in [H78, HVW85]. Burman, Chen and Sherwani [BCS91] studied the global routing problem in a generalized geometry, called  $\delta$ -geometry, where the edges may be oriented in any of  $i\pi/\delta$  angles, where i can be any integer and  $\delta$  is also an integer ≥2. In [CSW89], a restricted case of Steiner tree, called Steiner min-max tree is used for the global routing problem. They propose an efficient algorithm for obtaining a Steiner min-max tree in a weighted coarse grid graph, where the vertices are labeled actual and steiner depending on whether the vertex corresponds to the terminal of a net or a steiner vertex. The weight of an edge depends on the density of the corresponding channel through which the pair of vertices may be connected, and the capacity of the same channel.

The general global routing problem can be mapped to a 0/1 integer programming problem. Heisterman and Lengaur [HL91] presented a hierarchical algorithm for the global routing of multi-terminal nets using integer linear programming.

In [V91], an interior point method is proposed for global routing. It uses the famous Karmakar's polynomial time algorithm [AKR+89] in the linear programming formulation of routing problem.

Global routing algorithm can be mapped to different other optimization problems based on its varying optimization functions. A multi-commodity flow-based algorithm is proposed in [SK87, CLC96]. Vecchi and Krikpatrick used simulated annealing technique [VK83] to solve the same problem.

A practical global router for row based layout, such as sea-of-gates, gate array and standard cell was developed by Lee and Sechen [LS88]. For gate array, Aoshima and Kuh [AK83] proposed a global routing algorithm based on multi-channel optimization. Karp et al. [KLR+87] discussed the problem of global routing in a two-dimensional gate array. It uses linear programming followed by randomized rounding-off technique [RT91].

Simultaneous partitioning and routing-driven correlated approaches for placement of mixed macro blocks and standard cells are available in [DK85, LD86, C87, KPS89] which recursively apply mincut algorithm of [FM82]. In [YW96], a novel edge cost model is proposed to capture the congestion of routing region using an incremental assignment strategy [S85]. Then a resistive network analogy [DK69] is used to characterize the routability of nets. The combination of the edge cost model and the resistive network model provides a very effective guidance for partitioning.

# 2.4 Detailed Routing

The detailed router places the actual wire segments within the region indicated by the global router, thus completing the required connections between the terminals. The detailed routing problem is usually solved by considering a region at a time. Regions generally are of the form of ordinary channels and switchboxes. Depending on the placement of blocks we can mark the routing regions and their ordering in which the routing will be done.

A routing region may have terminals only on two opposite sides of the region. This type of routing region is called channel. If the routing region is of rectangular shape, then it is called straight channel. An L-shaped channel consists of a region which is of L-shaped form. Switchbox is a rectangular routing region where the terminals are on all four sides of the region.

Characteristics of routing problem largely depend on the topology of the routing region. Regions may contain one or more layers. An electrical connection between the segments on adjacent conducting layers is made by etching a hole in the insulator before manufacturing the second conducting layer, and such a connection is called via. Multilayer routing problem is NP-hard [S85a] even when number of layer is one [R84]. One obvious constraint in routing problem is that no two wires from different nets are allowed to cross each other on the same layer. Various detailed routing algorithms have been developed depending on the nature of the problem and design goals.

#### 2.4.1 Routing considerations

There are many parameters in a routing problem which are usually determined by design rules and routing strategy.

- Two- and multi-terminal nets: Though simple algorithm may exist for two-terminal nets, practical algorithms must be designed for handling multi-terminal nets.

- Net width: The width of a net depends on the layer it is assigned to, and its current carrying capacity. Usually routers must allow power and ground nets for such width variation.

- Via restriction: Vias are necessary to connect the wires of the same net on different layers. Vias still remain a concern in routing problem as they increase manufacturing cost, decrease yield and performance. The physical dimension of a via is usually larger than the width of connecting wires in today's manufacturing technology. Thus minimizing vias increases chip space usage.

- Number of layers: Generally fabrication processes allow at least two metal layers for routing. Increase of layers increases the manufacturing cost and design complexity, but at the same time reduces chip area. In MCM routing, a large number of layers are available.

- Boundary type: A boundary is the border of the routing region which contains the terminals. Most detailed router assume that the boundaries are rectangular. If the terminals are on two opposite sides of the boundary, then they are said to form a channel. Terminals appearing on four sides form a switchbox. In three-sided switchbox, the terminals lie on three sides of the boundary. Boundaries may be irregular in shape. Some recent routers [C86, CK86, VCW89] have the capability of routing within irregular boundaries.

Net types: Power, ground and clock nets are considered critical nets. Since power and ground nets are normally wider than signal nets, they need special consideration. Clock nets require very careful routing preference, as the delay of the entire chip may depend on clock routing. Critical nets are routed before signal nets using specialized routers.

#### 2.4.2 Routing models

The most common model used in routing is the grid-based Manhattan model, where a rectilinear grid is superimposed on the routing region, and wires are restricted to follow path along the grid lines. A horizontal grid line is called a track, and a vertical grid line is called a column. If in addition, 45° diagonal lines, are present in the grid, the model is known as Manhattan diagonal (MD) model [DB96]. A routing model that does not use an underlying grid, is known as a gridless model.

In the grid-based approach, terminals, wires and vias are required to conform to the grid geometry. For grid-based router, different grid size can cause a via-alignment problem between different layers. The gridless approach allows arbitrary location of terminals, nets; vias and nets are allowed to have arbitrary widths. Due to these advantages, the gridless approach has gained more popularity than the grid-based approach [CK86].

Routing problems can also be modeled based on the layer assignment of horizontal and vertical segments of nets. In unreserved layer model, any net segment along horizontal, vertical, or 45° diagonal tracks can be placed in any layer. Any such segment is allowed in a given layer, as long as two different net segments do not overlap. However, two net segments can overlap if they are in different layers. In this model, routing space can be used more efficiently, and the number of vias is reduced significantly. We have used this model in the thesis extensively. In Manhattan model with reserved layer wiring, only horizontal or vertical segments are allowed to appear in a particular layer. In other words, each layer contains either horizontal or vertical wire segments but not both. In Manhattan-diagonal reserved-layer model proposed in this thesis, all diagonal net segments are assumed to appear in the layer where the horizontal segments are assigned. This restriction simplifies routing algorithms considerably and provides excellent solutions since vertical segments do not block horizontal segments and vice versa, as they are on different layers. Layers assigned to horizontally oriented segments are called horizontal (H) layers and those reserveded for vertically oriented segments are called vertical (V) layers. In the two layer routing H-V or V-H wiring model is used. When three layers are available, HVH, VHV models are used in general.

With the advent of two and a half layer technology used in the layout design of standard cells, several routers now-a-days use the extra routing area inside the cell area for interconnection. These models are referred to as over-the-cell routing which renders considerable savings in channel width [CL88, CPL90, HSS91, LPHL91].

#### 2.4.3 Channel routing

A channel routing problem is specified by channel length, net list of the channel, and the number of layers. The goal of channel routing is to complete interconnections of all the nets in the channel satisfying design rule so that the channel width is minimized. Optimization of other secondary objectives, e.g., minimizing the number of vias, wire length, length of the longest wire are often required for higher performance and good yield.

We describe here few basic definitions and terminologies related to channel routing.

Channel area: The space between two adjacent parallel rows of cells.

- Top (bottom) terminal list:  $T = (t_1, t_2, ..., t_m)$  ( $B = (b_1, b_2, ..., b_m)$ ), where  $t_i(b_i)$  is a positive integer identifying the nets that enters through the i-th column in the channel at the top (bottom). If  $t_i(b_i) = 0$ , no net has to be connected to the ith terminal.

- Left (right) connection set: The set of nets that enters the channel from the left (right) end of the channel.

- Local density and density [YK82]: The local density  $d_j$  of column j, is the number of nets crossing that column. The density d of a given channel is defined by  $d = \max_{1 \le j \le m} \{ d_j \}$

- Doglegging: When a net is broken into two or more horizontal segments occupying different rows, a vertical segment is used to connect those horizontal segments. This is called doglegging, which may be necessary to complete routing, and to reduce channel width. Doglegging however, tends to increase vias.

- Vertical constraint graph: A directed graph G(V, E), whose nodes V represent horizontal segments. A directed edge  $(i,j) \in E$  implies that horizontal

segment i must be placed above the horizontal segment j, because of a vertical constraint. If G is cyclic, routing requirement cannot be satisfied without doglegging in two-layer reserved model.

#### 2.4.3.1 Single row routing problem

In this scenario, a set of evenly spaced terminals of two or multi-terminal nets appear on a real line, which is called the net axis. The single row routing problem is to realize the interconnection of the nets by means of non-crossing paths which are basically the horizontal and vertical line segments. All paths are placed on a single layer so that no two paths cross each other and each path cannot occupy two tracks at any column. The area above and below the node axis is called the upper street and lower street respectively. The number of tracks available for routing in these areas is called their capacity. For a given realization, the number of horizontal tracks needed in these area is called upper and lower street congestion. The most common objective function is to minimize the maximum of upper and lower street congestions. The single row routing problem was introduced by So [S74], for the layout design of multilayer circuit board. Later on, extensive studies on this problem were made in [HS84, KKF79, RS83, RS84, TKS76, TKS82, TSK84]. In [SD89], Sherwani and Deogun developed a new graph-theoretic approach for this problem.

#### 2.4.3.2 Single layer routing algorithm

Given a set of blocks with terminal of different nets, placed on a routing region, the objective of the single layer routing problem is to establish

- (i) connections (routing) among the terminals of each net in the same layer,

- (ii) the routing of different nets are non-overlapping and does not violate the specified design rule.

Here the problem is to determine whether all the nets can be routed in the same layer. Although the general single layer routing problem is conceptually easier than the multi-layer routing problem, it is still computationally hard. Different cases of this problem are handled in polynomial time [BP83, DKS\*87, LP83, M90, SD81, T81].

## General river routing problem

River routing is a special case of single layer routing, where all terminals lie on the boundary of the region and every net consists of exactly two terminals

and there are no blocks in the region. A solution exists if terminals are located in such a way that nets do not cross over. In [H83a, JP89, LP83, ST83, TH90], the formulation of river routing problem was considered. Hsu [H83a] proposed an algorithm for general river routing problem which is capable of routing arbitrary shaped rectilinear regions, and guarantees a solution if one exist. The algorithm is gridless and allows arbitrary net widths and wire separations.

#### 2.4.3.3 Two-layer channel routing algorithm

The main objective of routing is to reduce the routing area by minimizing the channel height. Let  $h_{max}$  and  $v_{max}$  represent the maximum clique in horizontal constraint graph (HCG) and the longest path in vertical constraint graph (VCG) respectively, for a routing instance. Then lower bound on the number of tracks of a two-layer dogleg free routing problem is  $max(h_{max}, v_{max})$ . The algorithms are mainly based on left-edge, graph based, greedy or hierarchical routing. Left-edge algorithms (LEA) [HS71] start with sorting the trunks from left to right and assign the segments to a track such that no two segments overlap. Some algorithms use various graph modeling, such as Interval graphs, permutation graphs etc., to assign nets to tracks. The algorithm in [RF82] uses a greedy strategy to route nets in the channel. It starts with the leftmost column and works towards the right end of the channel by routing the nets one column at a time. The hierarchical router generates the routing in the channel by repeatedly bisecting the routing region and then routing each net within the smaller routing regions to generate the complete routing.

The first algorithm developed for channel routing was the left-edge algorithm, proposed by Hashimoto and Stevens [HS71] which uses a reserved layer model and does not allow doglegs and any vertical constraints. Consequently, it does not allow cyclic vertical constraints. Deutsch [D76] proposed an algorithm known as dogleg router by observing that the use of doglegs can reduce the channel height. Like LEA [HS71], the dogleg router uses a reserved layer model. Experimentally dogleg routers achieve far superior results as compared to LEA, often requiring very few tracks beyond the channel density.

Sangiovanni-Vincentelli and Santomauro [VS82] proposed YACR (yet another channel router) which operates under the assumption that a user may add vertical tracks when they are needed anywhere within a channel. Clearly one can achieve the channel width equal to density under these assumptions, since a vertical column may be added every time there is a vertical conflict,

after the horizontal segments are packed by left edge routine. YACR does not use dogleg and attempts to minimize heuristically the number of added columns. Experimental results demonstrate improvement in overall routing area with fewer vias over routers operating within classical model. YACR-2 is the follow-up version of YACR, where it is not allowed to add columns but it is allowed to perform horizontal jogs on the vertical layer which may result in wire overlap. The algorithm works in two phases: horizontal track assignment and maze running. YACR-2 is very fast and practical in most cases, since most of the technologies allow limited wire overlap.

Yoshimura and Kuh [YK82] presented a new channel routing algorithm based on net merging. This work is the first attempt to analyze the graph theoretic structure of the channel routing problem. It considers horizontal and vertical constraint graphs and assigns tracks to nets so as to minimize the effect of vertical constraint chains in the vertical constraint graph. It does not allow dogleg and cannot handle vertical constraint cycles. The main steps in this algorithm are zone representation, net merging to minimize vertical constraint chains, and track assignment.

Chen and Kuh [CK86] first proposed a gridless variable-width channel router called Glitter. Glitter can utilize multiple layer technology and design rules. Terminals can be located at arbitrary positions and can be located on off-grid points. No columns or tracks are used in routing. Only the wire width, spacing, and via size are the factors in the routing algorithm. It is a reserved-layer routing model and is considered similar to net merge algorithm which uses a weighted constraint graph formed by using vertical and horizontal constraint graph.

Assigning the complete trunk of a multiterminal net severely restricts LEA and dogleg routers. Optimal channel routing can be obtained if it can be guaranteed that for each column, there is only one horizontal track per net. Based on this observation, one approach to reduce channel height could be to route nets column by column trying to join split horizontal tracks (if any) that belong to the same net as much as possible. Based on the above observation and approach, Rivest and Fiduccia [RF82] developed greedy channel router. The algorithm starts from the leftmost column and places all the net segments of a column before proceeding to the next right column. In each column, the router assigns net segments to tracks in a greedy manner. The greedy router allows the doglegs in any column of the channel, not necessarily where the terminal of the doglegged net occurs.

In [BP83], Burstein and Pelvin presented a two-layer channel router based on the reduction of the routing problem in (m x n) grid to the routing in (2 x n) grid and consistent utilization of divide and conquer approach.

Kowamoto and Kajitani [KK79] proposed an algorithm that guarantees routing with an upper bound of number of tracks equals to the density plus one, but additional columns are needed to complete the routing. Ho, Iyenger and Zhenq [HIZ91] developed a simple but efficient heuristic channel routing algorithm, which is greedy in nature.

All algorithms are not equally good in nature. Many benchmark examples can certify the quality of channel router. In most famous deutsch difficult example, dogleg router uses 21 tracks and 346 vias. In the same example YK-router takes 20 tracks and 403 vias and greedy router takes 20 tracks and 329 vias. Most popular hierarchical and YACR2 take 19 tracks each, and 326 and 287 number of vias respectively.

#### 2.4.3.4 Multi-layer channel routing algorithm

With the advance in VLSI technology, utilization of more than two layers for signal routing has become feasible. Most of the current gate-array technologies use three layers for routing. For example the Motorola 2900ETL macrocell array is a bipolar gate array which uses three metal layers for routing [S93].

Both the reserved layer and unreserved layer model are considered for three-layer routing algorithm. The reserved layer model can be classified into the VHV model and the HVH model. In the three layer VHV model the lower bound on the number of tracks for a routing problem is  $h_{max}$ , whereas in HVH model, the lower bound on the number of tracks for a routing problem is  $max(v_{max}, h_{max}/2)$ .

In [CL84] Chen and Liu presented a three layer channel router based on the net merging method and the left edge algorithm introduced by Yoshimura and Kuh [YK82] for their routing algorithm. As no vertical constraint exists in VHV, in this context, the left edge algorithm is sufficient. But in the HVH routing, vertical constraint exist, so the concept of (net) merging algorithm was extended to the HVH problem. In [CWL88], Cong, Wong, and Liu presented a general technique that systematically transforms a two-layer routing solution into a three-layer routing solution which is very similar to the Yoshimura and Kuh algorithm. Chen [C86] proposed a three-layer gridless router, called

Trigger, which is an extension of Glitter, the gridless router appeared in [CK86].

In [PZ87] Pitchumani and Zhang developed a three-layer channel router that combines both HVH and VHV models, based on the idea of partitioning the channel. In this approach the channel can be thought of as two separate channels, not necessarily of the same size. One portion (upper or lower) is routed using the VHV and the other portion is routed using the HVH model. A transition track is usually needed between the two portions. The algorithm does not allow any dogleg. This algorithm is a generalization of pure HVH and VHV approaches. This algorithm partitions the given netlist into two netlists, such that each netlist is best suited for either VHV or HVH style of routing. It then routes them separately thus obtaining two sub-solutions. The algorithm then insert transition tracks to complete the connections between the two routed sub-solutions.

In [H85], Hambrusch presented an algorithm for a n-layer channel router. The number of layers, the channel width, the amount of overlap and the number of contact points are four important factors for routing multi-terminal nets in multi-layer channels. An insight into the relationship between these four factors is also presented in [H85]. In [BBD+86], Braun developed a multi-layer channel router called Chameleon, based on YACR2. The main feature of Chameleon is that it uses a general approach for multilayer channel routing. Stacked vias can be included or excluded, and separate design rules for each layer can be specified.

In [ED86], Enbody and Du presented two algorithms for n-layer channel routing that guarantee successful routing of the channel for n > 3.

#### 2.4.3.5 Via minimization and over-the-cell channel routing

Most of the existing routing algorithms use a large number of vias to complete the routing. This is due to the fact that most routers use a reserved layer model. However, vias are undesirable from fabrication as well as circuit performance point of view and therefore, the number of vias should be kept as small as possible. Different via minimization approach is followed for reducing vias in a layout design. In constrained via minimization problem (CVM) we are given a set of wire segments, and k layers for routing, where the placement of wire segments has already been determined by some router. The problem is to assign each segment to one of the layers without changing the topology so

that the number of vias required is minimized. In unconstrained via minimization problem (UVM), the placement and the layer assignment of segments are not given. The problem is both the placement of the segments and assignment of layers so as to minimize the total number of vias. UVM is also known as topological via minimization problem (TVM).

Hashimoto and Stevens [HS71] first formulated the two layer CVM problem as a graph-theoretic max-cut problem. The problem was initially thought to be NP-complete which led other researchers to develop heuristic algorithms [CK81, SV79]. Chang and Du [CD87] developed a heuristic algorithm by splitting vertices in a graph. Kajitani [K80] showed that the two-layer CVM problem can be solved in polynomial time when the routing is restricted to a grid based model and all the nets are two terminal nets. Pinter [P82] proposed an optimal algorithm for two-layer CVM problem when the maximum junction degree is limited to three.

The TVM problem was first introduced by Hsu in [H83]. Marek-Sadowska [S84] proved that the TVM problem is NP-complete. Sarrafzadeh and Lee [SL89] and Cong and Liu [CL91] considered the crossing-channel TVM problem, and shown that the Crossing-channel K-layer TVM problem is solvable in polynomial time.

## 2.4.4 L-shaped channel and switchbox routing

L-shaped channel and switch box routing problems are the generalization of the channel routing problem. In L-shaped channel routing problem, terminals are located in the boundary of the L-shaped region. Kajitani [K83] first introduced the concept and term of safe routing order and studied the problem analytically. In order to overcome cyclic dependencies in routing order for nonslicible topologies, L-shaped routing regions [DAK85, SB91] were introduced. Switchbox is a four sided enclosed region where terminals are located on all four sides and routing must be completed within this region.

Algorithms by Maddila et al. [MZ89] for general routing regions are based on the restrictive knock-knee model [S93]. Tsai et al. [TCC+92] formulated general area routing as a planning problem in which the routing process is decomposed into a conjunction of subgoals; each subgoal consisting of selection of net segments and assignment of track resources. However, it may need to backtrack and may not generate any solution as it uses the Manhattan model even if Manhattan-diagonal routing exists. The time complexity of this method is high. Among non-Manhattan geometries, a diagonal model with  $\pm$  45° wires has been adopted [LLS91, C87]. Song [S92] presents an optimal knock-knee diagonal routing for L-channel with two-terminal nets only. In

Manhattan-diagonal (MD) model which combines diagonal and Manhattan geometries, routing method for straight channels based on sorting was proposed in [CR91]. Another MD channel router was presented by Wang [W91] but the track count and via count for denser channels seem to be higher and too many jogs are required. Recently, Das et al. gave a simpler MD channel router providing reduced wire length and vias [DB96]. Nevertheless, applicability of these methods to realistic routing in general regions are to be studied.

In general, switchbox routing is more difficult than standard channel routing. Theoretically, it falls into the category of NP-hard problems [S93]. Several heuristics are developed for the problem. Hamachi and Ousterhout [HO84] proposed a good switchbox router. The idea of Greedy channel router can be naturally extended to do the switchbox routing [L85]. Hierarchical channel router can be modified by introducing alternate partition in both vertical and horizontal directions instead of partitioning along the length of the channel [BP83]. One of the best practical switchbox router was proposed by Joobani [J86]. His algorithm WEAVER, was a successful knowledge-based expert-system router. Cohoon and Heck developed a computational-geometry-based tool BEAVER for switchbox routing.

## 2.5 MCM Routing

To get the advantage of advance fabrication technology, it is reasonable to consider new technique for packaging which can increase the packing density. Packaging has an important role in determining interconnection delay, cost, speed, reliability of high-speed system and the simplification of interconnection in the PCB. Recently, the multi-chip-module technology (MCM) has been developed that provides a common substrate where several bare chips can be mounted on the top layer. The substrate consists of multiple routing layers used for chip-to-chip interconnections. MCM routing problem is much more difficult in comparison with the conventional IC or PCB routing problem.

In MCM, chips are flip mounted on the top layer via solder bumps. The next few layers are called redistribution layers which are required to connect the chip bonding pads through the surface pads to the signal wires. Next, there are several interconnection layers. The MCM routing problem is a three-dimensional area routing problem where routing can be carried out almost everywhere in the entire multilayer substrate.

There are several new and interesting design automation problems associated with this technology [D90, HSV+90, PPC89]. Cho and Sarrafzadeh [CS91] investigated the pin redistribution problem on a uniform grid that arises in the design of MCM. There exist several methods for MCM routing, after pin redistribution step [CLR+94, D90, HSV+90, HYY90, KC92, KC95, MBG+91, SK92]. The approaches in [CLR+94, HYY90, MBG+91] extend the traditional maze routing technique [L61]. The methods in [HSV+90, SK92] uses layer assignment in order to overcome the size and net ordering. Here a global routing instance is obtained and then each net is assigned to layers so that wires of different nets do not intersect each other. Recently Khoo and Cong developed two powerful routers, namely SLICE [KC92] and V4R [KC95], which iteratively process the nets. Cha et al. [CRN97] propose a simple router SERGA. An improved technique for via minimization in MCM has been reported in this thesis.

# Chapter 3

# Over-the-cell Channel Routing

#### 3.1 Introduction

The two-layer channel routing is the most widely used technique for interconnecting nets in VLSI design. With the advent of two and half layer technology used in the layout design of standard cells, several channel routers now-a-days use the extra routing area available outside the channel for interconnections. These routers are called *over-the-cell* channel routers which render considerable savings in channel width [DG80, SS87, GN87, CL88]. Over-the-cell channel routing problem is known to be NP-hard [GN87]. The best known heuristic algorithm for over-the-cell channel routing appeared in [CL88], which consists of three major phases in the following sequence: (i) routing over the cell, (ii) choosing net segments within the channel and (iii) routing within the channel.

It is easy to observe that the first two steps are highly interrelated. Routing a net over the cell may force some other nets to be routed within the cell through the heavily congested area. Thus maximizing the number of over-the-cell candidates as suggested in [CL88] may not lead to a good solution. In this thesis we describe a new heuristic algorithm which iteratively selects over-the-cell nets with an ultimate objective of minimizing channel width. Experimental evidence shows considerable improvement over earlier results [CL88] in the number of tracks used both inside the channel and over the cell.

# 3.2 Formulation of the Problem

Consider a rectangular channel with n columns and two rows of terminals along its top and bottom sides. A number between 0 and m is assigned to each terminal. Terminals with the same number i  $(1 \le i \le m)$  are to be connected by net i, while those with number 0 designate unconnected terminals.

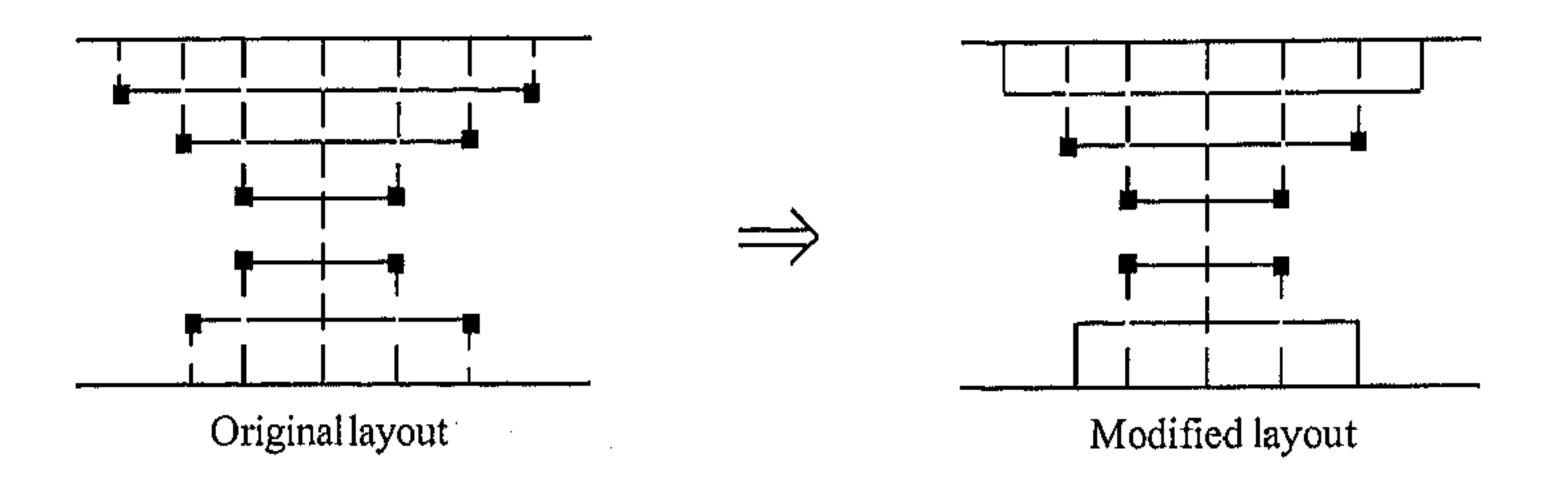

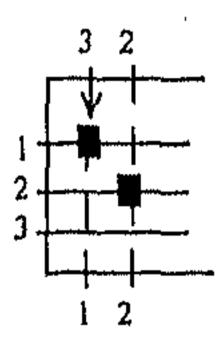

We assume two routing layers within the channel and a single layer over the cell. Routing consists of only rectilinear wire segments. Inside the channel, all horizontal segments lie on one layer and all vertical segments on the other. Interconnection between horizontal and vertical layers is accomplished through via holes. We also assume that the terminals are accessible only at the edges of the cell. Given a netlist, our objective is to generate a routing with possible over-the-cell interconnections which minimizes the channel width i.e., the number of horizontal tracks inside the channel. Fig. 3.1 displays an example of conventional versus over-the-cell routing.

Fig. 3.1: Conventional vs Over-the-cell channel routing.

## 3.2.1 Basic steps

The proposed method for over-the-cell channel routing consists of three phases which are performed in a sequence different from that of [CL88]: (i) initial terminal selection, (ii) over-the-cell routing by a new heuristic, (iii) routing within the channel.

### 3.2.1.1 Initial terminal selection

Nets having terminals on both sides of the channel should have at least one connection across the channel. Thus, if a net having multiple terminals on one side routed over the cell, it leaves a problem of selecting a net segment with two terminals of this net one from the top and other from the bottom of the channel. Appropriate choice of these net segments which minimize the channel density is NP-hard, and was accomplished earlier with a heuristic procedure [CL88]. In our work, we first select initial terminals by suitable heuristic which attempts to minimize the channel width and then go for deciding the over-the-cell candidates.

Definition: The congestion of a column r is the number of nets passing through that column and is denoted by  $c_r$ . The density of a channel is the maximum of  $c_r$ 's over all columns.

Given a net v, let there be p terminals on the top side of the channel occupying column positions  $v_i^t$  for i=1,...,p (t stands for top) and q terminals on the bottom side of the channel occupying the column positions  $v_j^b$  for j=1,...,q (b stands for bottom). In over-the-cell channel routing, as the terminals appearing in the top (bottom) side are connected over the cell, here the problem is to select a suitable terminal from the top and another from bottom for connecting the two sets.

For each pair of terminals  $(v_i^1, v_j^b)$  we now define the cost function  $w_{ij}$  as:  $w_{ij} = \sum_{r=1}^{n} \delta_r \cdot (b_r^2 + c_r) \text{ where } r \text{ stands for column number,}$

$\delta_r = 1$ , if r lies within the interval  $[v_i^t, v_i^b]$  and 0 otherwise;

$b_r = \text{number of occupied tracks in the } r\text{-th column by net segments which are selected so far for routing through the channel.$