M.Tech.(Computer Science) Dissertation Series

## Partial Reconfiguration in Floorplanning of FPGAs with Heterogeneous Resources

A dissertation submitted in partial fulfillment of the requirements for the M.Tech.(Computer Science) degree of the Indian Statistical Institute

Under the supervision of

## Dr. Susmita Sur-kolay

$\mathbf{B}\mathbf{y}$

## Megha Sangtani Roll No : CS0609

Indian Statistical Institute

203, B.T. Road

Kolkata-700108

## Indian Statistical Institute

#### Certificate of Approval

This is to certify that the thesis entitled **Partial Reconfiguration in Floorplanning** of FPGAs with Heterogeneous Resources submitted by Megha Sangtani towards partial fulfillment for the degree of M. Tech. in Computer Science at Indian Statistical Institute, Kolkata, embodies the work done under my supervision.

**Dr. Susmita Sur-Kolay** ACMU, ISI, Kolkata

Date:

### Acknowledgment

It is with great reverence that I wish to express my deep sense of gratitude to my guide Dr. Susmita Sur-Kolay, Associate Professor, Advanced Computing and Microelectronics Unit, Indian Statistical Institute, Kolkata, for her valuable guidance, suggestions and encouragement to carry out the work and the meticulous care with which she helped me throughout preparation of the report. I have benefited a great deal because of her deep insight.

I express my sincere thanks to Ms. Pritha Banerjee (Research Scholar), Advanced Computing and Microelectronics Unit, for her valuable inspiration and help throughout this work. I am also very thankful to all the teachers for the valuable feedback. I also express my thanks to my friends and my classmates for their help.

I am short of adequate words in expressing my heartiest thanks to my parents who are the constant of encouragement to me. It is the loving care and understanding of them, which has placed me at the present level of academic career. In the last, but not the least, I want to thank my almighty GOD.

### Abstract

Modern Field Programmable Gate Arrays (FPGA) with heterogeneous resources with millions of gates, have been widely used for prototyping large design nowadays. However, large designs might not fit in one FPGA chip. Since, all the modules of a given application might not be active at the same time, the FPGA resources may remain unutilized during the execution of the application. In such applications partial reconfigurability of FPGA helps, where a part of the FPGA chip remains active and inactive part of FPGA could be replaced by another set of modules. Given a schedule of instances with each instance having a set of active modules and their connectivity, a global floorplanning method is essential to reduce the partial reconfiguration overhead while optimizing the performance of the design. This can be done by fixing the position and shapes of common modules across all instances at the same location, while the rest of the temporary modules can be swapped in and out of the board. Modern FPGAs have different types of resources like CLBs, RAMs and Multipliers. This heterogeneity in resources makes floorplanning in FPGA difficult, especially when the design to be implemented is large. In this dissertation we propose a unified global floorplan topology generation method to obtain the fixed positions for the common modules across all instances such that resource requirement of rest of the modules are still satisfied and the total wirelength of the floorplan is minimized.

# Contents

| 1        | Intr                                          | oduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1                                                                                              |

|----------|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

|          | 1.1                                           | Partial Reconfiguration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2                                                                                              |

|          | 1.2                                           | FPGA Physical Design Cycle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2                                                                                              |

|          | 1.3                                           | Scope of this thesis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3                                                                                              |

| <b>2</b> | Par                                           | tial Reconfiguration on FPGA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <b>5</b>                                                                                       |

|          | 2.1                                           | Target Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 6                                                                                              |

|          | 2.2                                           | Problem Formulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 6                                                                                              |

|          |                                               | 2.2.1 Floorplanning Problem for heterogeneous FPGAs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 7                                                                                              |

|          |                                               | 2.2.2 Partial Reconfiguration Problem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 8                                                                                              |

|          | 2.3                                           | Existing Approaches                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 8                                                                                              |

|          |                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                |

| 3        | Pro                                           | posed Method                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 10                                                                                             |

| 3        | <b>Pro</b><br>3.1                             | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | <b>10</b><br>11                                                                                |

| 3        |                                               | Preliminaries                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                |

| 3        | 3.1                                           | Preliminaries                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 11                                                                                             |

| 3        | 3.1<br>3.2                                    | Preliminaries                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 11<br>12                                                                                       |

| 3        | 3.1<br>3.2                                    | Preliminaries       PHASE I- Linear arrangement of Modules       PHASE I- Linear arrangement of Modules         PHASE II- Unified floorplan topology generation       PHASE II- Unified floorplan topology generation         3.3.1       Generation of Module Shapes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 11<br>12<br>14                                                                                 |

| 3        | 3.1<br>3.2                                    | Preliminaries       PHASE I- Linear arrangement of Modules       PHASE I- Linear arrangement of Modules         PHASE II- Unified floorplan topology generation       PHASE II- Unified floorplan topology generation         3.3.1       Generation of Module Shapes         3.3.2       Node Sizing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 11<br>12<br>14<br>15                                                                           |

| 3        | 3.1<br>3.2                                    | Preliminaries       PHASE I- Linear arrangement of Modules       PHASE I- Linear arrangement of Modules       PHASE II- Unified floorplan topology generation       PHASE II- Unified floorplan topology generation <td>11<br/>12<br/>14<br/>15<br/>15</td> | 11<br>12<br>14<br>15<br>15                                                                     |

| 3        | <ul><li>3.1</li><li>3.2</li><li>3.3</li></ul> | Preliminaries                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <ol> <li>11</li> <li>12</li> <li>14</li> <li>15</li> <li>15</li> <li>16</li> </ol>             |

| 3        | <ul><li>3.1</li><li>3.2</li><li>3.3</li></ul> | Preliminaries                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <ol> <li>11</li> <li>12</li> <li>14</li> <li>15</li> <li>15</li> <li>16</li> <li>17</li> </ol> |

|   | 3.4.4 Postprocessing for reallocation of resources | 20 |

|---|----------------------------------------------------|----|

|   | 3.5 Time Complexity                                | 21 |

|   |                                                    |    |

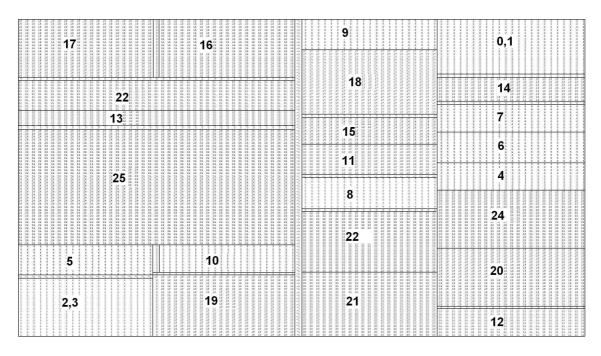

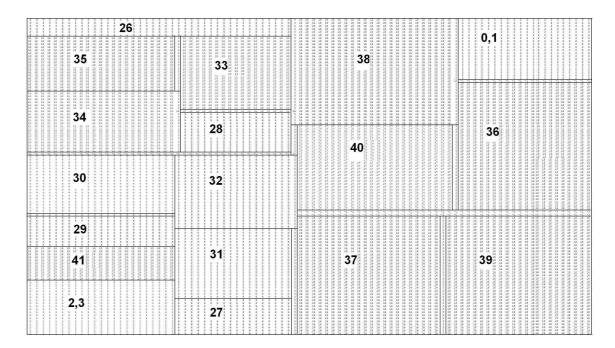

| 4 | An Example                                         | 23 |

| 5 | Experimental Results                               | 29 |

| 6 | Concluding Remarks and Future Work                 | 39 |

# Chapter 1

# Introduction

Field Programmable Gate Arrays (FPGAs) are programmable integrated circuits. It consists of array of *Configurable Logic Blocks* (CLBs) with wires of different lengths layed out in horizontal and vertical channels. CLBs consist of Look-up tables and flip flops which can be programmed to implement a design. A given digital design is implemented as a netlist of CLBs and the connectivity is implemented by connecting required wires on the vertical and horizontal channels with the help of switchboxes present at every crosspoint of horizontal and vertical channels. An FPGA is programmed using a configuration file which contains the place and route information to implement the design. To reprogram an FPGA, i.e., to implement a different application, all that is required is downloading of a new or different configuration file to the FPGA chip. Applications are often mapped to FPGAs using a four step process: design entry, technology mapping, physical placement and routing. Then a configuration file is downloaded to program the FPGA. Recent advancements in fabrication technology and device architecture have resulted in tremendous growth in FPGAs, both in terms of density and performance. Earlier FPGAs used to have only CLBs for mapping the logic but modern FPGAs have other resources also on the board like RAMs, Multipliers, DSPs, microprocessor cores along with array of CLBs. Heterogeneity in resources makes the mapping of logic on FPGA board more difficult, which requires additional steps in the mapping process.

### **1.1** Partial Reconfiguration

The obvious benefit of FPGA is that the functionality on it can be changed and updated at some time in the future. The FPGA can be completely reprogrammed with new logic. For many users, this still is not't enough. If one wants to change the logic within a part of an FPGA without disrupting the entire system, it can be done by partially reconfiguring the application on a device. Partial reconfiguration is a design process, which allows a limited, predefined portion of an FPGA to be reconfigured while the remainder of the device continues to operate. Using partial reconfiguration, the functionality of a single FPGA can be increased, allowing for fewer, smaller devices than would otherwise be needed. Partial reconfiguration is useful for systems with multiple functions that can time-share the same FPGA device resources. In such systems, one section of the FPGA continues to operate, while other sections of the FPGA are disabled and reconfigured to provide new functionality. This is analogous to the situation where a microprocessor manages context switching between software processes. In the case of partial reconfiguration of an FPGA, however, it is the hardware not the software that is being switched.

## 1.2 FPGA Physical Design Cycle

First of all the design to be programmed on FPGA is defined in terms of design equations in some high level language like VHDL. These design equations are mapped on to the resources available on the FPGA board as a netlist of logic blocks in technology mapping phase. The design is partitioned in components based on their connectivity and then the location of the components are determined on the FPGA board in placement phase. After placement, routing of the wires, which are connectivity between the components, is done by determining switch boxes through which the wire should go. Finally, the design is programmed on the FPGA board.

Earlier Floorplanning on FPGA was generally ignored in the physical design cycle as the design were comparatively smaller and the resources on FPGA were homogeneous, namely CLBs. With the advent of technology, modern FPGAs are capable of implementing large

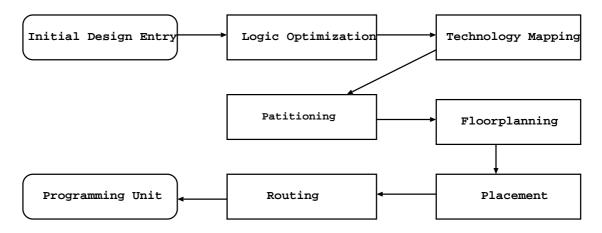

Figure 1.1: FPGA Design Cycle

designs with millions of gates. This has made floorplanning an important step in the design flow. As shown in Figure 1.1 the floorplanning is done prior to the placement and route phase in the FPGA physical design cycle. In the context of partial dynamic reconfiguration too, floorplanning has become an essential step. Formally, it is the process of determining the location of the modules on the chip such that no two modules overlap and there is enough space left to complete the interconnections. The input for floorplanning is a set of modules and a netlist describing the connectivity of the modules. At this stage the estimate for the required areas for different modules are available, but their exact dimension can vary in a range. As the result of floorplanning, we get a floorplan, which describes the exact location and size of each module on the chip.

#### **1.3** Scope of this thesis

In this thesis, an deterministic floorplan topology generation method is proposed for partial reconfiguration of a set of designs at different instances which minimizes the partial reconfiguration overhead, while optimizing the performance of the designs. The rest of the thesis is organized as follows.

In chapter 2, the floorplanning problem in the context of partial reconfiguration is introduced. Chapter 3 describes the method proposed. The method is demonstrated with an example in Chapter 4. The experimental results on a set of benchmarks are given in Chapter 5. Concluding remarks and future work appear in Chapter 6.

## Chapter 2

## Partial Reconfiguration on FPGA

Recent Field Programmable Gate Array (FPGA) architectures like Xilinx' Virtex series allow partial dynamic reconfiguration. This means, inactive parts of a design implemented on FPGA hardware could be replaced by other designs while the remaining part of FPGA is still executing some other operations. So, partial reconfiguration helps executing a large application to be executed in the same piece of hardware by swapping in and out parts of the design, even if it does not fit completely on the same chip. Alternatively, a set of independent application can run on the same piece of FPGA hardware utilizing the FPGA resources effectively. This definitely, incurs an additional partial reconfiguration overhead each time a new part is swapped in and out of the FPGA hardware. Hence an appropriate scheduling of task/application/design is necessary to reduce the partial reconfiguration overhead such that common tasks/designs need not be swapped in and out again and again. Moreover, at any instance of time, the tasks should be mapped onto the FPGA such that new tasks in the schedule can be fitted onto the board contiguously. It may be possible that, some tasks are already mapped on the board in such a way that, even though there are enough resources that satisfy the requirements of scheduled tasks at that instance, they are not contiguous. As Modern FPGAs are heterogeneous in nature with preplaced blocks like RAM, Multipliers along with sea of CLBs, the mapping of new tasks at any instance becomes more complex. The whole chip may have to be reconfigured which defeats the whole purpose of partial reconfigurability feature of FPGA. Even if it is possible to map all the active tasks at any instance of time on to the FPGA satisfying its resource requirement contiguously, does this mapping meet the required performance specification? In order to obtain a globally optimized floorplan of active tasks at different instance of time that also minimizes partial reconfiguration overhead, the floorplanning problem is defined in the context of partial reconfiguration.

#### 2.1 Target Architecture

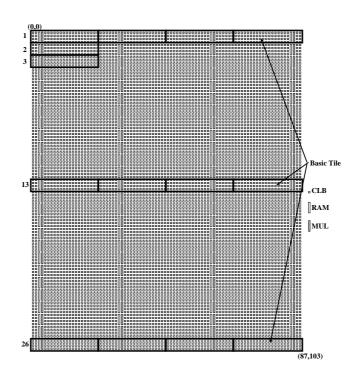

Modern FPGAs are heterogeneous with different kinds of resources like CLBs, RAMs, Multipliers (MUL) etc., while earlier FPGAs used to have only CLBs. Fig. 2.1 shows a Xilinx Spatran-3 FPGA where the CLBs are arranged in columns interleaved with columns of RAM-MUL pair at certain intervals. Each small square represents a CLB. A pair of shaded rectangular block spanning 4 rows of CLBs represents a pair of RAM and MUL. We use this architecture, though the described method is applicable on other architectures as well.

**Definition 1** Let W and H be the width and height of a target FPGA architecture, where the units are the width and height of a CLB respectively. A coordinate system (0, 0, W, H) with top-left corner at (0, 0) and bottom-right corner at (W, H) is assumed for the given chip.

In Figure 2.1, it is (0, 0, 87, 103) Each resource on the architecture is identified by its coordinate position (x, y), where  $0 \le x \le W$  and  $0 \le y \le H$ . Henceforth, the term target FPGA architecture and target chip will be used synonymously.

#### 2.2 Problem Formulation

First, the basic terminology is given below.

**Definition 2** Modules and Signal nets: Let  $M = \{m_1, m_2, ..., m_n\}$  be a set of n distinct modules. Let  $S = \{s_1, s_2, ..., s_q\}$  be a set of q signal nets. Each signal net  $s_i \in S$  is associated with a set of distinct modules  $M_{s_i} = \{m_j \mid m_j \in M\}$ , and the set S is called a netlist. If  $M_{s_i}$  $= M_{s_j}$ , then the two distinct signal nets  $s_i$  and  $s_j$  connect the same set of modules.

**Definition 3** Resource Requirement Vector [?]: For a module m, a 3-tuple vector  $R_m = (m_{clb}, m_{ram}, m_{mul})$  represents the number of CLBs, RAMs and MULs required by module m.

Figure 2.1: Spartan-3 XC3S5000 FPGA Architecture

#### 2.2.1 Floorplanning Problem for heterogeneous FPGAs

Given a target architecture (0, 0, W, H) with its resource locations, a design consisting of (a) a set of soft (flexible in shape) modules M, (b) the resource requirement vectors  $R_{m_i}$  for each  $m_i \in M$ , and (c) the netlist S,

find a floorplan by assigning a connected region  $(x_{min}, y_{min}, x_{max}, y_{max})$  to each module on the target architecture such that

(i)  $0 \le x_{min} \le x_{max} \le W$  and  $0 \le y_{min} \le y_{max} \le H$ ,

(ii) region for no two modules overlap with each other,

- (iii) for each module  $m_i$ , the resources in its region satisfies  $R_{m_i}$

- (iv) a certain cost function is optimized.

A floorplan is said to be *feasible* if it satisfies all three conditions (i), (ii) and (iii). The cost function to be optimized is typically the wirelength [7, 8]for which the popular metric HPWL (half-perimeter wirelength), i.e.,the sum of the semi-perimeter of the bounding boxes for each net, is used. In the absence of information at this stage, the net terminals on a soft module are assumed to be at the center of the module. This bounding box cost has also been

extensively used as a FPGA placement metric [6]. The problem formulation as stated above is a generalization of that given in [9, 10] and as such is NP-hard. Like most of the prior works on FPGA heterogeneous floorplanning [9, 11], we also consider HPWL as the objective function.

#### 2.2.2 Partial Reconfiguration Problem

**Definition 4** Static and Dynamic modules: Given a schedule of instances, modules which are common and remains active in all instances are called static modules. The rest of the modules which are swapped in and out of an instance, are called dynamic modules.

The floorplanning problem for partial reconfiguration is defined as follows: In a given schedule, let there be k instances  $I_1, I_2, \dots I_k$ . Let  $s_1, s_2, \dots s_m$  be m common modules that remain active in all instances. For each  $I_i, 1 \leq i \leq k$ , let there be  $n_i$  modules  $d_{i1}, d_{i2}, \dots d_{in_i}$ . The connectivity of the modules in each instance is also given. The objective is to give a floorplan of all modules across all instances such that

(i) the resource requirement of each module is satisfied in each instance,

- (ii) the location and shape of each static module is same across all instances,

- (iii) the half-perimeter wirelength (HPWL) of netlist for all instances is minimized.

As in any floorplanning problem, we consider sum of HPWL of each instance as the objective function to be minimized in the context of partial reconfiguration.

### 2.3 Existing Approaches

There are only a few floorplanning approaches for FPGA. Most of them use probabilistic techniques like simulated annealing with sequence pair representation of the floorplan. They start with some initial floorplan topology and perform some perturbations like complement the cut lines or swapping of modules to get a new floorplan and this floorplan is accepted only if it is better than the previous floorplan, otherwise it is rejected with a probability which depends on the number of iterations done so far. In this way the initial floorplan plays an important role in this method and if the initial floorplan is not good then it may take large number of iterations to get the optimal floorplan. Singhal and Bozorgzadeh have introduced a new multi layer sequence pair representation based floorplanner in their paper [3] which maximizes the overlap of common components of multiple designs thereby reducing reconfiguration overhead and guarantees a feasible floorplan with minimum area packing. The main drawback of this method is the long execution time because of probabilistic nature of simulated annealing. The commercial tool like Xilinx' Planahead [15] requires manual placement of the common modules beforehand, and then the rest of the modules are placed. This method is also based on simulated annealing.

To overcome the long execution time of simulated annealing based approach and yet arrive at a global floorplan such that the partial reconfiguration is minimized and performance of floorplan of each instance in optimized, a fast deterministic method is proposed. As in case of [3], this method places the common modules with same shape across all instances at a specific position on the chip so that they need not be reconfigured again and again, thereby reducing reconfiguration overhead. Also the remaining modules are placed in such a way that the wirelength (HPWL) is minimized globally. Unlike the method in [3], where sequencepair is used as floorplan representation under simulated annealing based moves, the proposed method uses slicing tree [1] representation and node sizing for topology generation. Fekete et. al have proposed an alogorithm for optimal free space management and routing conscious dynamic placement for reconfigurable devices in their paper [12]. They find an optimal feasible communication - conscious placement which minimizes the total weighted mahattan distance between new module and already placed modules.

# Chapter 3

# **Proposed Method**

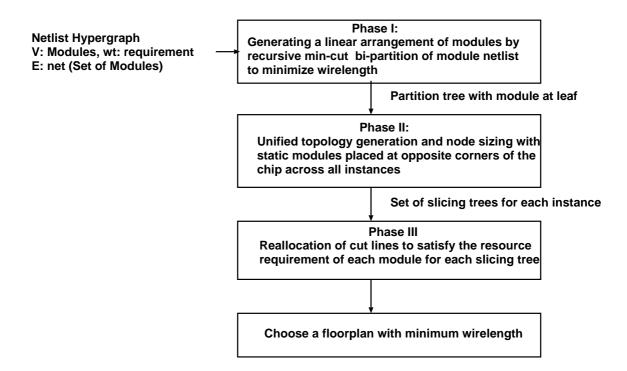

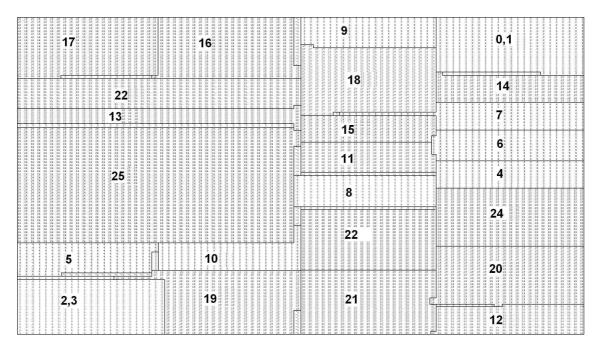

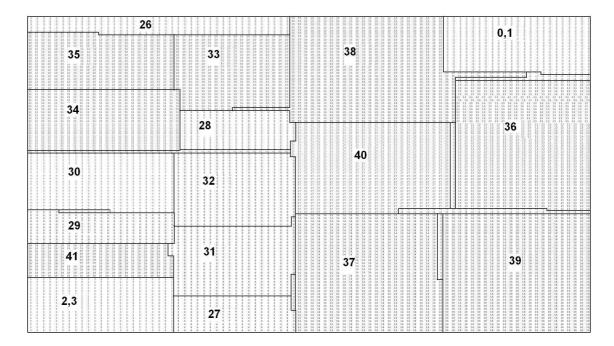

The goal of the proposed method is to design a fast yet effective unified floorplan topology such that static modules occupy same position at every instance and still the performance is optimizes. Our method consists of three phases: (i) creating a linear arrangement of modules for each instance with the fixed position of static modules, (ii) slicing tree topology generation for floorplan and, (iii) realization of the floorplan using actual resource requirements of the modules.

In the first phase, we obtain a linear arrangement of modules to minimize the sum of the total wirelengths such that heavily connected modules come closer to each other.

In the second phase a list of global slicing tree topologies is generated for each instance with the positions of static modules fixed at the bottom left and top right corners of the floorplan.

In the third phase, we group the set of slicing trees, obtained in the second phase, on the basis of shapes of static modules. For each of the slicing tree in each group, a rectangular region is assigned to every module, which respects the cut direction and the actual resource requirement of the modules.

Finally, one floorplan from each instance is chosen such that the total wirelength is minimum.

Figure 3.1: Flow of the Proposed Method

#### **3.1** Preliminaries

For modules with homogeneous resource requirement, the area of a module could be considered for generation of shapes, which can be later used for node sizing in traditional topology generation, when floorplans are represented as slicing trees [1]. For heterogeneous resource requirements, where each resource type have specific location on the board, shapes can not be generated from the resource requirement vector. Thus, *basic tile*, an uniform entity is defined to compute the resource requirement of each module, which could be easily adapted for generation of shapes during node sizing.

**Definition 5** Basic Tile: A Basic FPGA Tile  $A = (a_{clb}, a_{ram}, a_{mul})$  is a 3 tuple vector composing of the minimum number of CLBs, RAMs, MULs that constitute a basic unit which can be repeated horizontally and vertically to cover all the rows and columns of a given FPGA architecture.

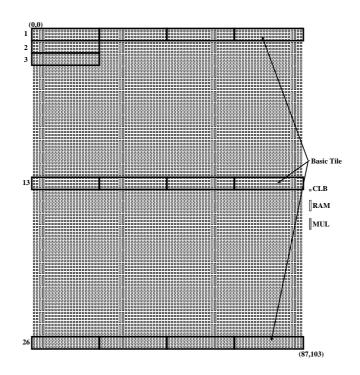

The given architecture is thus composed of, say,  $T_w \times T_h$  basic tiles arranged in h rows and w columns. In Fig. 3.2, The basic tile A = (80, 1, 1) consists of  $20 \times 4$  CLBs , 1 RAM and 1

Figure 3.2: Spartan-3 XC3S5000 FPGA Architecture, tessellated with a basic tile, indicated by a rectangle of 4 rows and 20 columns of CLBs and 1 pair of RAM-MUL blocks

MUL. The entire architecture (Spartan-3) in Fig. 3.2 can be covered by 26 rows and 4 columns of basic tile A.

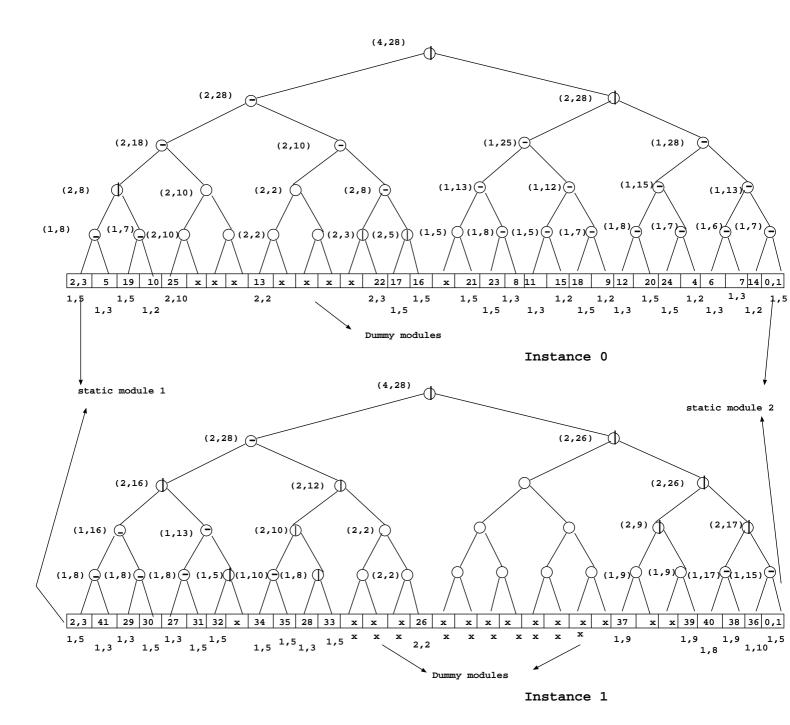

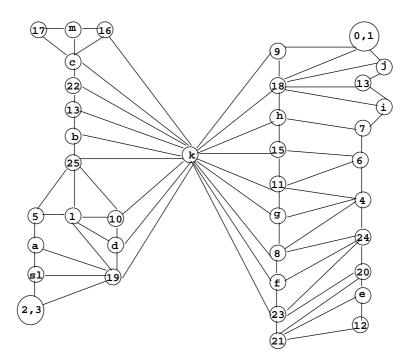

#### **3.2 PHASE I-** Linear arrangement of Modules

To minimize the wire length of the feasible floorplan we obtain a linear arrangement of modules such that heavily connected modules come closer to each other. Finding an optimal linear arrangement of modules of a netlist is NP-hard. Thus we use a min-cut bi-partitioning heuristic recursively till there is a single module in each partition. The recursive bi-partitioning generates a binary tree at every step of recursion, which is called a *decomposition* or *partition* tree. The left to right order of the modules at the leaves is considered to be a good linear arrangement [5]. The partition tree generated in this phase is the baseline of slicing tree generation in the next phase.

We use state-of-the-art bi-partitioning tool hMetis [13] for partitioning hypergraphs. The netlist of modules is best represented by an hypergraph H = (V, E). Each vertex  $v \in V$  corresponds to a module  $m_i$ ,  $i = 1, 2, \dots n$ . An hyperedge  $e = \{v_1, v_2, \dots v_p\} \in E$  corresponds to a signal net connecting the set of modules  $\{v_1, v_2, \dots v_p\}$ . If there are more than one such sets, then the total number of such set is considered to be the weight of that hyperedge e. The minimum number of tiles required by a module m is computed from the size of the *basic tile* Aand the resource requirement vector  $R_m$ . This is given as the weight of the vertex corresponding to module m. The tool hMetis produces a balanced min-cut partitioning of this hypergraph.

Static modules should have the same shape and location across all instances. It is beneficial to place all the static modules to the extreme corners of the floorplan, so that, we get the largest continuous space in the middle of the chip to place the rest of the dynamic modules contiguously. We generate the slicing tree of the floorplan in the second phase from the partition tree obtained in this phase. The objective of placing the static modules to the corners of a floorplan led to the following observation.

**Observation 1** In a slicing tree representation of a floorplan, the modules at left most and right most leaves of the tree always correspond to the two opposite corners of the floorplan.

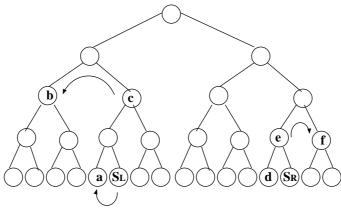

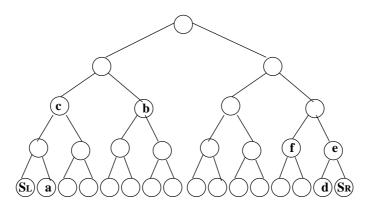

From Observation 1, if we can place the static modules at extreme ends of the partition tree, the static modules will definitely be on the opposite corners on the floorplan. To generate a partition tree with this constraint we do the following. First we extract the static modules and the corresponding netlist from the given schedule. then we bi-partition the static modules into two groups  $S_L$  and  $S_R$  and call each of them a *super module*. Now we have two static super modules and some dynamic modules along with the netlist for each instance. This netlist of modules is bi-partitioned recursively until each partition contains at most one module/super module per partition. In the first level of recursive bi-partitioning, we force  $S_L$  and  $S_R$  to be in different partitions, so that, they can be pushed to extreme left and right positions during the further recursive partitioning. As swapping of left and right partition in a bi-partition do not affect the min-cut, two partitions can interchange their position without affecting the cut. During recursive bi-partitioning the left and right partitions are swapped in such a way that partitions having static super modules are always pushed to the extreme left and extreme right of the linear arrangement of the modules obtained at leaf level. The swapping of partitions with static super modules to the leftmost and the rightmost leaf of the partition tree is shown

**Before Swapping**

After Swapping

Figure 3.3: Swapping of static super modules to extreme ends of the partition tree; the arrow shows the partitions to be exchanged

in Fig. 3.3.

Thus we get one partition tree for each instance where the static modules are at the extreme left and right leaves.

### 3.3 PHASE II- Unified floorplan topology generation

In this step a set of sliceable floorplan topologies is generated for each instance by appropriate horizontal and vertical node sizing starting from a set of possible shapes (in terms of tiles) of each module.

#### 3.3.1 Generation of Module Shapes

A list  $D = \{(w_1, h_1), (w_2, h_2), \dots, (w_t, h_t)\}$  of irredundant shapes of a module m, is a list of t possible shapes of m, where  $(w_i, h_i)$  denotes the width and height of  $i^{th}$  shape of m in terms of basic tiles. D is said to be irredundant if each individual  $w_i$  and  $h_i$  are distinct.

By making individual  $w_i$  and  $h_i$  distinct, a shape with smaller height is chosen from two implementations with same width. Thus the inferior shape is always gets eliminated. A set of possible irredundant rectangular shapes for  $m_i$  is generated by factorizing  $T_{m_i}$ . As we are considering only rectangular shapes there may not be many choices such that  $width \times height =$  $T_{m_i}$ . A few more shapes are generated by factorizing all integers from  $T_{m_i}$  to the smallest composite integer which is greater than  $T_{m_i}$ .

#### 3.3.2 Node Sizing

A subtree rooted at an internal node p corresponds to a sub-floorplan. The sub-floorplan at p is generated by joining  $(w_i, h_i) \in D_l$  and  $(w_j, h_j) \in D_r$  vertically or horizontally, where  $D_l$  and  $D_r$  are  $i^{th}$  shape of left child (left sub-floorplan) and  $j^{th}$  shape of right child (right sub-floorplan) of p. If p is the parent of leaves then the left and right sub-floorplans are the shapes of the modules themselves.

Vertical Cut: We use the vertical node sizing algorithm of [1] to generate a sub-floorplan with vertical cut. Let  $D_l = \{(w_{l_1}, h_{l_1}), (w_{l_2}, h_{l_2}), \dots, (w_{l_s}, h_{l_s})\}$ , with  $|D_l| = s$  and  $D_r = \{(w_{r_1}, h_{r_1}), (w_{r_2}, h_{r_2}), \dots, (w_{r_t}, h_{r_t})\}$ , with  $|D_r| = t$ , be the set of possible irredundant shapes of the left sub-floorplan/module and the right sub-floorplan/module respectively, of a node in partition tree.  $D_l$  is sorted such that,  $w_{l_1} < w_{l_2} < \dots < w_{l_s}$  and  $h_{l_1} > h_{l_2} > \dots > h_{l_s}$ .

$D_r$  is also sorted as above. If  $(w_{l_i}, h_{l_i})$  and  $(w_{r_j}, h_{r_j})$  are merged vertically, the resultant floorplan size becomes  $(w_{v_k}, h_{v_k}) = (w_{l_i} + w_{r_j}, max(h_{l_i}, h_{r_j}))$ . The number of resultant irredundant shapes is at most s + t - 1 [1].

Horizontal cut: To merge sub floorplans using horizontal cut, we use the same irredundant lists  $D_l$  and  $D_r$  as described above. The lists are sorted in increasing order of height and decreasing order of width i.e.  $h_{l_1} < h_{l_2} < \cdots < h_{l_s}$  and  $w_{l_1} > w_{l_2} > \cdots > w_{l_s}$

Merging  $(w_{l_i}, h_{l_i})$  and  $(w_{r_i}, h_{r_i})$  by a horizontal cut the resultant size of the floorplan be-

comes  $(w_{v_k}, h_{v_k}) = (max(w_{l_i}, w_{r_j}), h_{l_i} + h_{r_j})$ . As in case of vertical cut the number of resultant irredundant shapes is at most s + t - 1.

#### 3.3.3 Generation of Slicing Trees

A set of slicing tree is generated for the decomposition or partition tree obtained in PHASE -I by appropriate shape generation and node sizing as described above. Each leaf node of the tree corresponding to a module contains a list of possible shapes, i.e., (width, height) pair in terms of tiles. For all instances, the corresponding partition trees are traversed simultaneously bottom-up, level by level, generating a set of irredundant sub-floorplans by combining the available shapes of its left and right children with vertical or horizontal cut. Whenever a static super module is combined with its neighbouring dynamic module by a particular cut, the shape generated at parent must also be irredundant. To generate irredundant shapes at the parent node, a particular shape of static super modules may be thrown out in some of the instances when combined with its neighboring dynamic modules by a cut. We discard such shapes of static modules from all the instances when a particular shape is eliminated from any of the instances so that the list of shapes of static modules remain same for all the instances. If at any level, we end up with an empty list of shapes for any of the static super modules then we can directly report that floorplanning is not possible on the FPGA board for the linear arrangement of modules/super modules obtained in the first phase, and may iterate with another linear arrangement.

At the end of this phase we get a set of slicing trees for each of the instances with static super modules at two opposite corners of the floorplan. The list of shapes (width, height) generated at root may not fit the target FPGA chip when the shapes are considered in terms of tiles. The target chip is  $4 \times 26$  tiles. We consider only those slicing trees with root shape of width between 3 and 6 as there is a high possibility of getting a feasible floorplan on this target board in the third phase.

### 3.4 PHASE III - Realization of Slicing Trees on the chip

For every slicing tree generated in the previous step, now we assign coordinate position to each module. We allocate a rectangular region which satisfies the CLB requirements.

#### 3.4.1 Allocation of Rectangular Region to a Module

Each slicing tree is traversed top down and a rectangular region  $(x_{min}^{p}, y_{min}^{p}, x_{max}^{p}, y_{max}^{p})$  is assigned to every node p using the cut direction and the number of CLBs required at p. Let the region allocated to some node p contains  $r_{clb}$  rows and  $c_{clb}$  columns of CLBs. If the CLB requirements at node p, its left child l and its right child r are  $p_{clb}$ ,  $l_{clb}$  and  $r_{clb}$  respectively. If the p represents the vertical cut, the number of clb columns allocated to p is  $p_{col}$  and number of clb rows allocated to p is  $p_{row}$  then the rectangular box assignment for l and r is done by the following equations : -

Let the rectangular assigned to l and r are  $(x_{min}^{l}, y_{min}^{l}, x_{max}^{l}, y_{max}^{l})$  and  $(x_{min}^{r}, y_{min}^{r}, x_{max}^{r}, y_{max}^{r})$  respectively. Let the clb rows and columns allocated by l and r are  $l_{row}$ ,  $l_{col}$  and  $r_{row}$ ,  $r_{col}$ .

For a horizontal cut at p,

$$\begin{split} l_{col} &= l_{clb}/p_{row}, \\ r_{col} &= r_{clb}/p_{row}, \\ x_{min}{}^{l} &= x_{min}{}^{p}, y_{min}{}^{l} &= y_{min}{}^{p}, \\ x_{max}{}^{l} &= x_{min}{}^{p} + l_{col} - 1, y_{max}{}^{l} &= y_{max}{}^{p}, \\ x_{min}{}^{r} &= x_{max}{}^{p} - r_{col} + 1, y_{min}{}^{r} &= y_{min}{}^{p}, \\ x_{max}{}^{r} &= x_{min}{}^{p}, y_{max}{}^{r} &= y_{max}{}^{p}. \\ For a vertical cut at p, \\ l_{row} &= l_{clb}/p_{col}, \\ r_{row} &= r_{clb}/p_{col}, \\ x_{min}{}^{l} &= x_{min}{}^{p}, y_{min}{}^{l} &= y_{min}{}^{p}, \\ x_{max}{}^{l} &= x_{max}{}^{p}, y_{max}{}^{l} &= y_{min}{}^{p} + l_{row} - 1, \\ x_{min}{}^{r} &= x_{min}{}^{p}, y_{min}{}^{r} &= y_{max}{}^{p} - r_{row} + 1, \\ x_{max}{}^{r} &= x_{max}{}^{p}, y_{max}{}^{r} &= y_{min}{}^{p}. \end{split}$$

As a convention, the vertical cut line is positioned by counting the columns from left to

right for the left child and right to left for the right child. Silmilarly for horizontal cut, it is positioned by counting the rows from bottom to top for the left child and top to bottom for the right child. This may generate a overlapping rectangular region in the middle of the two rectangles assigned to the left and right child. We allocate the CLBs required by a module to the non overlapping region of the rectangles assigned to the corresponding module. The remaining CLB requirement of each module, called *deficit*, has to be allocated either to the overlapping rectangle or to the neighboring rectangles. By positioning the cutlines as described above, free rectangular region might get generated too in the middle. Thus, three types of rectangular region is created by positioning of cut lines. (i) non overlapping part of rectangle assigned to a module either with no free CLBs within it or with some free CLBs in it (ii) overlapping rectangle, where conflicts for CLB requirements of more than one module needs to be resolved, (iii) free rectangles created at the middle due to the convention followed to assign rectangles to a module. The deficit (if any) of each module is satisfied during post processing described in Section 3.4.4

#### 3.4.2 Pruning the Trees

While allocating the rectangular regions to modules in different instances, their RAM/MUL requirements are not considered. So we cannot say anything about whether RAM/MUL requirement of modules will be satisfied within rectangular region allocated.

**Definition 6** Major Violation : If a module has RAM/MUL requirement and has been assigned the rectangular box such that no RAM/MUL column going through it, then the module is said to have the major violation.

We discard all the floorplans from each instance in which any module has major violation. The intuition behind such floorplans is, if any module has been assigned such a rectangular box through no RAM?MUL column is going through and it has RAM/MUL requirements, then it would be difficult to borrow the RAM/MULT from neighboring modules if they have excess of them and then adjusting the shape of the affected modules. This may make the shapes of the modules very bad so we avoid such floorplans.

Figure 3.4: Graph generated for selecting set of trees in a group

#### 3.4.3 Grouping the floorplans

After getting the set of floorplans for each instance, the question arises which set of the trees to be considered together for global floorplan so that the objective of the partial reconfiguration can be achieved, i.e. the same shapes for the static modules across all instances.

For this purpose, we calculate the aspect ratios of static modules/supermodule in each floorplan for each instance(after rectangular region allocation). We group the floorplans from each instance on the basis of nearly equal aspect ratios of the static module/super module such that a group contains at least one floorplan from each instance of the design. If there is more than one floorplan for an instance in the group, we need to select a single floorplan for that instance. For this, we define the following for the slicing topology corresponding to each floorplan.

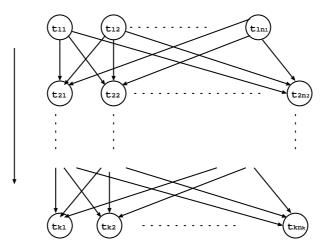

**Definition 7** Hamming distance between two slicing trees: Let a and b be the strings representing the level order traversal of nodes from the root till one level above the leaves of the two slicing trees respectively, with horizontal cut represented as 0 and vertical cut represented as 1. Let  $l = min\{length(a), length(b)\}$  and the length of the longer string be truncated till l from right. Then the hamming distance between these trees is the number of ones in aXORb.

This basically measure the closeness among two slicing trees in terms of slicing topology. In the context of partial reconfiguration, a schedule implies the ordering of the instances on

Figure 3.5: Network flow graph for reallocation of resources

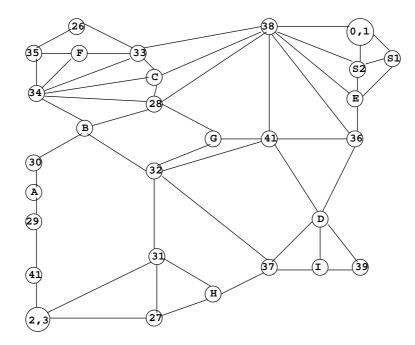

the time line. To have same shapes of static from one instance to the consecutive one, the change in slicing tree must be minimum. Let,  $T_1 < T_2 < \cdots T_k$  be the k trees of k instances in a given schedule, where  $T_i < T_j$  indicates that  $i^{th}$  instance is executed prior to  $j^{th}$  instance in the schedule. So,  $T_1$  and  $T_k$  are the trees from the first and the last instances in the schedule. We formulate a method for selecting slicing trees consecutively from each instance as follows. Let G = (V, E) be a directed graph with  $v \in V$  corresponding to the trees in a group. There exists a weighted edge  $e \in E$ , between  $u, v \in V$ , if uandv corresponds to the slicing trees in consecutive instances. The weight is the hamming distance between u and v. If there are k instances, we find a minimum weighted k-length path starting from the node corresponding to  $T_1$  to  $T_k$ . The floorplans corresponding to the trees in the minimum weighted path is selected as the final floorplans for a group.

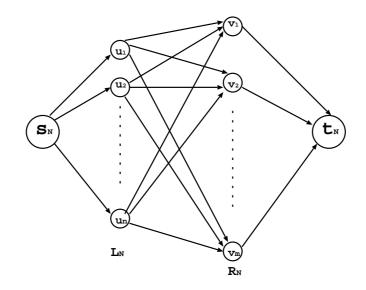

#### **3.4.4** Postprocessing for reallocation of resources

The set of floorplans chosen for each instance in a group have static modules with nearly equal aspect ratios but not exactly the same shape. We consider all pair of shapes, taking one from the list of  $S_L$  and the other from  $S_R$  and use this shape pair for static modules in all instances and reallocate CLBs of those dynamic modules that are either generating overlap with the shapes of static modules or they have some deficiency or excess CLBs within its rectangular region. To allocate the deficit of a module, if exists, we use a minimum cost maximum flow (MCMF) formulation for each floorplan in the group.