Approximate Computing in Digital Design

Sayandeep Mitra

# Approximate Computing in Digital Design

DISSERTATION SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF

Master of Technology in Computer Science

by

Sayandeep Mitra [ Roll No: CS-1413 ]

under the guidance of

Ansuman Banerjee Associate Professor Advanced Computing and Microelectronics Unit

Indian Statistical Institute Kolkata-700108, India

**July 2016**

To my family and my supervisor

## CERTIFICATE

This is to certify that the dissertation entitled "Approximate Computing in Digital Designs" submitted by Sayandeep Mitra to Indian Statistical Institute, Kolkata, in partial fulfillment for the award of the degree of Master of Technology in Computer Science is a bonafide record of work carried out by him under my supervision and guidance. The dissertation has fulfilled all the requirements as per the regulations of this institute and, in my opinion, has reached the standard needed for submission.

Ansuman Banerjee Associate Professor, Advanced Computing and Microelectronics Unit, Indian Statistical Institute, Kolkata-700108, INDIA.

## Acknowledgments

I would like to show my highest gratitude to my advisor, *Ansuman Banerjee*, Advanced Computing and Microelectronics Unit, Indian Statistical Institute, Kolkata, for his guidance and continuous support and encouragement. He has literally taught me how to do good research, and motivated me with great insights and innovative ideas.

My deepest thanks to all the teachers of Indian Statistical Institute, for their valuable suggestions and discussions which added an important dimension to my research work.

Finally, I am very much thankful to my parents and family for their everlasting support.

Last but not the least, I would like to thank all my friends for their help and support. I thank all those, whom I have missed out from the above list.

Sayandeep Mitra Indian Statistical Institute Kolkata - 700108, India.

### Abstract

In recent times, approximate computing is being looked at as a viable alternative for reducing the energy consumption of programs, while marginally compromising on the correctness of their computation. The idea behind approximate computing is to introduce approximations at various levels of the execution stack, with an attempt to realize the resource hungry computations on low resource consuming approximate hardware blocks. Approximate computing for program transformation faces a serious challenge of automatically identifying core program areas/statements where approximations can be introduced, with a quantifiable measure of the resulting program correctness compromise. Introducing approximations randomly can cause performance deterioration without much energy advantage, which is undesirable. In this thesis, we introduce a verification-guided method to automatically identify program blocks which lend themselves to easy approximations, while not compromising significantly on program correctness. Our method is based on identifying regions of code which are less influential for the computation of the program outputs and therefore, can be compromised with, however still having a potential of significant resource reduction. We take the help of assertions to quantify the effect of the resulting transformations on program outputs. We show experimental results to support our proposal.

**Keywords**: Approximate Computing, Program Slicing, Assertions, Verification, Statement Coverage, Linear Programming.

# Contents

| 1 | Introduction |                                                                          |          |

|---|--------------|--------------------------------------------------------------------------|----------|

|   | 1.1          | Motivation of this dissertation                                          | 11       |

|   | 1.2          | Contribution of this dissertation                                        | 11       |

|   | 1.3          | Organization of the dissertation                                         | 13       |

| 2 | Bac          | ekground and related work                                                | 15       |

|   | 2.1          | Background                                                               | 15       |

|   |              | 2.1.1 Assertions                                                         | 15       |

|   | 2.2          | Related Work on Approximate Computing                                    | 20       |

| 3 | Sta          | tement Identification for Approximate Computing                          | 23       |

|   | 3.1          | Definition                                                               | 23       |

|   | 3.2          | Dynamic Method                                                           | 24       |

|   | 3.3          | Static Approach for Statement Identification                             | 27       |

|   |              | 2.2.1 Decen for a Different Annual                                       | 07       |

|   |              | 3.3.1 Reason for a Different Approach                                    | 27       |

|   |              | 3.3.1       Reason for a Different Approach         3.3.2       Approach | 27<br>27 |

|   |              |                                                                          |          |

|   |              | 3.3.2 Approach                                                           | 27       |

| 4                                                                                  | App                | proxim        | ation Insertion and Correctness Compromise Quantification                                | 35 |  |

|------------------------------------------------------------------------------------|--------------------|---------------|------------------------------------------------------------------------------------------|----|--|

|                                                                                    | 4.1                | Rando         | om Approximation Insertion                                                               | 36 |  |

|                                                                                    | 4.2                | Correc        | ctness and Compromise Measure                                                            | 37 |  |

|                                                                                    | 4.3                | Final         | Form of the Problem                                                                      | 39 |  |

| 5 Statement and Approximation Selection based on Multiple Optimization<br>Criteria |                    |               |                                                                                          |    |  |

|                                                                                    | 5.1                | An In         | teger Linear Programming formulation for Ranked List Aggregation $% \mathcal{L}^{(1)}$ . | 41 |  |

|                                                                                    | 5.2                | Borda         | 's Score                                                                                 | 43 |  |

|                                                                                    | 5.3                | Worki         | ng                                                                                       | 44 |  |

| 6                                                                                  | Imp                | olemen        | tation and Results                                                                       | 47 |  |

|                                                                                    | 6.1 Implementation |               |                                                                                          |    |  |

|                                                                                    | 6.2                | .2 Evaluation |                                                                                          |    |  |

|                                                                                    |                    | 6.2.1         | Case Study on USB Function Core                                                          | 49 |  |

|                                                                                    |                    | 6.2.2         | Case Study on OR1200                                                                     | 50 |  |

|                                                                                    |                    | 6.2.3         | Case Study on PCI IP Core                                                                | 50 |  |

| 7                                                                                  | Cor                | nclusio       | n and Future Work                                                                        | 51 |  |

| 8                                                                                  | Dis                | semina        | ations out of this work                                                                  | 53 |  |

# List of Figures

| 1.1 | Stack Showing Layers of Approximate Computing                      | 12 |

|-----|--------------------------------------------------------------------|----|

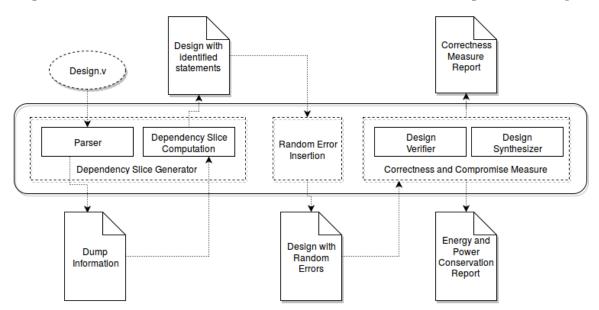

| 1.2 | Overview of our Approach                                           | 12 |

| 3.1 | Example of Statement Coverage                                      | 25 |

| 3.2 | Dynamic method of Statement Identification                         | 26 |

| 3.3 | Working example of a module of traffic light controller            | 29 |

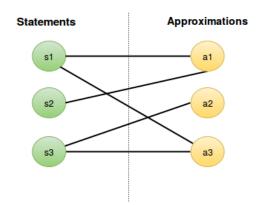

| 4.1 | Bipartite Graph relationship between statements and approximations | 39 |

| 6.1 | System Architecture                                                | 47 |

| 6.2 | Example of the modified approach                                   | 50 |

# List of Tables

| 4.1 | Snapshot of possible modifications          | 36 |

|-----|---------------------------------------------|----|

| 5.1 | List of Approximations applicable           | 44 |

| 5.2 | Top Ten Combinations using Borda Score      | 45 |

| 5.3 | Top Ten Combinations using Kemeny Aggregate | 45 |

| 6.1 | Evaluation Results of our Framework         | 49 |

# Chapter 1

# Introduction

Energy efficiency has become an element of paramount concern in design of computing systems. Ongoing technological developments and the Internet of Things mean more aspects of our lives are being computerized and connected, needing ever more processing of data, thereby requiring the computing systems to become increasingly embedded and mobile. Despite advances in reducing the power consumption of devices and enhanced battery technology, today's designs continue to increase their energy use as the amount of computation increases, at a time when energy efficiency is being encouraged and demands on battery life increasingly scrutinized.

Approximate computing is an emerging design paradigm that aims to address the energy utilization problem from a completely different perspective, by using the inherent resilience of applications to perform computations in an in-exact manner. Computing today is not always about producing a precise numerical result at the end. Many applications have intrinsic tolerance of minor to moderate elements of inaccuracy. Applications in domains like computer vision, media processing, machine learning, and sensor data analysis already incorporate imprecision into their design. Large scale data analytics focus on aggregate trends rather than the integrity of individual data elements. In domains such as computer vision and robotics, there are no perfect answers: results can vary in their usefulness, and the output quality is always in tension with the resources that the software needs to produce them. All these applications are approximate programs: a range of possible values can be considered correct outputs for a given input.

The central challenge in approximate computing is forging abstractions that make imprecision controlled and predictable without sacrificing its efficiency benefits. Many applications are often intrinsically resilient to a large part of their computations being performed in an approximate or imprecise manner, enabling us to save computing resources. Approximate computing helps design platforms for which correctness is defined as producing results that are good enough, judged by some metric, departing from the long held belief that computing platforms should be developed by the same strict notion of correctness. A number of research articles have discussed strategies for implementation of approximate computing in both hardware and software. In [30], approximate computing of applications by loop perforations is proposed. Critical versus tunable loops are identified by intentional perforation of loops and observing the respective output. For hardware, [15] presents the design of a system architecture for approximate applications. [20] designs an imprecise adder which consumes low power performing approximate computing.

The technology of approximate computing today is poised at an interesting juncture, which has led researchers to identify the two main subproblems as below.

- 1. Identification of areas to apply approximation

- 2. Application of suitable approximations, and verify the correctness and gain of the application.

This dissertation attempts to address both the above problems and create a framework that can enable us harness the full power of approximate computing in the best possible way. We discuss about our specific contributions below.

While existing literature talks mostly about methods for implementation of approximate computing in different layers of the execution stack and approximate designs, the problem of automatic identification of candidate program blocks amenable to approximation has been relatively less addressed. We aim to address this important question, specifically, we aim to develop an automated technique for identification of areas in an application where approximations can be implemented. A few articles in recent past have addressed this question in a semi-automated way. In [12, 25, 29] approximation aware programming frameworks are proposed, which provide language constructs to annotate functions, data or loop as approximate or precise. [13, 14] identify resilient computation kernels by injecting errors and then classifying them based on the output quality metric.

In this dissertation, we present A Verification Guided Approach for selective program transformations for Approximate Computing, that can be used to automatically identify areas in a digital design to apply Approximate Computing. A number of proposals have been made in [13, 14] to identify program blocks based on the kernel computation time of innermost loops. The fundamental difference with this body of work on identification of program blocks for application of approximations and our proposed approach is that existing approaches primarily use a semi-automated way based on the program execution on a specific set of inputs, whereas our work proposes a novel approach of statement identification based on program structure along with the execution traits of the design. Our approach stems from the observation that not all statements in a program execute with same effect, nor influence the computation of the outputs equally. Statements which are less prone to executions, or have minor effects on the program output, can thus be approximated, thereby saving computation resources resulting in improved system resource utilization and efficiency. In our model, we propose a formal framework for statement identification, that can identify the set of statements that are suitable for approximations, thereby reducing resource utilization. Experiments show our proposed framework is capable of saving resources significantly for standard Verilog designs.

### **1.1** Motivation of this dissertation

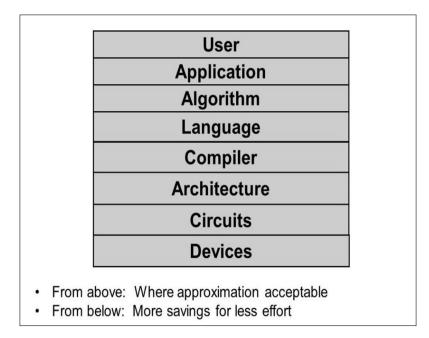

The general system stack is shown in Figure 1.1. From the figure it is clear that, approximation provides a lot of gain if applied to the hardware, while it is better if we apply approximation mainly at the user level or at the language level. The latter approach can be taken in two ways.

- Apply approximations directly in the application or program.

- Identify program areas to be computed with approximate hardware.

In both the methods, it is imperative that parts of the program suitable for approximation are identified, in an efficient method. The main issue, as mentioned is that it is difficult to receive a lot of gain by approximating at the language level. To make the best out of the situation, all possible approximating areas of a program needs to identified. To the best of our knowledge although work has been done to identify program statements for approximation in different machine learning programs, no work has yet been done in digital design. This is the main motivation for this dissertation, where we present such an approach for Verilog design codes. The main contribution of this dissertation is highlighted in the following section.

## **1.2** Contribution of this dissertation

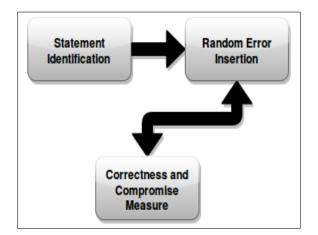

In this dissertation, we propose an automated approach for statement identification for approximation in Verilog programs. We consider a simple overview of our work presented in Fig 1.2, where the three basic steps in our methodology are presented. In this work, initially, we identify statements based on their execution rate and their effects on outputs. After the initial set of statements are identified, we insert random errors (raw approximations) to the programs. This step is interchangeably used along with the correctness and compromise measure which measures the effect of the random error on the program functionality. We use assertions [18] to specify the correctness of the design. After the random error insertion step, we measure the number of assertions that change their truth value. Along with the correctness metric, we also provide the amount of power and circuit area that is reduced due to the random error. Based on these scores, we select the best set of statements to apply our approximations on. In order to avoid applying approximations which result in no

Figure 1.1: Stack Showing Layers of Approximate Computing

gain or highly compromised circuits, we propose certain heuristics for candidate statement selection. This helps us to identify a set of statements suitable for approximations in an efficient and scalable way.

Figure 1.2: Overview of our Approach

# 1.3 Organization of the dissertation

The rest of the dissertation is organized into 6 chapters. A summary of the contents of the chapters is as follows:

Chapter 2: A detailed study of relevant research is presented here.

- Chapter 3: This chapter describes the statement identification step of our approach.

- **Chapter 4**: This chapter describes the random error insertion and correctness step of our approach.

- Chapter 5: This chapter presents methods for candidate statement selection.

- **Chapter 6**: This chapter describes the detailed case study of our work, implementation and results.

- Chapter 7: We summarize with conclusions on the contributions of this dissertation.

# Chapter 2

# Background and related work

In this chapter, we first present a few background concepts needed for developing the foundation of our framework. We also present an overview of different schemes proposed in literature for approximate computing.

### 2.1 Background

In this section, we discuss a few background concepts.

#### 2.1.1 Assertions

Assertions are primarily used to validate the behavior of a design ("Is it working correctly?"). They may also be used to provide functional coverage information for a design ("How good is the test?"). Assertions can be checked dynamically by simulation, or statically by a separate property checker tool i.e. a formal verification tool that proves whether or not a design meets its specification. Such tools may require certain assumptions about the design behavior to be specified.

Some of the popular assertion languages used in the industry are :

- PSL (Property Specification Language) based on IBM Sugar [4]

- Synopsys OVA (Open Vera Assertions) and OVL (Open Vera Library) [7]

- Assertions in Specman [6]

- 0-In (0In Assertions)

- SystemC Verification (SCV)

- SVA (SystemVerilog Assertions)

In this section, we introduce the popular type of assertions System Verilog Assertions (SVA) [18] and describe its functionality.

#### System Verilog Assertions

SystemVerilog assertions are built from sequences and properties. Properties are a superset of sequences; any sequence may be used as if it were a property, although this is not typically useful. In SystemVerilog there are two kinds of assertion: **immediate** (assert) and **concurrent** (assert property). Coverage statements (cover property) are concurrent and have the same syntax as concurrent assertions, as do assume property statements, which are primarily used by formal tools. Finally, expect is a procedural statement that checks that some specified activity (property) occurs. The three types of concurrent assertion statement and the expect statement make use of sequences that describe the design's " temporal behavior" i.e. behavior over time, as defined by one or more clocks.

#### **Immediate Assertions**

Immediate assertions are procedural statements and are mainly used in simulation. An assertion is basically a statement that something must be true, similar to the if statement. The difference is that an if statement does not assert that an expression should be true, it simply checks that it is true.

**Example 2.1** if  $(A == B) \dots //$  Simply checks if A equals B assert (A == B); // Asserts that A equals B; if not, an error is generated

If the conditional expression of the immediate assert evaluates to X, Z or 0, then the assertion fails and the verification tool writes an error message. An immediate assertion may include a pass statement and/or a fail statement. The following example shows a case with an action specified if the assertion evaluates to true.

**Example 2.2** assert (A == B) \$display ("OK. A equals B");

It is executed immediately after the evaluation of the assert expression. The statement associated with an else is called a fail statement and is executed if the assertion fails:

**Example 2.3** assert (A == B) \$display ("OK. A equals B"); else \$error("It's gone wrong");

We may omit the pass statement yet still include a fail statement:

**Example 2.4** assert (A == B) else \$error("It's gone wrong");

#### **Concurrent Assertions**

The behavior of a design may be specified using statements similar to these:

"The Read and Write signals should never be asserted together."

"A Request should be followed by an Acknowledge occurring no more than two clocks after the Request is asserted."

Concurrent assertions are used to check behavior such as these. These are statements that assert that specified properties must be true.

**Example 2.5** assert property (!(Read && Write));

asserts that the expression Read  $\mathcal{E}\mathcal{E}$  Write is never true at any point in the design.

Properties are often built using sequences.

**Example 2.6** assert property ( @(posedge Clock) Req |-> ##[1:2] Ack);

where Req is a simple sequence (it's just a Boolean expression) and ##[1:2] Ack is a more complex sequence expression, meaning that Ack is true on the next clock, or on the one following (or both).  $|-\rangle$  is the implication operator, so this assertion checks that whenever Req is asserted, Ack must be asserted on the next clock, or the following clock.

Concurrent assertions like these are checked throughout simulation or formal verification. They usually appear outside any initial or always blocks in modules, interfaces and programs. Concurrent assertions may also be used as statements in initial or always blocks. A concurrent assertion in an initial block is only tested on the first clock tick.

The first assertion example above does not contain a clock. Therefore it is checked at every point in the simulation. The second assertion is only checked when a rising clock edge has occurred; the values of *Req* and *Ack* are sampled on the rising edge of Clock.

#### Implication

The implication construct  $(|-\rangle)$  allows a user to monitor sequences based on satisfying some criteria, e.g. attach a precondition to a sequence and evaluate the sequence only if the condition is successful. The left-hand side operand of the implication is called the antecedent sequence expression, while the right-hand side is called the consequent sequence expression. If there is no match of the antecedent sequence expression, implication succeeds vacuously by returning true. If there is a match, for each successful match of the antecedent sequence expression, the consequent sequence expression is separately evaluated, beginning at the end point of the match.

There are two forms of implication: overlapped using operator  $|-\rangle$ , and non-overlapped using operator  $|=\rangle$ . For overlapped implication, if there is a match for the antecedent sequence expression, then the first element of the consequent sequence expression is evaluated on the same clock tick.

s1 | -> s2;

In the example above, if the sequence s1 matches, then sequence s2 must also match. If sequence s1 does not match, then the result is true. For non-overlapped implication, the first element of the consequent sequence expression is evaluated on the next clock tick.

$s1 \mid => s2;$

where true is a boolean expression, used for visual clarity, that always evaluates to true.

#### Assertion Clocking

Concurrent assertions (assert property and cover property statements) use a generalized model of a clock and are only evaluated when a clock tick occurs. In fact, the values of the variables in the property are sampled right at the end of the previous time step. Everything in between clock ticks is ignored.

A clock tick is an atomic moment in time and a clock ticks only once at any simulation time. The clock can actually be a single signal, a gated clock (e.g. (clk && GatingSig)) or other more complex expression. When monitoring asynchronous signals, a simulation time step corresponds to a clock tick.

#### Example 2.7 property p;

@(posedge clk) a ##1 b; endproperty assert property (p);

#### Putting It All Together

We look at couple of complete examples for System Verilog Assertions.

**Example 2.8** "A request (req high for one or more cycles then returning to zero) is followed after a period of one or more cycles by an acknowledge (ack high for one or more cycles before returning to zero). ack must be zero in the cycle in which req returns to zero."

```

assert property ( @(posedge clk) disable iff reset

!req ##1 req[*1:$] ##1 !req

|->

!ack[*1:$] ##1 ack[*1:$] ##1 !ack );

```

**Example 2.9** "After a request, ack must remain high until the cycle before grant is high. If grant goes high one cycle after req goes high then ack need not be asserted."

assert property ( @(posedge clk) disable iff reset  $\operatorname{srose}(\operatorname{req}) \mid => \operatorname{ack}[*0:\$] \#\#1 \operatorname{grant}$ ); where  $\operatorname{srose}(\operatorname{req})$  is true if req has changed from 0 to 1.

### 2.2 Related Work on Approximate Computing

In this section, we discuss some related work that has been done so far. In the first part of this section, we discuss various work done on automatic identification for approximate computing in literature. This is followed by a brief analysis of work done on ensuring quality of approximate computing.

A software framework for automatically discovering approximable data in a program by using statistical methods is presented in [28]. Their technique first collects the variables of the program and the range of values that they can take. Then, using binary instrumentation, the values of the variables are perturbed and the new output is measured. By comparing this against the correct output, which fulfills the acceptable QoS threshold, the contribution of each variable in the program output is measured. The variables are marked as approximable or nonapproximable based on the above score. Thus, their framework obviates the need of a programmers involvement or source code annotations for Approximate Computing. They compared this to a baseline with type-qualifier annotations by the programmer [29], their approach achieves nearly 85% accuracy in determining the approximable data. Their limitation is that some variables that are marked as nonapproximable in the programmer-annotated version may be marked as approximable by their technique. which can lead to errors. A technique was presented in [13][14] for automatic resilience characterization of applications. The method has two parts. The resilience identification part, considers innermost loops that occupy more than 1% of application execution time as atomic kernels. The application executes with input datasets, then random errors are introduced into the output variables of a kernel using the Valgrind DBI tool. If the output quality is not up to the mark or if the application crashes, the kernel is marked as sensitive; otherwise, it is potentially resilient. In the resilience characterization step, potentially resilient kernels are further explored to see the applicability of various approximation strategies. In this step, errors are introduced in the kernels using Valgrind based on the approximation models. To quantify resilience, they propose an Approximation Computing Technique(ACT)-independent model and an Approximate Computing Technique specific model for approximation. The ACT-independent approximation model studies the errors introduced due to ACT using a statistical distribution that shows the probability, magnitude, and predictability of errors. The ACT-specific model may use different ACTs, such as precision scaling, inexact arithmetic circuits, and loop perforation. The experimental results show that several applications show high resilience to errors, and many parameters such as the scale of input data, granularity of approximation have a significant impact on application resilience. Two techniques were presented in [27] for selecting approximable computations for a reduce and rank kernel. A reduce and rank kernel performs reduction between an input vector and each reference vector, the outputs are then ranked to find the subset of top reference vectors for that input. Their first technique decomposes vector reductions into multiple partial reductions and interleaves them with the rank computation. The next step identifies whether a particular reference vector is expected to appear in the final subset. Based on this, future computations that have little impact on the output after

relaxation are selected. The second technique leverages the temporal or spatial correlation of inputs. Depending on the similarity between current and previous input, this technique approximates or entirely skips processing parts of the current inputs. Approximation is achieved using precision scaling and loop perforation strategies. Language extensions and an accuracy-aware compiler for facilitating writing of configurable-accuracy programs has been presented in [9]. The compiler performs auto tuning using a genetic algorithm to explore the search space of possible algorithms and accuracy levels for dealing with recursion and sub calls to other configurable-accuracy code. Initially, the population of candidate algorithms is maintained, which is expanded using mutators and later pruned to allow more optimal algorithms to evolve. Thus, the user needs to specify only accuracy requirements and does not need to understand algorithm specific parameters, while the library writer can write a portable code by simply specifying ways to search the space of parameter and algorithmic choices. To limit computation time, the number of tests performed for evaluating possible algorithms needs to be restricted. This can lead to the choice of suboptimal algorithms and errors, hence the number of tests performed needs to be carefully chosen. A programming language, named Rely was proposed in [12], that allows programmers to determine the quantitative reliability of a program. In the Rely language, quantitative reliability can be specified for function results; for example, in int < 0.99 \* R(arg) > FUNC(intarg, int x) code, 0.99<sup>\*</sup>R(arg) specifies that the reliability of return value of FUNC must be at least 99% of reliability of arg when the function was invoked. Rely programs can run on a processor with potentially unreliable memory and unreliable logical/arithmetic operations. The programmer can specify that a variable can be stored in unreliable memory and/or an unreliable operation can be performed on the variables. Integrity of memory access and control flow are maintained by ensuring reliable computations for the corresponding data. By running both error-tolerant programs and checkable programs (those for which an efficient checker can be used for dynamically verifying result correctness), they show that Rely allows determination of integrity (i.e., correctness of execution and validity of results) and QoR of the programs.

It was noted in [19] that, for several computation intensive applications, although finding a solution may incur high overheads, checking the solution quality may be easy. They proposed decoupling error analysis of approximate accelerators from application quality analysis by using application specific metrics called light weight checks (LWCs). LWCs are directly integrated into the application, which enables compatibility with any ACT. By virtue of being lightweight, LWCs can be used dynamically for analyzing and adapting application-level errors. Only when testing with LWCs indicates quality loss below a set standard, exact computation needs to be performed for recovery. Otherwise, the approximation is considered acceptable. This saves energy without compromising reliability. Their approach guarantees bounding worst-case error and obviates the need of statically designed error models. A quality control technique for inexact accelerator based platforms was proposed in [24]. They note that an accelerator may not always provide acceptable results; thus, blindly invoking the accelerator in all cases will lead to quality loss and waste of energy and execution time. They proposed a predictor that guessed whether the invocation of accelerator will lead to quality degradation below a threshold. If yes, their technique instead invokes the precise code. A novel product program construction for differential assertion checking is presented in [23] that permits procedural programs, and allows leveraging off-the-shelf program verifiers and invariant inference engines. This work shows that mutual summaries naturally express many relaxed specifications for approximations, and SMT-based checking and invariant inference can substantially automate the verification of such specifications and provides us with an insight that assertions can be used as a proper metric for approximation quality.

To the best of our knowledge, our proposed model is the first work of its kind. We use automated techniques to identify approximable regions of digital design code and measure the resulting correctness compromise using assertions. This is the major limelight of this dissertation.

# Chapter 3

# Statement Identification for Approximate Computing

In this chapter, we formally explain our approaches for identifying statements which can be suitable for approximations. In the subsequent chapter, we elaborate the next two steps of our complete methodology.

## 3.1 Definition

The main idea of the statement identification step is to segregate the statements of a digital design, into two parts.

- Possibly Approximable Statements : These are statements which can be executed in a manner so that they produce a *good enough* result.

- Sensitive Statements : These are the statements which are extremely *important* to the digital design. We can say that these statements needs to be executed with exact accuracy.

There are two approaches we have pursued to identify possibly approximable statements.

- Dynamic Method : The dynamic method uses coverage to separate between the statements. Low covered statements are judged to be possibly approximable whereas highly covered statements are marked as sensitive statements.

- Static Method : We use the program's dependency graph to find out the number of output variables each statement affects. Statement which affect lower number of

output variables are marked as potentially approximable statements, while the rest are marked as sensitive statements.

We explain in detail both the methods in the discussion below.

## 3.2 Dynamic Method

#### **Detailed Methodology**

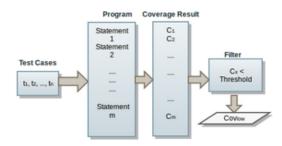

The dynamic approach is based on the calculation of statement coverage  $C_{statement}$ , of the Verilog code based on a large number of given test cases, similar to the approach used in [10].

**Statement Coverage :** Statement coverage, also known as line coverage is the easiest understandable type of coverage. From N lines of code and according to the applied stimulus how many statements (lines) are covered in the simulation is measured by statement coverage. If a DUT is 10 lines long and 8 lines out of them were exercised in a test run, then the DUT has line coverage of 80%. Line coverage includes continuous assignment statements, Individual procedural statements, Procedural statement blocks, Procedural statement block types, Conditional statement and Branches for conditional statements.

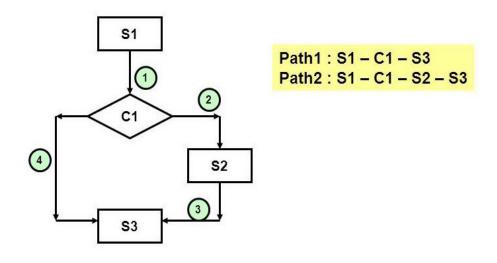

For a particular test case, not all statements of the design are executed. For a large set of test cases, a particular statement in the design will be executed for a subset of given test set. To understand this approach consider Figure 3.1. There are two paths based on the condition C1. One which contains statement S2 and another which contains statement S3. S1 is common to both the paths. For say around t number of test cases, it is obvious that S1 will be executed for all. However S2 will be executed for some of the test cases among t, and the rest shall cause S3 to execute.

We can intuitively see that the set of statements can be segregated into two sets. One,  $Cov_{high}$  with a very high coverage value, greater than a given threshold  $t_c$ , which can be set depending upon the level of approximation we want to perform. This signifies that majority of the test cases had the statement on their execution path. We claim these sentences to be very important to the design, which need to be executed with exact precision and thus, are marked as sensitive. Second,  $Cov_{low}$  the rest of the statements which have a low coverage value, as they are executed for a very less number of test cases. We claim these statements to be potentially approximable statements, which can be approximated to reduce the gate count or power consumption of the design. Since they are not executed very frequently, we can deal with their precision being slightly inexact, having significant resource optimization in return. The value of threshold  $t_c$  can be decided by the user. It acts as the controlling parameter of the level of approximation we want to perform.

Figure 3.1: Example of Statement Coverage

**Example 3.1** If  $t_c$  is set to be 20%, it means we shall consider only those statements in our next step, who have a coverage score of less than 20%, i.e they have been executed for less than 20% of the test cases.

Figure 3.2 shows the steps of the above approach.

Formally, the dynamic approach can be stated as follows: We define **S** to be the set of all statements of the given digital design code and  $C_{statement_s}$ , the coverage score of a statement  $s \in \mathbf{S}$ . s is used to segregate statements as:

$$s \in \begin{cases} Cov_{high}, & \text{if } C_{statement_s} > t_c \\ Cov_{low}, & \text{otherwise} \end{cases}$$

(3.1)

At the end of the dynamic approach, we can generate a matrix A of the form *Statements* x *Test Cases.* A 1 in the position  $a_{ij}$  signifies that statement *i* has been executed by test case *j*, 0 signifies otherwise. This will be used in the upcoming sections for the purpose of ranked aggregation.

Figure 3.2: Dynamic method of Statement Identification

**Example 3.2** The matrix below shows the matrix A for 30 sentences against 5 test cases. Statement 1 is executed for all five of the test cases, whereas statement 2 is executed for only two of the test cases,  $t_2$  and  $t_5$ .

$$\mathbf{A} = \begin{bmatrix} s_1 & t_1 & t_2 & t_3 & t_4 & t_5 \\ s_2 & \begin{bmatrix} 1 & 1 & 1 & 1 & 1 \\ 0 & 1 & 0 & 0 & 1 \\ \vdots & \vdots & \vdots & \vdots & \vdots \\ 0 & 1 & 1 & 0 & 1 \end{bmatrix}$$

## 3.3 Static Approach for Statement Identification

#### 3.3.1 Reason for a Different Approach

The dynamic approach of statement identification, brings forward the old question of *Are* there enough test cases?. It is quite possible, that for a larger number of test cases, some of the statements, which had low coverage score previously might end up having a high coverage score. Also, to get a large number of test cases, one has to use a random test generator, which without considering the design shall provide us test cases. It is quite possible that, the test cases may be focused on some particular branches more than the rest. So it is evident that blindly increasing the number of test cases is not enough. However the dynamic approach gives us a rough acceptance, that our intuition of segregating statements in a Verilog design is possible and its initial results were quite supportive as well.

As a second method, we decided to look at an approach that does not depend on the behavior of the test cases, or the number of test cases. We decided to utilize the program structure to shortlist our statements, rather than depend on any other separate inputs. We present the *static* approach, which utilizes the dependency graph for a module to shortlist the statements, based on the number of output variables it affects.

#### 3.3.2 Approach

As mentioned in the previous section, we now aim to develop a statement identification approach, which shall use the program structure to identify statements possible for approximations. We present the static approach which uses the concept of the effect a statement has on a particular output, to mark statements which are *sensitive* and *possibly approximable*.

In a Verilog program, each module has multiple outputs. Each statement in the program, does not take part in the decision for the value of every output variable. This is the major motivation behind the static approach, where we aim to find out the number of output variables affected by a particular statement, and then use that score to segregate between the statements. To understand this concept let us look at the following example.

**Example 3.3** Consider four statements  $s_1$ ,  $s_2$ ,  $s_3$  and  $s_4$  in a module. There are three outputs in the module,  $o_1$ ,  $o_2$  and  $o_3$ .

The value of  $o_1$  is affected by  $s_1$  and  $s_3$ . The value of  $o_2$  is affected by  $s_1$ ,  $s_3$  and  $s_4$ . The value of  $o_3$  is affected by  $s_2$ . From the above example, we see that there is a score on the basis of which we can segregate the statements. Clearly, statement  $s_2$  has a lot less affect on the total functionality of the module. Similar to the dynamic approach, we can separate the statements into two categories. One, in which the statements affect a large number of output variables, i.e, above a given threshold, and the other in which the statements affects a less number of output variables.

Formally, the static approach can be stated as follows: We define **S** to be the set of all statements of the function and  $OutScore_{statement_s}$  to be the score of a statement, which specifies the number of output variables it affects  $s \in \mathbf{S}$ .  $t_{os}$  is the given threshold. s is segregated as:

$$s \in \begin{cases} OutScore_{high}, & \text{if } OutScore_{statement_s} > t_{os} \\ OutScore_{low}, & \text{otherwise} \end{cases}$$

(3.2)

Similar to the dynamic approach, we claim that the statements in the set  $OutScore_{high}$ , are very important to the program, as they affect a large number of output variables. These statements needs to be performed possibly with exact accuracy, and are thus said to be *sensitive*. For the statements in  $OutScore_{low}$ , the program can deal with their results being a little inexact from the correct value, as they affect very less number of output variables. These statements are claimed as *possibly approximable*. The value of threshold  $t_{os}$  can be decided by the user. It acts as the controlling parameter of the level of approximation we want to perform.

**Example 3.4** If  $t_{os}$  is set to be 40%, it means we shall consider only those statements in our next step, who influence the value of less than 40% of the total output variables.

At the end of the static approach, we can generate a matrix B of the form *Statements* x *Output Variables.* A 1 in the position  $b_{ij}$  signifies that statement *i* has affected output variable *j*, 0 signifies otherwise. This will be used in the upcoming sections for the purpose of ranked aggregation.

**Example 3.5** The matrix below shows the matrix B for 30 sentences against 4 output variables. Statement 2 is responsible for the value of 4 of the output variables, whereas statement 30 affects only two output variables,  $o_1$  and  $o_3$ .

$$\mathbf{B} = \begin{bmatrix} s_1 & 0_1 & 0_2 & 0_3 & 0_4 \\ s_2 & 1 & 1 & 1 & 0 \\ s_3 & 1 & 1 & 1 & 1 \\ \vdots & \vdots & \vdots & \vdots \\ 1 & 0 & 1 & 0 \end{bmatrix}$$

```

1

module farm_control(clk, car_present, enable_farm, short_timer, long_timer, farm_light,

farm_start_timer, enable_hwy);

\mathbf{2}

3

input clk;

4

5

.

\mathbf{6}

output farm_light;

7

output farm_start_timer;

8

output enable_hwy;

9

.

10

initial farm_light = RED; /*farm_start_timer,

11

12

enable_hwy, farm_light*/

13

assign farm_start_timer = (((farm_light == GREEN) && ((car_present == NO) || long_timer)) ||

14

(farm_light == RED) && enable_farm); //farm_start_timer

15

16

assign enable_hwy = ((farm_light == YELLOW) && short_timer); /*enable_hwy*/

17

always @(posedge clk) begin

18

19

case (farm_light)

/*farm_start_timer,

20

enable_hwy, farm_light*/

21

GREEN:

22

if ((car_present == NO) || long_timer)

/*farm_start_timer, enable_hwy, farm_light*/

23

24

farm_light = YELLOW;

/*farm_start_timer,

enable_hwy, farm_light*/

25

26

YELLOW:

27

/*farm_start_timer,

if (short_timer)

28

enable_hwy, farm_light*/

29

farm_light = RED;

/*farm_start_timer,

30

enable_hwy, farm_light*/

31

RED:

/*farm_start_timer,

32

if (enable_farm)

33

enable_hwy, farm_light*/

34

farm_light = GREEN;

/*farm_start_timer,

35

enable_hwy, farm_light*/

36

endcase

end

37

38

always@(posedge clk)

39

begin

40

gm0 : assert property(!((farm_light == GREEN) && (hwy_light == GREEN)));

41

gm1 : assert property (((car_present == YES) ##0 (!(farm_light == GREEN))[*0:$]));

42

gm2 : assert property ((hwy_light == GREEN)[*1:$]);

43

end

endmodule

44

```

Figure 3.3: Working example of a module of traffic light controller

#### 3.3.3 Motivating Example

To implement the static approach, we implement dependency slicing, which traverses the control dependency flow graph of the module, and identifies statements which changes the values of the variables. A number of dependencies arise in this approach, namely transitive, conditional and direct dependencies which need to be taken care of. We present an example which presents a clear explanation of the static approach for statement identification.

**Example 3.6** Consider Figure 3.3, which shows a simple Verilog design module of a light controller, which controls the light on a crossing (details not shown in figure), depending on the various inputs received (e.g., car present, timer duration, etc). Our algorithm begins by examining each output variable in turn. The variables in green beside the statements show that the statement modifies this particular variable. Consider the output farm\_light which is modified in three statements, 24, 29, and 34. Each of these is control dependent on an if condition. The variables in the if conditions on line 22, 27, and 32 are enable\_farm, short\_timer, car\_present and long\_timer. All these statements lie nested under the case statement at line 19 and are therefore, control dependent on it. Further, statement 11 belongs to the dependency slice of farm\_light since it assigns a value to it. For enable\_hwy, statement 16 belongs to its dependency slice due to the direct data dependency. The variables on the right hand side of the assign statement are farm\_light and short\_timer. The concurrency semantics of Verilog language makes the other two outputs farm\_start\_timer, enable\_hwy affected by statements 22 to 34 as well. In particular, enable\_hwy is assigned at statement 16, which checks for a condition on farm\_light. Hence, statements 11, 19, 22, 24, 27, 29, 32, and 34 which belong to the dependency slice of farm\_light end up indirectly affecting the logic of computation for enable\_hwy. A similar reasoning holds for the other output variable as well.  $\blacksquare$

#### 3.3.4 Algorithm for Static Approach

The dependency slicing [11][26] step takes in the following input: (a) The program P and (b) A list of module output variables. The output of the method is a list of statements  $\phi \subseteq P$  that influence the computation of the output variables. The dependency slice,  $Dep_i$ , for variable *i* computes a chain of static data and control dependencies. In the slicing algorithm, for each output variable *out*, we traverse the program and mark the data and control dependencies, both the direct ones and the transitive ones that propagate through other variables. In other words, we end up computing the transitive closure of the data and control dependencies for the variable *out*. Finally, we mark all such statements as influencing the variable *out*. The slicing is done on the control and data flow graph (CDFG) [11] constructed from the module code. Algorithm 1 presents the dependency slice computation strategy. We take each module output *out*, and compute the dependency slice chain starting from the first unmarked statement where *out* is assigned. The algorithm terminates when we reach a fix point, in other words, no new statements are added and no new variables are encountered.

| Algorithm | 1: | Dependence | cy Slice | Computation |

|-----------|----|------------|----------|-------------|

|           |    |            |          |             |

| <b>Input</b> : $D$ : Design to be approximated                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Out: Outputs of $D$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| S: Set of all statements of $D$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| <b>Output</b> : $Dep_{Out}$ : Dependency slice of module outputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| begin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| for all $out \in Out \mathbf{do}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| for all unmarked $s \in S$ do                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| <b>if</b> out modified in s <b>then</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Add $s$ to $Dep_{out}$ and mark $s$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| $B[s][out] \leftarrow 1$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |