# MEMRISTIVE CROSSBARS: ALU DESIGN, TESTING, AND FAULT ANALYSIS FOR NEUROMORPHIC APPLICATIONS

A thesis submitted for the degree of **Doctor of Philosophy**

by

Manobendra Nath Mondal

Advisors

Prof. Susmita Sur-Kolay and Prof. Bhargab B. Bhattacharya

Advanced Computing and Microelectronics Unit Indian Statistical Institute 203 B. T. Road, Kolkata - 700108 West Bengal, India July 2023 Dedicated to To my family

#### Acknowledgements

The journey towards the completion of this thesis has been a formidable one, filled with both challenges and triumphs. Along this path, I have been fortunate to receive unwavering support from those around me, and I would like to take this opportunity to express my heartfelt gratitude to all those who have contributed to making this experience truly memorable.

First and foremost, I extend my sincere appreciation to my supervisors Prof Susmita Sur-Koley, and Prof. Bhargab B. Bhattacharya, whose constant guidance and support have been instrumental throughout my Ph.D. Prof. Bhattacharya's profound knowledge and invaluable insights have enriched my understanding of the subject matter , while Prof. Sur-Kolay's expertise in the field have made the complex research work more accessible. I am truly grateful for their unwavering encouragement, motivation, and constructive criticism, which have propelled me towards achieving my goals. I would also like to acknowledge the exceptional support of Prof. Nabanita Das, and all the faculty members from whom I have gained invaluable knowledge during this journey.

Every result presented in this thesis owes its accomplishment to the support and collaboration of fellow lab-mates and collaborators. I wholeheartedly appreciate the immense help and teachings of Sandip-da, Sukanta-da, and Sudip-da throughout these years. I would like to extend my sincere thanks to Manjari Pradhan, Animesh Basak Chowdhury, and Santlal Prajapati for their fruitful contributions to our co-authored paper.

I am also thankful for the support and camaraderie of my colleagues, including Debasisda, Dibakar-da, Oishila-di, Samir, Abhishek, Tapalina, and Mukta. Their presence and encouragement have been invaluable. I extend special appreciation to Dulu-da for his caring presence throughout these days. My sincere thanks to Sachi-da and Debu-da for their technical assistance. I would also like to acknowledge to the non-teaching staff of the Advanced Computing and Microelectronics Unit, ISI for the constant assistance in official matters.

I would like to express my sincere gratitude to the Indian Statistical Institute, Kolkata, for providing the fellowship for my Ph.D. research. I would also like to thank the anonymous reviewers and experts who have contributed their valuable time and insights to the review process.

Words cannot convey my gratitude to Subrata-da who have been always beside me in

all my ups and downs through his unconditional love and support. My heartfelt thank goes to my friends Samir, Buro, Bishnu, Piu, Anirban, Dibyendy, Shouvik, Banani, Swadesh, Kaustav, Daribaba, Partha, Subho, Sadhan, Jitu, Panda, Pabitra, Raju-da, Subrata-da,

Lastly, I offer my deepest and most heartfelt gratitude to my parents and all my family members. Without the unwavering support, boundless love, and constant encouragement from Borda, Mejda, and Didi, I would have never been able to include "Dr." before my name. I am deeply grateful to my wife, Suchetana, whose unwavering belief in me has been the cornerstone of my perseverance and achievements.

Pitam for all the emotional support and caring they provided. Your friendship is irreplace-

To all the individuals mentioned above, and to those whose names may have inadvertently been left out, I extend my sincere gratitude for the profound impact you have had on my academic and personal growth. It is through the collective support of these exceptional individuals that I stand proudly before you today, presenting this thesis.

Manobendra Nath Mondal

able.

#### Abstract

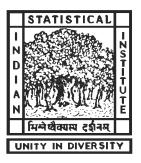

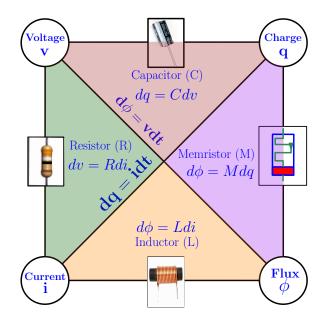

In 1971, Professor Leon Chua introduced the notion of a memristor, the fourth fundamental passive circuit component alongside resistor, capacitor, and inductor. The resistance of this two-terminal device depends on the current through it; thereby a memristor is similar to a resistor with memory. In 2008, a group of researchers at HP Labs built the first memristor successfully and demonstrated its characteristic resistance-switching behavior. Its unique properties and compatibility with CMOS technology has made it a powerful circuit element and has significantly influenced design paradigms.

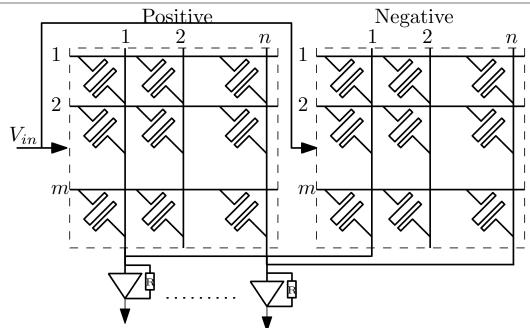

Recent developments have shown that memristors are promising for designing memory and logic subsystems, which can store multiple states of memory by utilizing the analog variation of resistance in the cells. By combining CMOS components with memristor cells, hybrid systems can be created where CMOS components can perform computation-in-memory (CIM), while memristor cells can store data in a non-volatile manner. Memristor-based crossbars (MBCs) realised as a 2D-array of memristors, have been particularly effective for performing certain types of computations, such as vector-matrix multiplication (VMM) and vector outer product, which are crucial in neuromorphic computing systems. Developing practical and reliable memristive crossbar-based systems for various applications still poses significant challenges which can hinder their performance and scalability. This thesis tackles several challenges head-on, offering innovative solutions that elevate their performance, reliability, and scalability.

In this thesis, we introduce novel designs for an Arithmetic Logic Unit (ALU) that utilize differential currents passing through a hybrid-memristor crossbar network. The ALU performs integer addition, subtraction, multiplication, and logical operations in the binary domain, using both analog and digital components. The analog component provides the peripheral control circuit, input voltages and logic values to the crossbar in the form of memristor-states. The variation of the analog output current is then sensed and converted back to discrete logic bits using A/D converters. Our simulation studies demonstrate that our proposed designs are more efficient than previous approaches, with lower memristor cost and computation-cycle time required for integer addition and multiplication.

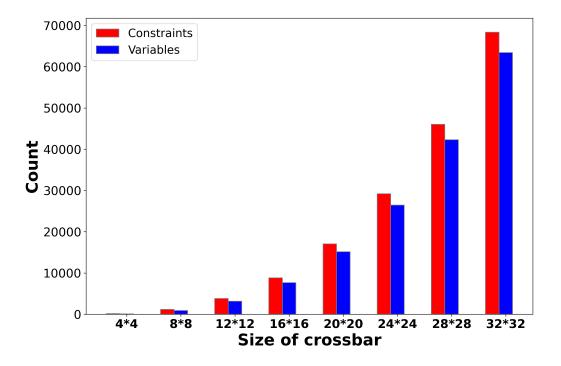

Next, we envisage a 2D memristor crossbar as a network and identify certain paths that are suitable for fault sensitization. In order to optimize testing time for large scale full-size square and rectangular memristive crossbars, we propose a path-based technique guided by maximum matching in bipartite graphs. In order to address the testing optimization problem in both complete and incomplete crossbars, we employ an Integer Linear Programming (ILP) formulation. By comparing the results of the ILP formulation with our proposed path-based techniques, we observe that our method minimizes the number of paths required. Through simulations conducted in LTspice, we validate the effectiveness and superiority of our approach over previous techniques in terms of test time and fault coverage.

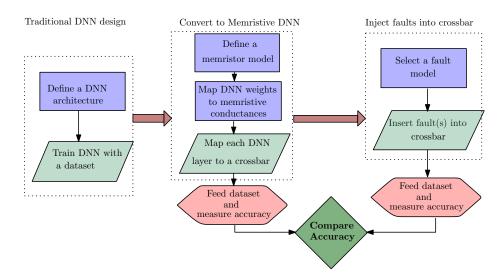

Finally, we present a thorough analysis of the impact of various hard faults on memristive crossbars utilized in neuromorphic computing. This study is critical as comprehending the effects of such faults can enhance the reliability and efficacy of fault-tolerant memristor based neuromorphic computing systems with resource constraints. Moreover, understanding the effect of faults on individual layers of memristive crossbar-based neural architecture can guide the discovery of optimal architecture design to solve specific problems with predefined accuracy.

Overall, this thesis contributes to advancing memristor-based computing systems by addressing ALU design, fault sensitization, test time optimization, and the impact of faults on neuromorphic architectures. The findings provide valuable insights to improve the reliability and performance of future fault-tolerant memristor-based systems across a wide range of applications.

# CONTENTS

| 1 | Intro | roduction and the Scope of the Thesis                        |           | 1  |

|---|-------|--------------------------------------------------------------|-----------|----|

|   | 1.1   | Introduction                                                 |           | 1  |

|   | 1.2   | Memristor Model                                              |           | 3  |

|   | 1.3   | Memristive Crossbar                                          |           | 6  |

|   | 1.4   | Read and Write Operations in Memristive Crossbars            |           | 7  |

|   |       | 1.4.1 Read Operation                                         |           | 8  |

|   |       | 1.4.2 Write Operation                                        |           | 8  |

|   | 1.5   | Motivation and Scope of this thesis                          |           | 9  |

|   |       | 1.5.1 Roadblocks in Computation-In-Memory (CIM)              |           | 9  |

|   |       | 1.5.2 Challenges in Testing Memristive Crossbars             |           | 11 |

|   |       | 1.5.3 Fault-Tolerant Memristive Neural Networks: Key Challen | $\log es$ | 12 |

|   | 1.6   | Organization of the Thesis                                   |           | 13 |

| 2 | Revi  | view of Related Works                                        |           | 15 |

|   | 2.1   | Introduction                                                 |           | 16 |

|   | 2.2   | Memristor Models                                             |           | 16 |

|   |       | 2.2.1 Linear ion-drift model                                 |           | 16 |

|   |       | 2.2.2 Non-linear ion-drift model $\ldots$                    |           | 17 |

|   |       | 2.2.3 Simmons tunnel barrier model                           |           | 17 |

|   |       | 2.2.4 Yakopcic neuromorphic memristor model                  |           | 18 |

|   |       | 2.2.5 TEAM – ThrEshold Adaptive Memristor model              |           | 18 |

|   |       | 2.2.6 VTEAM – Voltage ThrEshold Adaptive Memristor mode      | l         | 18 |

|   |       | 2.2.7 Stanford-PKU model                                     |           | 19 |

|   |       |                                                              |           |    |

# Contents

|   | 2.3 | Memristive Crossbars                                                           | 19 |

|---|-----|--------------------------------------------------------------------------------|----|

|   |     | 2.3.1 1T1R cell and crossbar array                                             | 20 |

|   |     | 2.3.2 1S1R cell and crossbar array                                             | 20 |

|   |     | 2.3.3 1D1R cell and crossbar array                                             | 20 |

|   |     | 2.3.4 1BJT1R cell and crossbar array                                           | 20 |

|   |     | 2.3.5 CRS memory cell and crossbar array                                       | 21 |

|   |     | 2.3.6 SRC and crossbar array                                                   | 21 |

|   |     | 2.3.7 SSC and crossbar array                                                   | 21 |

|   |     | 2.3.8 Comparison of various architectures                                      | 21 |

|   | 2.4 | Security Implications of Memristor-based Systems                               | 22 |

|   |     | 2.4.1 Black-box attacks and countermeasures                                    | 22 |

|   |     | 2.4.2 White-box attacks and countermeasures                                    | 23 |

|   | 2.5 | Memristive ALU Design for Computation-In-Memory (CIM)                          | 24 |

|   |     | 2.5.1 Gaps addressed in our work                                               | 27 |

|   | 2.6 | Testing of Memristive Crossbars                                                | 27 |

|   |     | 2.6.1 Gaps addressed in our work                                               | 30 |

|   | 2.7 | Fault Analysis in Memristive Neuromorphic Architectures                        | 30 |

|   |     | 2.7.1 Gaps addressed in our work                                               | 32 |

| 3 | Des | ign of Memristive Adders using Differential Current Sensing                    | 33 |

|   | 3.1 | Introduction                                                                   | 34 |

|   | 3.2 | Motivation                                                                     | 34 |

|   | 3.3 | Designing Adders Based on Current-Comparison                                   | 36 |

|   |     | 3.3.1 Design of output computing unit (OCU)                                    | 38 |

|   |     | 3.3.2 Fast multi-operand addition inspired by Carry-Save Adder                 | 39 |

|   |     | 3.3.3 Memristive Addition inspired by Carry-Look Ahead Adder                   | 45 |

|   | 3.4 | Evaluation of our Memristive Adders                                            | 52 |

|   |     | 3.4.1 Simulation results                                                       | 52 |

|   |     | 3.4.2 Discussion                                                               | 55 |

|   | 3.5 | Concluding Remarks                                                             | 55 |

| 4 |     | nristive Crossbar Architectures for Subtractor, Multiplier and Logical Modules | 56 |

|   | Wer |                                                                                |    |

|   | 4.1 | Introduction                                                                   | 57 |

|   |     |                                                                                |    |

iii

|   |      | · · · · · ·                                                     | •          |

|---|------|-----------------------------------------------------------------|------------|

|   |      |                                                                 | 61         |

|   | 4.3  | Logical Operations                                              | 53         |

|   |      | 4.3.1 NOT-operation                                             | 65         |

|   |      | 4.3.2 AND-operation                                             | 35         |

|   |      | 4.3.3 OR-Operation                                              | 37         |

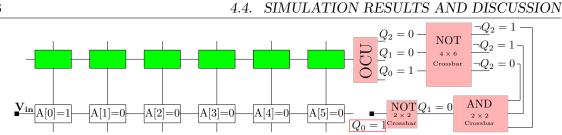

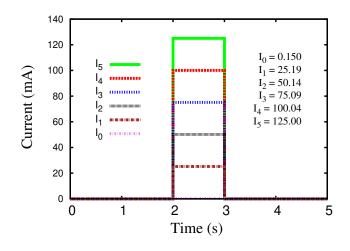

|   | 4.4  | Simulation Results and Discussion                               | 68         |

|   |      | 4.4.1 Results                                                   | <u>5</u> 8 |

|   |      | 4.4.2 Discussion                                                | 70         |

|   | 4.5  | Summary 7                                                       | 71         |

| 5 | Test | t Optimization in Full Memristive Crossbars 7                   | 72         |

|   | 5.1  | Introduction                                                    | 73         |

|   | 5.2  | Preliminaries                                                   | 73         |

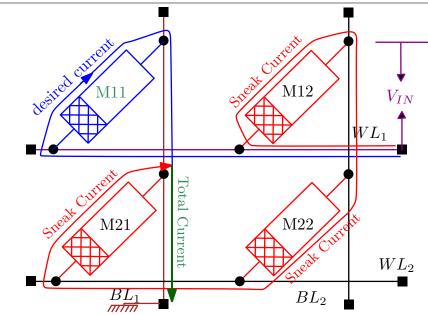

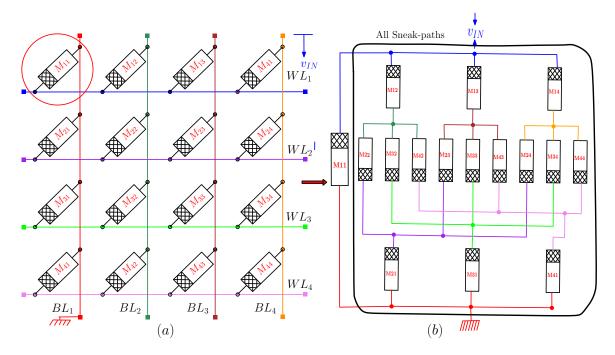

|   |      | 5.2.1 Sneak-path                                                | 73         |

|   |      | 5.2.2 Fault model                                               | 74         |

|   | 5.3  | Problem Formulation                                             | 76         |

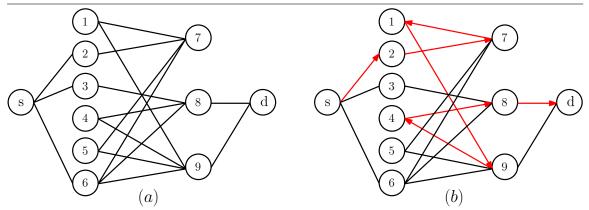

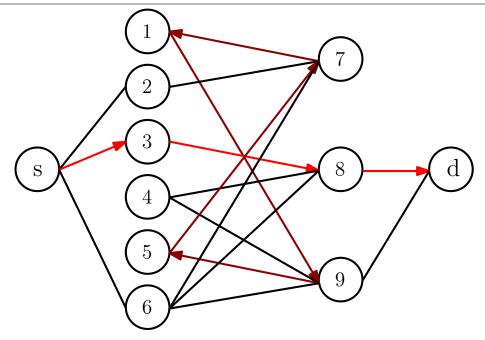

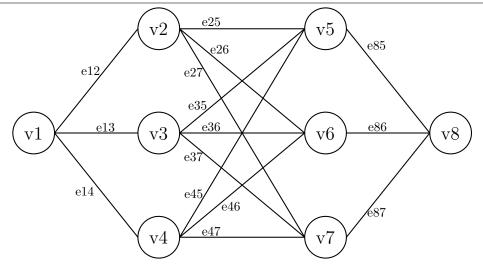

|   |      | 5.3.1 Problem statement for the sneak-path network              | 78         |

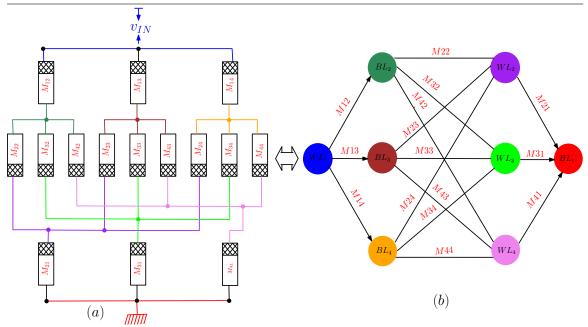

|   |      | 5.3.2 A graph-based formulation                                 | 78         |

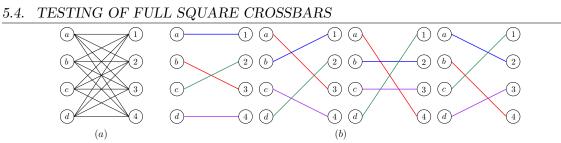

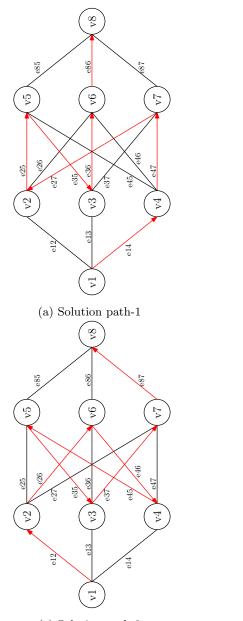

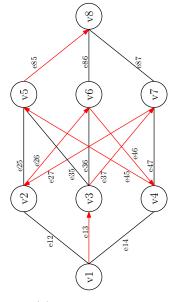

|   | 5.4  | Testing of Full Square Crossbars    6                           | 30         |

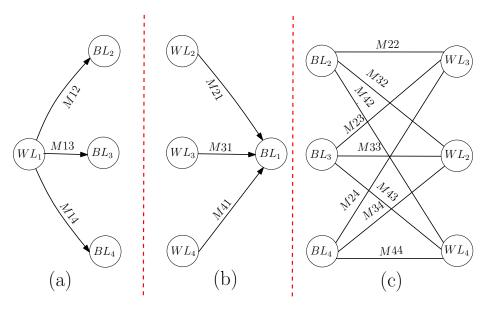

|   |      | 5.4.1 Graph decomposition                                       | 30         |

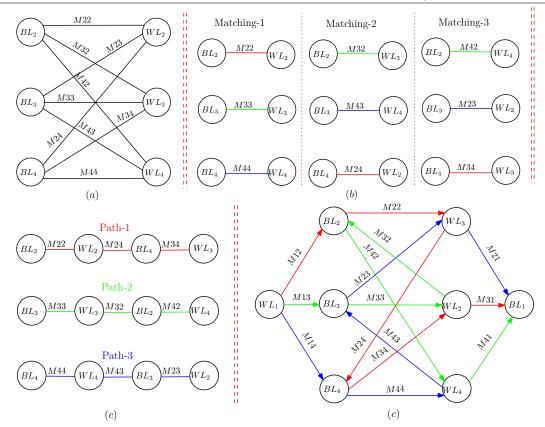

|   |      | 5.4.2 Square crossbar testing 8                                 | 31         |

|   |      | 5.4.3 Test Optimization by Multiple Paths Selection (TOMPS-Q) 8 | 87         |

|   | 5.5  | Testing of Full Rectangular Crossbars    6                      | 87         |

|   |      | 5.5.1 Test Optimization by Multiple Paths Selection (TOMPS-R) 9 | 91         |

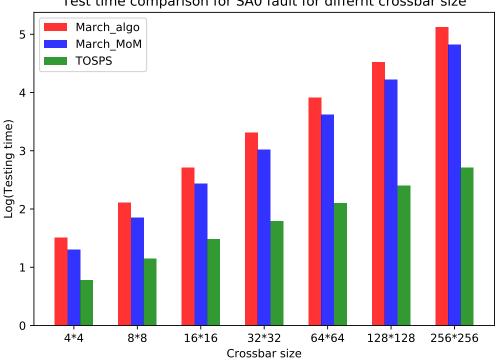

|   | 5.6  | Evaluation of the proposed methods                              | 92         |

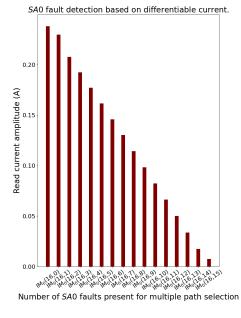

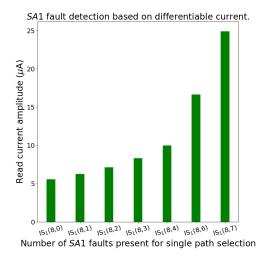

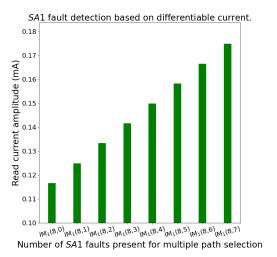

|   |      | 5.6.1 Simulation results                                        | 95         |

|   | 5.7  | Concluding Remarks                                              | 97         |

| 6 | Test | t Optimization in Incomplete Memristive Crossbars 10            | )1         |

|   | 6.1  | Introduction                                                    | )1         |

|   | 6.2  | Motivation                                                      | )2         |

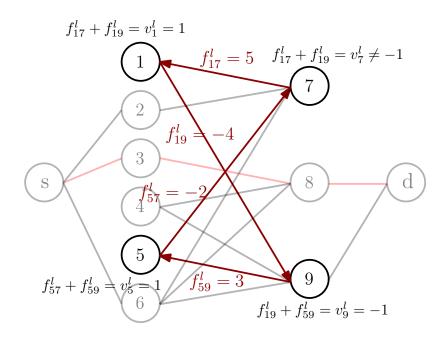

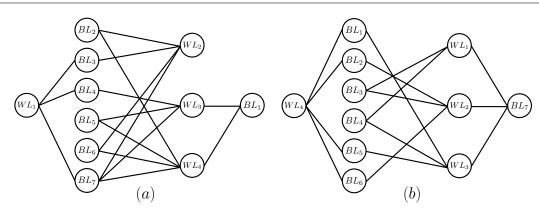

|   | 6.3  | ILP formulation                                                 | )3         |

|   |      | 6.3.1 Path construction                                         | )3         |

|   |      | 6.3.2 Disjoint path-loop removal                                | )5         |

|   |      | 6.3.3 Path minimization and formulation of the <i>ILP</i>       | )7         |

| Columna Colu | onten | ts       |                                                                          | v                   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|----------|--------------------------------------------------------------------------|---------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 6.4   | Evalu    | ation of the proposed methods                                            | 111                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 6.5   | Summ     | ary                                                                      | 112                 |

| 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Ana   | lysis of | Fault Sensitivity in Memristive Neural Architectures                     | 115                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 7.1   | Introd   | luction                                                                  | 116                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 7.2   | Prelin   | ninaries                                                                 | 117                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |       | 7.2.1    | Neural networks                                                          | 117                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |       | 7.2.2    | Faults in neural models                                                  | 117                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |       | 7.2.3    | Basics of fault-tolerance                                                | 118                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |       | 7.2.4    | Active and passive fault-tolerance                                       | 119                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 7.3   | Proble   | em Formulation                                                           | 120                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 7.4   | Overv    | iew of the proposed method                                               | 121                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 7.5   | Exper    | imental Evaluation                                                       | 122                 |

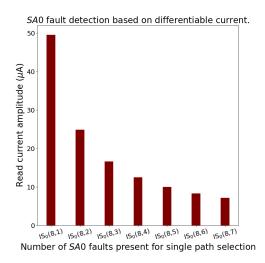

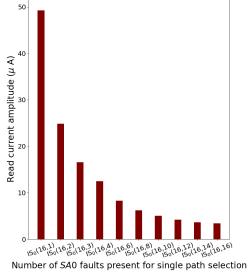

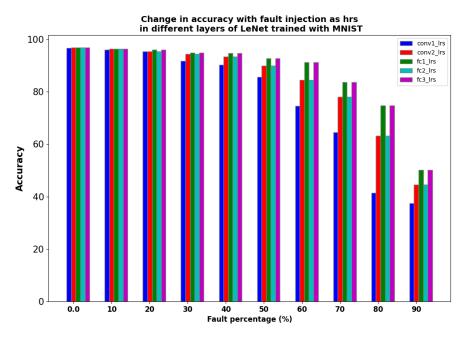

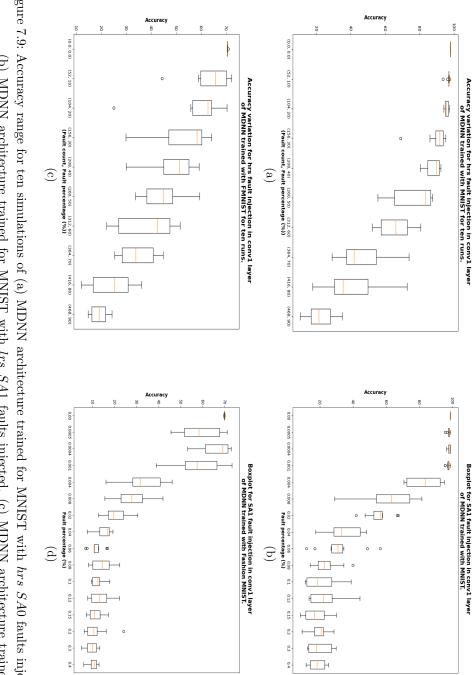

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |       | 7.5.1    | Effect of SA0 faults on accuracy                                         | 123                 |

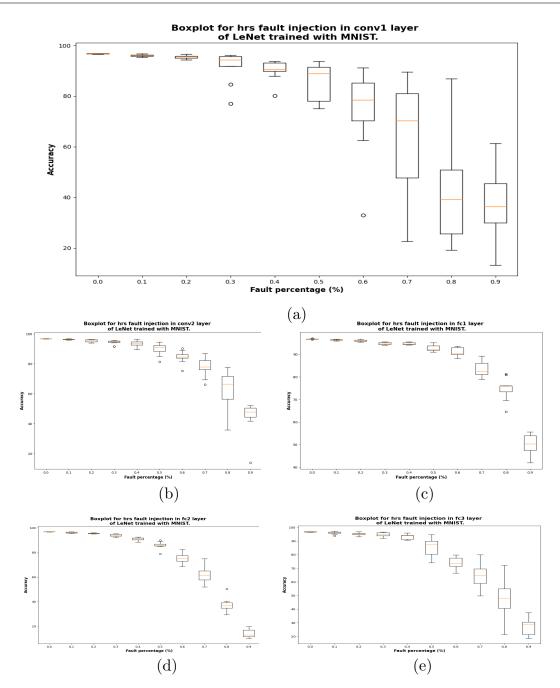

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |       | 7.5.2    | Effect of SA1 faults on accuracy                                         | 125                 |

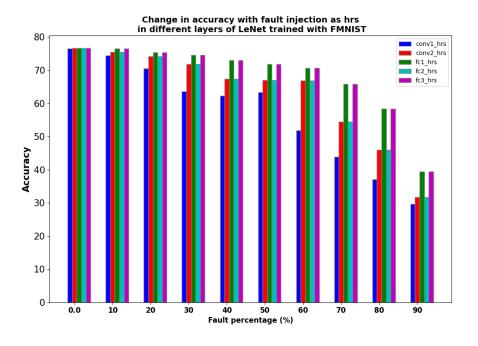

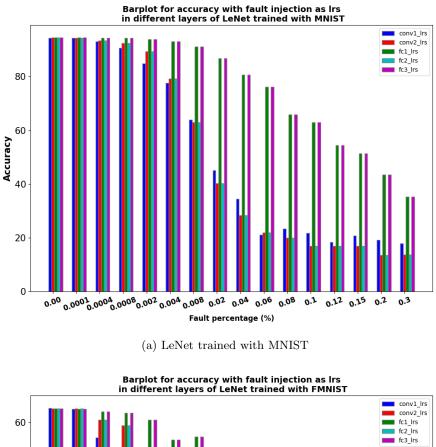

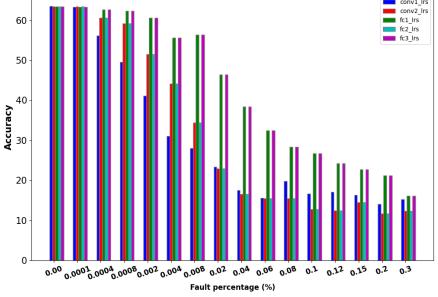

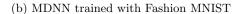

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |       | 7.5.3    | Layer-wise sensitivity analysis of LeNet architecture to fault locations | 129                 |

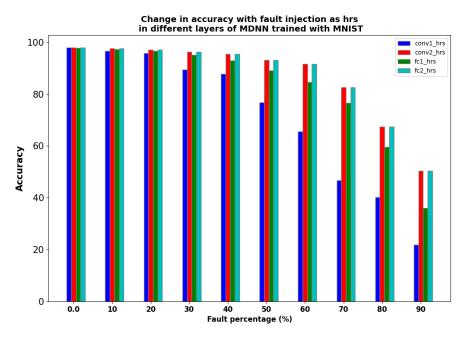

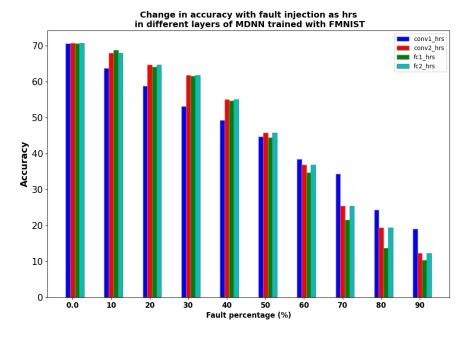

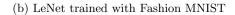

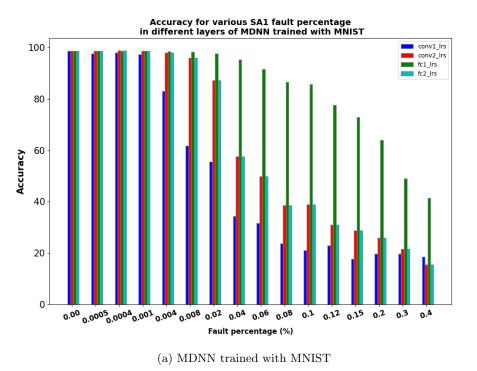

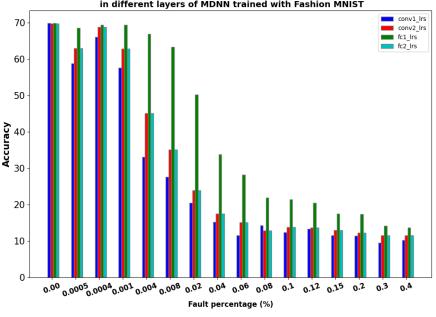

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |       | 7.5.4    | Layer-wise sensitivity analysis of MDNN architecture to fault location   | <mark>15</mark> 129 |

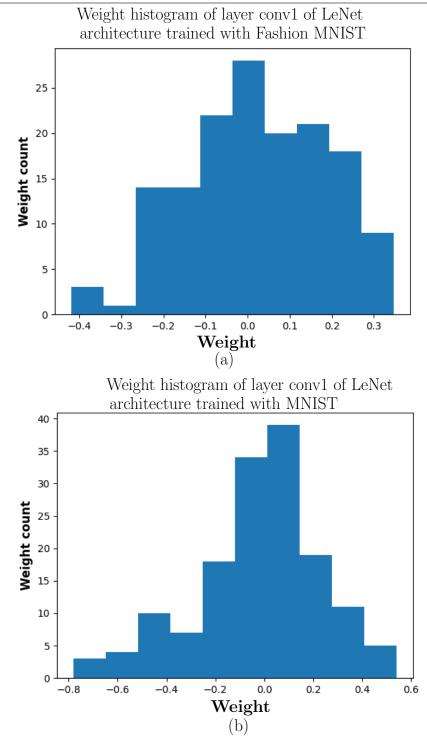

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |       | 7.5.5    | Distribution of weights in trained LeNet architecture                    | 129                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |       | 7.5.6    | Discussion on Experimental Results                                       | 130                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 7.6   | Concl    | uding Remarks                                                            | 130                 |

| 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Con   | clusion  | s and Future Directions                                                  | 136                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 8.1   | Summ     | ary                                                                      | 136                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 8.2   | Future   | e Directions                                                             | 138                 |

| Bi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | bliog | raphy    |                                                                          | 139                 |

# LIST OF PUBLICATIONS RELATED TO THIS THESIS

The thesis is based on the following publications of the author.

# In Journals

M. N. Mondal, S. Sur-Kolay and B. B. Bhattacharya, "Test Optimization in Memristor Crossbars Based on Path Selection," *IEEE Transactions on Computer-Aided Design* of Integrated Circuits and Systems, vol. 42, no. 1, pp. 294-307, Jan. 2023 doi: 10.1109/TCAD.2022.3168782

[2] M. N. Mondal, S. Sur-Kolay and B. B. Bhattacharya, "Scalable Design of Memristive ALU via Differential Current Sensing," to be submitted.

## In Peer-reviewed International Conference Proceedings

M. N. Mondal, S. Sur-Kolay and B. B. Bhattacharya, "Current Comparator-Based Reconfigurable Adder and Multiplier on Hybrid Memristive Crossbar," 2020 IEEE Computer Society Annual Symposium on VLSI (ISVLSI), 2020, pp. 494-499.

doi: 10.1109/ISVLSI49217.2020.000-8

[4] M. N. Mondal, S. Sur-Kolay and B. B. Bhattacharya, "Selective Sensitization of Useless Sneak-Paths for Test Optimization in Memristor-Arrays," 2019 32<sup>nd</sup> International Conference on VLSI Design and 2019 18th International Conference on Embedded Systems (VLSID), 2019, pp. 383-388. doi: 10.1109/VLSID.2019.00084

[5] M. N. Mondal, A. B. Chowdhury, S. Prajapati, S. Sur-Kolay and B. B. Bhattacharya, "Analysis of Fault Sensitivity in Memristive Neural Architectures," to be submitted.

# **LIST OF FIGURES**

| 1.1 | Relations among the four basic circuit elements in circuit theory (Chu71) .                                                                                                                                                                                                                                                                                                          | 4  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2 | (a) $Pt/TiO_2$ memristor proposed by HP Labs., (b) its equivalent resistive model                                                                                                                                                                                                                                                                                                    | 5  |

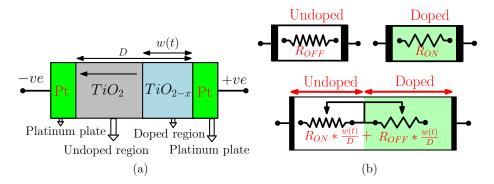

| 1.3 | Change in length of doped region due to application of external bias voltage.                                                                                                                                                                                                                                                                                                        | 5  |

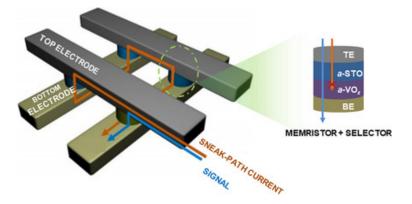

| 1.4 | Schematic illustration of a crossbar memory array with normal and sneak current paths                                                                                                                                                                                                                                                                                                | 6  |

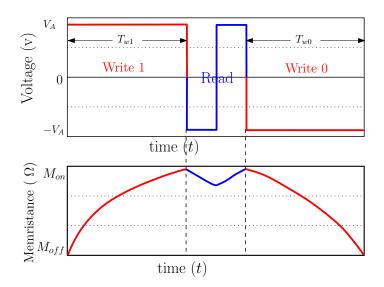

| 1.5 | Read and write operations in a memristor                                                                                                                                                                                                                                                                                                                                             | 7  |

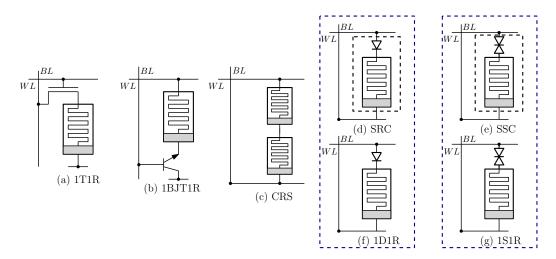

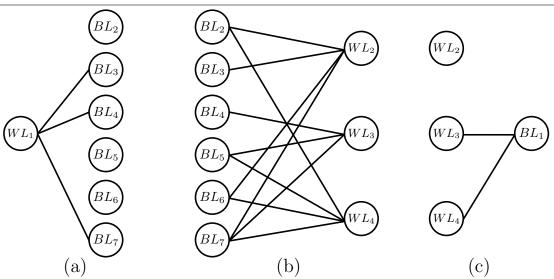

| 2.1 | Seven types of possible solutions to solve the sneak-path current issue (a) $1T1R$ (b) $1BJT1R$ (c) $CRS$ (d) $1D1R$ (e) $1S1R$ (f) SRC and (g) SSC, respectively.                                                                                                                                                                                                                   | 19 |

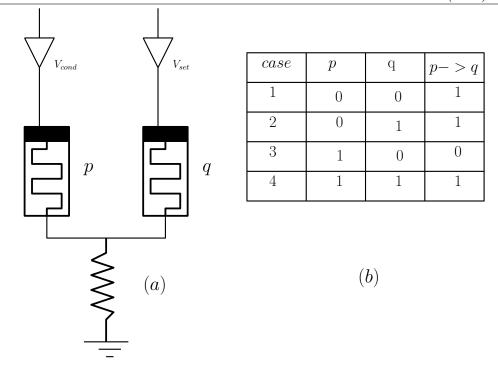

| 2.2 | (a) An IMPLY logic gate operates as follows: the initial states of memristors $p$ and $q$ serve as inputs to the logic gate, while the final state of memristor $q$ is the output, resulting from the application of voltages $V_{SET}$ and $V_{COND}$ .<br>Both memristors are connected to a load resistor $R_G$ . (b) The truth table of the IMPLY function (KSW <sup>+</sup> 14) | 25 |

| 2.3 | the IMPLY function (KSW <sup>+</sup> 14)                                                                                                                                                                                                                                                                                                                                             | 29 |

|     | for all input combinations (KBL <sup>+</sup> 14).                                                                                                                                                                                                                                                                                                                                    | 26 |

| 2.4  | Test locations and coverage for an SA1 fault with sneak paths (not shown); the red lines demarcate the $RoD$ , a dark blue square in a $RoD$ is the memory |     |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | element being sensitised and the gray region has other memory elements in                                                                                  |     |

|      | its RoD whose faults can also be sensed at the output (KKKS15). $\ldots$                                                                                   | 29  |

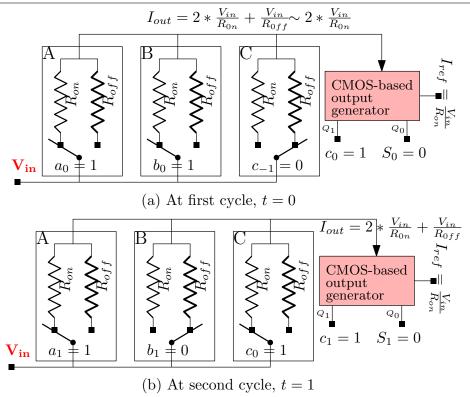

| 3.1  | Input connections of the resistive circuit for a 2-bit adder at (a) $t = 0$ and                                                                            |     |

|      | (b) $t = 1$ to add two 2-bit binary numbers A and B                                                                                                        | 35  |

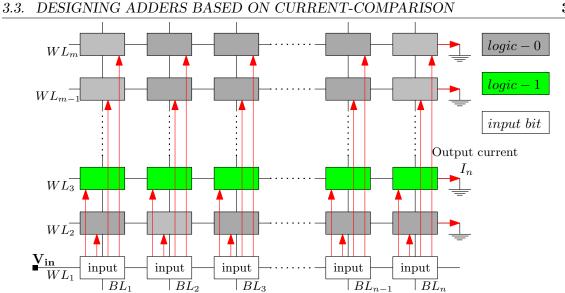

| 3.2  | Direction of current flow in the crossbar from $WL_1$ to $OCU$                                                                                             | 37  |

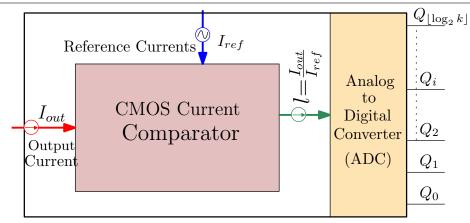

| 3.3  | Block diagram of an Output Computing Unit (OCU)                                                                                                            | 38  |

| 3.4  | Feeding binary inputs in the $t^{th}$ cycle for adding two unsigned binary 4-bit                                                                           |     |

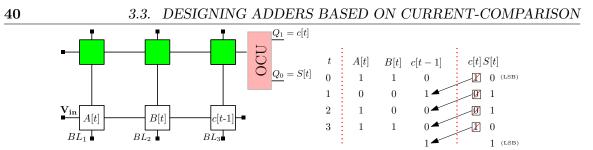

|      | numbers, and the corresponding five execution cycles                                                                                                       | 40  |

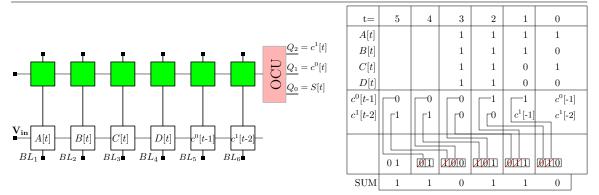

| 3.5  | Crossbar mapping and the execution cycles for adding four unsigned binary numbers                                                                          | 41  |

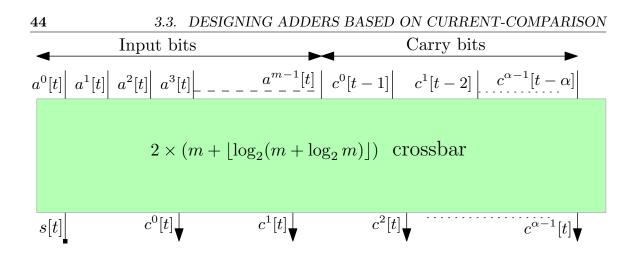

| 3.6  | Block diagram of a multi-operand adder inspired by CSA on a $2 \times (k + \alpha_k)$                                                                      | 4.4 |

| 27   | crossbar                                                                                                                                                   | 44  |

| 3.7  | Mapping on a $5 \times 8$ crossbar with four OCU units for generating carry-                                                                               | ۲1  |

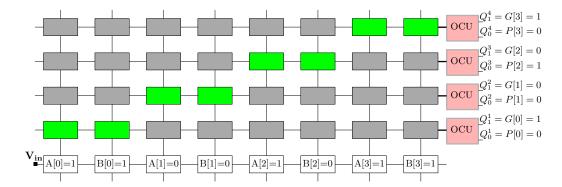

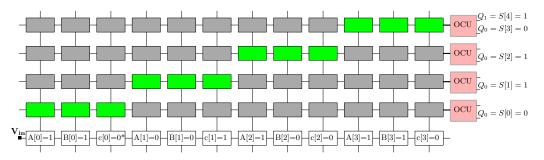

| 20   | propagate $(P[t])$ and carry-generate $(G[t])$ while adding two 4-bit numbers.                                                                             | 51  |

| 3.8  | Generation of carry bits $c[1]$ , $c[2]$ , $c[3]$ and $c[4]$ on a 5 × 8 crossbar                                                                           | 51  |

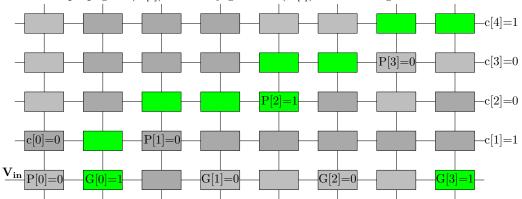

| 3.9  | Generation of the final sum bits $S = 10110$ on a $5 \times 12$ crossbar                                                                                   | 51  |

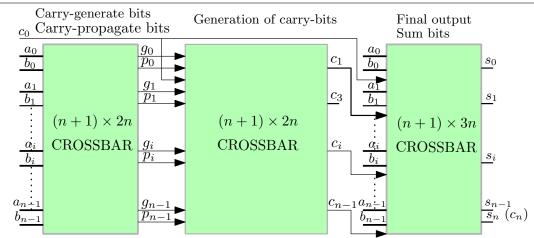

| 3.10 | Block diagram of a CLA-inspired <i>n</i> -bit adder                                                                                                        | 52  |

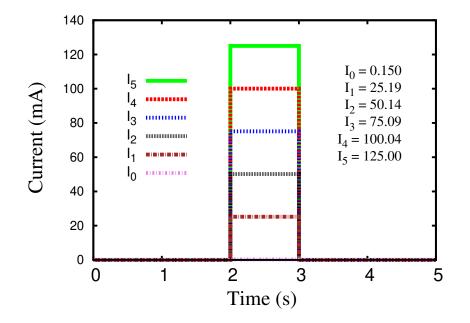

| 3.11 | Simulation results with five discrete current values                                                                                                       | 53  |

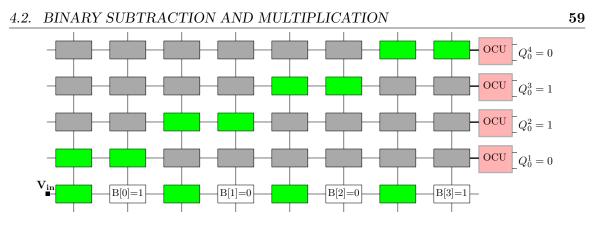

| 4.1  | Generation of 1's complement of $B$ , the subtrahend                                                                                                       | 59  |

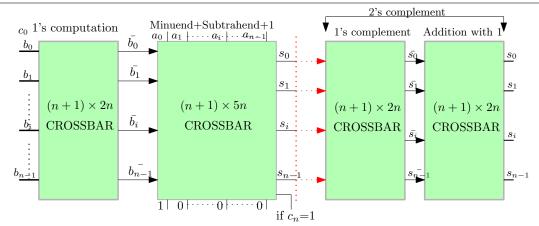

| 4.2  | Block diagram of an <i>n</i> -bit subtractor                                                                                                               | 61  |

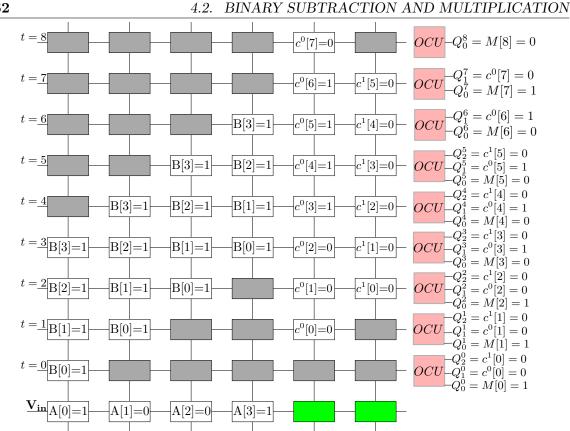

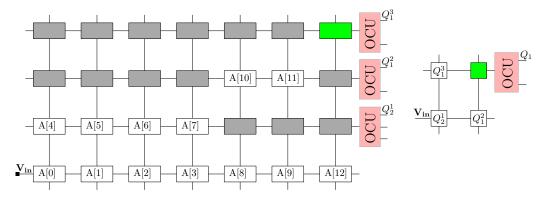

| 4.3  | A 4-bit multiplier on a $10 \times 6$ memristive crossbar $\ldots \ldots \ldots \ldots \ldots$                                                             | 62  |

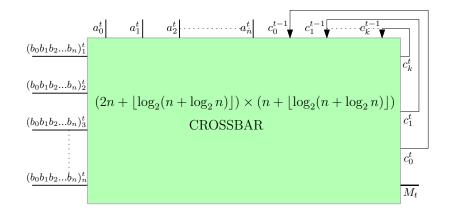

| 4.4  | Block diagram of a multiplier for two <i>n</i> -bit numbers                                                                                                | 64  |

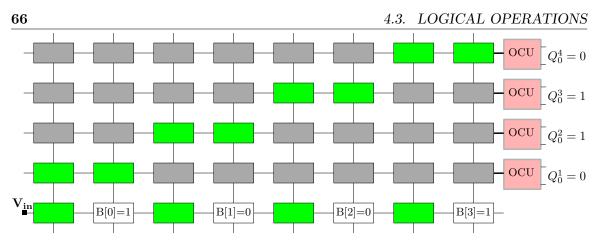

| 4.5  | Word-level NOT-operation on $B = 1001 \dots \dots \dots \dots \dots \dots \dots \dots$                                                                     | 66  |

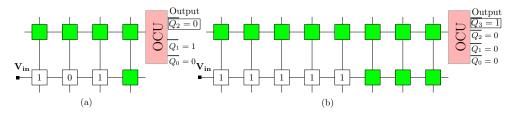

| 4.6  | Implementing bitwise AND-operation for (a) the word $y_1 = 101$ with output                                                                                |     |

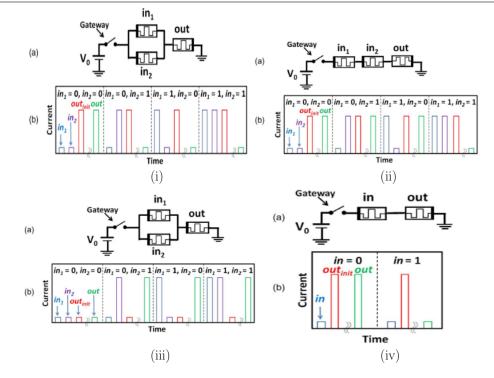

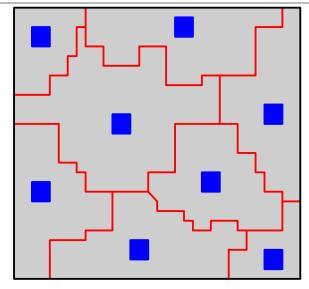

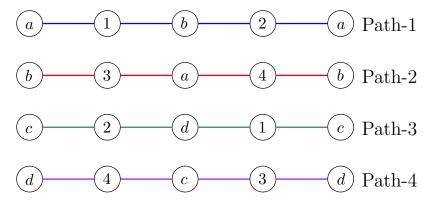

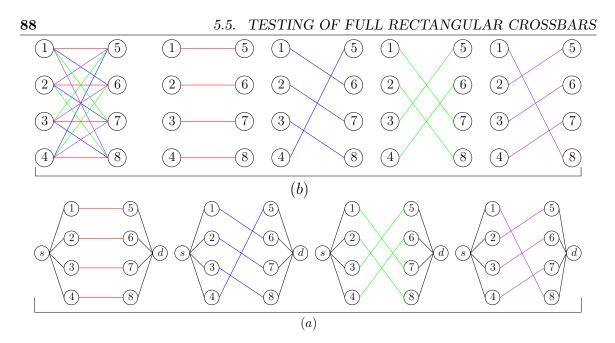

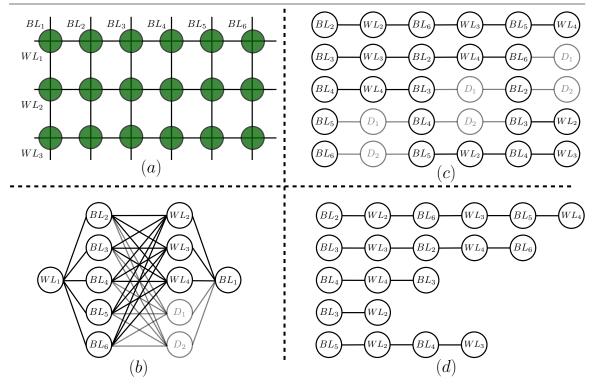

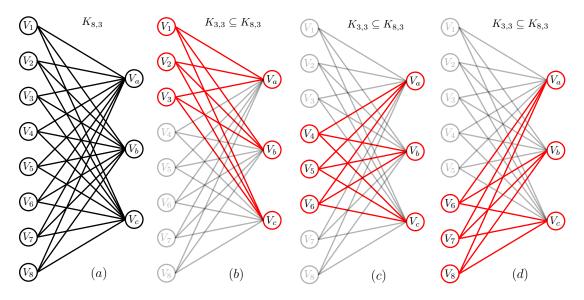

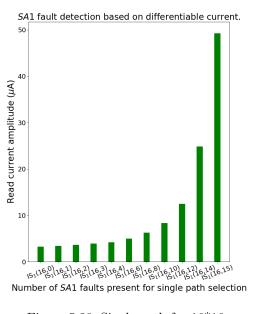

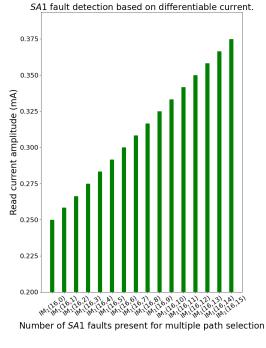

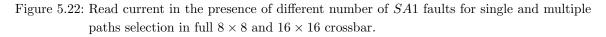

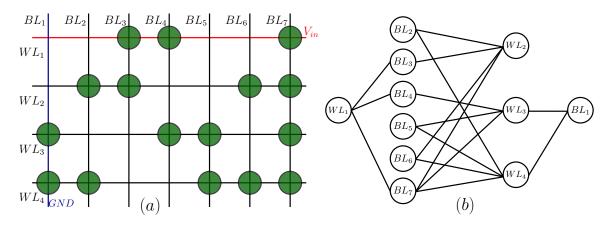

|      | $Q_2 = 0$ and (b) the word $y_2 = 1111$ with output $Q_3 = 1$                                                                                              | 66  |