# Fast Placement and Floorplanning Methods in Modern Reconfigurable FPGAs

Doctoral dissertation submitted by

# Pritha Banerjee

for award of the Ph.D. degree of the

# Indian Statistical Institute, Kolkata

Advisor:

Professor Susmita Sur-Kolay

Advanced Computing and Microelectronics Unit Indian Statistical Institute 203, B. T. Road, Kolkata, INDIA 700 108 June 2009 Dedicated to

my parents

Although a thesis is known by the name of its author, there are many without whose direct or indirect help, a thesis does not materialize. It is time to thank them.

First and the foremost, I am profoundly grateful to my supervisor Dr. Susmita Sur-Kolay for her constant motivation, guidance and advices throughout this work with patience.

I would like to express my gratitude towards Prof. Subhas C. Nandy, Dr. Sandip Das, Dr. Arijit Bishnu and Subasis Bhattacharjee for the numerous technical discussions we had and their motivation during this period. I thank my co-authors Megha Sangtani and Debasri Saha.

I would like to thank Indian Statistical Institute for providing me the financial support through fellowship and job assignments, which made this work successful. My thank goes to all the members of the faculty, office staff and my colleagues of Advanced Computing and Microelectronics Unit for making this unit a cordial and wonderful place to work.

I consider myself to be fortunate to have met my friends Partha, Sasanka, Subhasis, Debasis, Sandeep, Arindam, Gautam, Buddha da, Nilanjana, Sruti, Sahadeb, Sudip and many others, whose support, encouragement and willingness to listen made things bearable during difficult times and delightful the rest of the times during these years.

I would like to give a special acknowledgement to my husband, without whose help, patience and encouragement I would not have completed this work. I am also thankful to my parents-in-law for their support and encouragement during these years. Last but not the least, I thank my Grandmother, Mother, Father, Brothers -Partho, Argho, and my aunts Manju Chatterjee and Late Gopa Mukherjee for their support, encouragement, patience, faith and love which made this work a success.

(Pritha Banerjee)

June 1, 2009Advanced Computing and Microelectronics Unit,Indian Statistical Institute,203 B T Road, KolkataPin 700 108, India

# Contents

| 1        | Intr                 | oductio | on                                                                                                                                          | 1         |

|----------|----------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------|-----------|

|          | 1.1                  | FPGA    |                                                                                                                                             | 1         |

|          | 1.2                  | Compo   | onents of a basic FPGA chip                                                                                                                 | 3         |

|          | 1.3                  | Types   | of FPGA                                                                                                                                     | 5         |

|          |                      | 1.3.1   | Structural classification                                                                                                                   | 6         |

|          |                      | 1.3.2   | Programming technology based classification                                                                                                 | 7         |

|          |                      | 1.3.3   | Modern FPGAs                                                                                                                                | 8         |

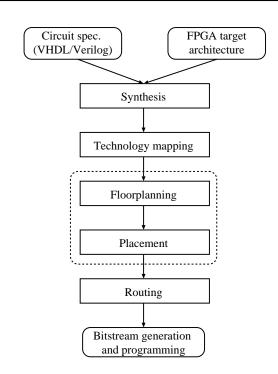

|          | 1.4                  | Design  | flow for FPGA                                                                                                                               | 9         |

|          | 1.5                  | Scope   | of the thesis                                                                                                                               | 12        |

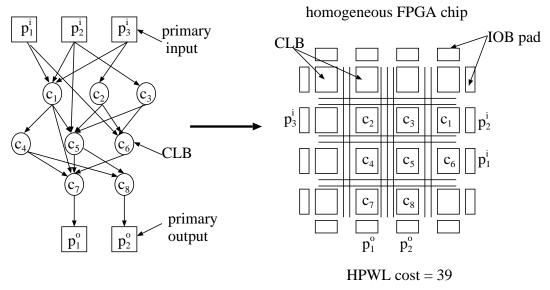

|          |                      | 1.5.1   | Placement of CLBs on island-style homogeneous FPGAs                                                                                         | 13        |

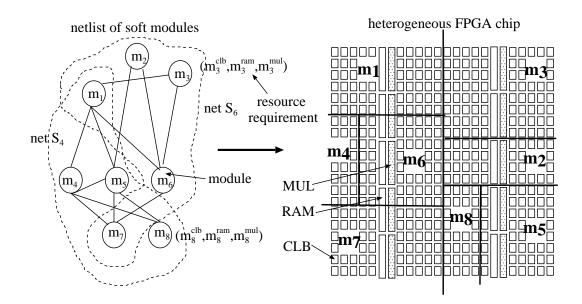

|          |                      | 1.5.2   | Floorplanning for heterogeneous FPGAs                                                                                                       | 15        |

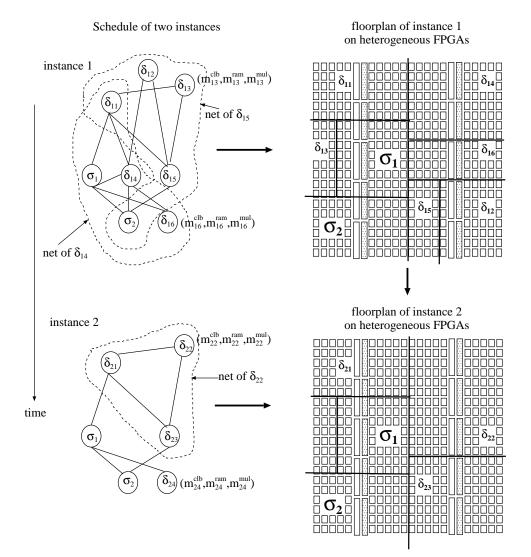

|          |                      | 1.5.3   | Floorplanning for partial reconfiguration in heterogeneous FP-                                                                              |           |

|          |                      |         | GAs                                                                                                                                         | 17        |

|          | 1.6                  | Organi  | zation                                                                                                                                      | 18        |

| <b>2</b> | $\mathbf{Pre}$       | vious V | Vorks                                                                                                                                       | <b>21</b> |

|          | 2.1                  | Placem  | nent on island-style FPGAs                                                                                                                  | 21        |

|          |                      | 2.1.1   | Stochastic methods                                                                                                                          | 22        |

|          |                      | 2.1.2   | Partitioning based placement                                                                                                                | 25        |

|          |                      | 2.1.3   | Analytical placement                                                                                                                        | 26        |

|          |                      | 2.1.4   | Other placement techniques                                                                                                                  | 28        |

|          |                      | 2.1.5   | Summary                                                                                                                                     | 30        |

|          | 2.2                  | Floorp  | lanning for heterogeneous FPGAs                                                                                                             | 31        |

|          |                      | 2.2.1   | Summary                                                                                                                                     | 33        |

|          | 2.3                  | Floorp  | lanning for partial reconfiguration                                                                                                         | 34        |

|          |                      | 2.3.1   | Summary                                                                                                                                     | 35        |

|          | 2.4                  | Conclu  | $sion \ldots \ldots$ | 36        |

| 3        | $\operatorname{Bot}$ | tom-up  | O Cone based Placement for Island-style FPGAs                                                                                               | 37        |

|          | 3.1                  | Introdu | uction                                                                                                                                      | 38        |

|          | 3.2                  | Backgr  | ound                                                                                                                                        | 38        |

|          |                      | 3.2.1   | Overview of our method                                                                                                                      | 39        |

|          | 3.3                  | ConeC   | <i>LBPlace</i> : Cone based CLB placement                                                                                                   | 40        |

|          |                      | 3.3.1   | Placement of output blocks                                                                                                                  | 40        |

|   |     | 3.3.2  | Construction of an <i>output cone</i> for placement of CLBs       | 40 |

|---|-----|--------|-------------------------------------------------------------------|----|

|   |     | 3.3.3  | Placement of CLBs and input blocks                                | 41 |

|   |     | 3.3.4  | Illustration of CLB placement by <i>ConeCLBPlace</i>              | 43 |

|   |     | 3.3.5  | Time complexity of <i>ConeCLBPlace</i>                            | 44 |

|   |     | 3.3.6  | Iterative improvement of placement                                | 46 |

|   | 3.4 | ConeI  | <i>OBPlace</i> : Cone based IOB placement                         | 47 |

|   |     | 3.4.1  | Phase I: Generation of circular arrangement of IOBs $\ . \ . \ .$ | 49 |

|   |     | 3.4.2  | Phase II: Computation of separation between adjacent IOB          |    |

|   |     |        | positions                                                         | 52 |

|   |     | 3.4.3  | Illustration of IOB placement by <i>ConeIOBPlace</i>              | 53 |

|   |     | 3.4.4  | Time complexity of <i>ConeIOBPlace</i>                            | 53 |

|   |     | 3.4.5  | Placement of CLBs                                                 | 55 |

|   | 3.5 | ConeF  | Place: Cone based IOB and CLB placement                           | 56 |

|   | 3.6 | Exper  | imental results                                                   | 56 |

|   |     | 3.6.1  | Placement obtained by <i>ConeCLBPlace</i>                         | 57 |

|   |     | 3.6.2  | Placement obtained by <i>ConeIOBPlace</i>                         | 58 |

|   |     | 3.6.3  | Placement obtained by <i>ConePlace</i>                            | 59 |

|   | 3.7 | Conclu | 1sion                                                             | 62 |

| 4 | Top | o-Down | Deterministic FPGA Placement                                      | 65 |

|   | 4.1 | Introd | uction                                                            | 65 |

|   | 4.2 | Overv  | iew                                                               | 66 |

|   | 4.3 | Coarse | e grain placement                                                 | 68 |

|   |     | 4.3.1  | Partitioning of CLB netlist                                       | 68 |

|   |     | 4.3.2  | Allocation of <i>netlist partitions</i> to <i>regions</i>         | 69 |

|   |     | 4.3.3  | Reallocation in overloaded regions                                | 71 |

|   |     | 4.3.4  | Placement of IOBs                                                 | 72 |

|   |     | 4.3.5  | Time complexity of <i>Coarse grain</i> method                     | 73 |

|   | 4.4 | Fine g | rain placement                                                    | 74 |

|   |     | 4.4.1  | Fine grain partitioning                                           | 74 |

|   |     | 4.4.2  | Recursive space filling curve                                     | 75 |

|   |     | 4.4.3  | Placement using space filling curve                               | 77 |

|   |     | 4.4.4  | Time Complexity of <i>Fine grain</i> method                       | 78 |

|   | 4.5 | Exper  | imental results for top-down deterministic FPGA placement         | 78 |

|   |     |        |                                                                   |    |

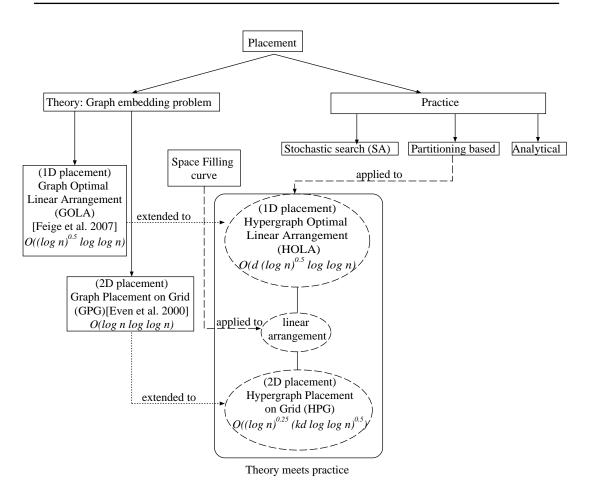

| <b>5</b> | Effi | cient l | FPGA Placement using Space Filling Curves:                                 | Theory       |

|----------|------|---------|----------------------------------------------------------------------------|--------------|

|          | Mee  | ets Pra | actice                                                                     | 85           |

|          | 5.1  | Introd  | uction                                                                     | 85           |

|          |      | 5.1.1   | FPGA placement: theory and practice                                        | 86           |

|          | 5.2  | Our co  | ontribution                                                                | 87           |

|          | 5.3  | Graph   | embedding and approximation algorithms $\ldots \ldots$                     |              |

|          | 5.4  | Appro   | ximation algorithms for FPGA placement                                     | 92           |

|          |      | 5.4.1   | Extending approximation algorithms for graphs to hyp                       | pergraphs 92 |

|          |      | 5.4.2   | Approximation algorithm for HPG using space filling                        | curve . 94   |

|          | 5.5  | The al  | gorithm in practice                                                        | 99           |

|          |      | 5.5.1   | Computation of linear arrangement                                          | 99           |

|          |      | 5.5.2   | Placement by space filling curves                                          | 100          |

|          |      | 5.5.3   | Placement of IOBs                                                          | 100          |

|          | 5.6  | Exper   | imental results                                                            | 101          |

|          |      | 5.6.1   | Quality of placement $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 101          |

|          |      | 5.6.2   | Effect of low temperature SA                                               | 103          |

|          | 5.7  | Conclu  | usion                                                                      | 104          |

| 6        | Uni  | fied F  | loorplan Topology Generation and Sizing on H                               | eteroge-     |

|          |      | us FP0  |                                                                            | 107          |

|          | 6.1  | Introd  | uction                                                                     | 108          |

|          | 6.2  | Backg   | round                                                                      | 109          |

|          |      | 6.2.1   | Architecture                                                               | 109          |

|          |      | 6.2.2   | FPGA floorplanning problem                                                 | 109          |

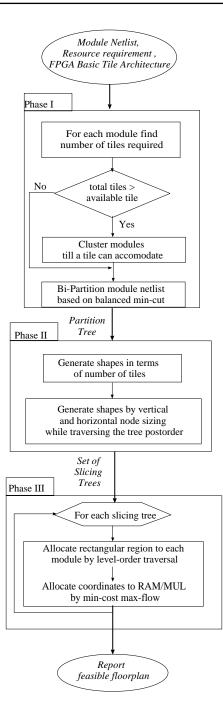

|          |      | 6.2.3   | Proposed floorplanning method                                              | 111          |

|          |      | 6.2.4   | Basic tile of a FPGA architecture                                          | 113          |

|          |      | 6.2.5   | Clustering step for large number of small modules .                        | 117          |

|          | 6.3  | Phase   | I: Generation of partition tree                                            | 117          |

|          | 6.4  | Phase   | II: Floorplan topology generation                                          | 118          |

|          |      | 6.4.1   | Generation of module shapes                                                | 118          |

|          |      | 6.4.2   | Generation of slicing trees                                                | 120          |

|          | 6.5  | Phase   | III: Realization of slicing tree on target FPGA                            | 122          |

|          |      | 6.5.1   | Greedy allocation of rectangular region (GARR) $$                          | 122          |

|          |      | 6.5.2   | Allocation of RAM and MUL                                                  | 123          |

|          |      | 6.5.3   | Time complexity of <i>HeteroFloorplan</i>                                  | 127          |

|          | 6.6  | An exa  | ample                                                                      | 128          |

|          | 6.7  | Exper   | imental results                                                            | 131          |

|          |      |         |                                                                            |              |

|    | 6.8   | How good is our GARR?                                       | 36 |

|----|-------|-------------------------------------------------------------|----|

|    |       | 6.8.1 Max-flow formulation for CLB allocation               | 36 |

|    |       | 6.8.2 Comparison of GARR with network flow method 1         | 38 |

|    | 6.9   | Conclusion                                                  | 40 |

| 7  | Flo   | orplanning for Partial Reconfiguration in FPGAs 14          | 41 |

|    | 7.1   | Introduction                                                | 41 |

|    | 7.2   | Floorplanning for partial reconfiguration                   | 43 |

|    |       | 7.2.1 Overview of proposed method                           | 44 |

|    |       | 7.2.2 Basic tile on FPGA chip                               | 45 |

|    | 7.3   | Phase I: Generation of partition trees                      | 45 |

|    | 7.4   | Phase II: Global floorplan topology generation              | 48 |

|    | 7.5   | Phase III: Realization of slicing trees on the chip 1       | 51 |

|    |       | 7.5.1 Allocation of rectangular region to a module          | 51 |

|    |       | 7.5.2 Pruning the set of slicing trees                      | 53 |

|    |       | 7.5.3 Grouping of slicing trees for global floorplan        | 54 |

|    |       | 7.5.4 Postprocessing for satisfying resource requirements 1 | 57 |

|    | 7.6   | An example                                                  | 60 |

|    | 7.7   | Experimental results                                        | 64 |

|    | 7.8   | Conclusion                                                  | 66 |

| 8  | Cor   | cluding Remarks 10                                          | 67 |

|    | 8.1   | Summary of the contributions                                | 67 |

|    | 8.2   | Future directions                                           | 68 |

| Bi | bliog | graphy 10                                                   | 69 |

| Pι | ıblic | ations from the Thesis                                      | 79 |

# List of Tables

| 1.1 | Summary of FPGA architectures provided by different companies                   | 7   |

|-----|---------------------------------------------------------------------------------|-----|

| 3.1 | An example: Adjacency matrix representing the block netlist graph               |     |

|     | $D^b$ , the netlist of CLBs and IOBs; $p^i$ , $p^o$ and $c$ denote the primary  |     |

|     | input blocks, primary output blocks and CLBs respectively                       | 43  |

| 3.2 | Characteristics of MCNC FPGA placement benchmark circuits                       | 56  |

| 3.3 | Comparison of wirelength driven BB cost: ConeCLBPlace vs. VPR $% \mathcal{A}$ . | 57  |

| 3.4 | Comparison of <i>critical path delay</i> : <i>ConeCLBPlace</i> vs. VPR          | 58  |

| 3.5 | Comparison of wirelength driven BB cost: ConeIOBPlace vs. VPR $\cdot$ .         | 59  |

| 3.6 | Comparison of <i>critical path delay</i> : ConeIOBPlace vs. VPR                 | 60  |

| 3.7 | Comparison of <i>BB cost: ConePlace</i> vs. VPR                                 | 61  |

| 3.8 | Comparison of <i>speedup</i> : <i>ConePlace</i> vs. VPR                         | 61  |

| 3.9 | Comparison of <i>critical path delay: ConePlace</i> vs. VPR                     | 62  |

| 4.1 | Characteristics of MCNC FPGA placement benchmark circuits                       | 78  |

| 4.2 | Placement results for wirelength driven VPR                                     | 79  |

| 4.3 | Comparison of $GL\%$ between timing driven VPR and wirelength driven            |     |

|     | VPR                                                                             | 80  |

| 4.4 | Comparison of $GL\%$ (Initial BB Cost) by our method vs. Final BB               |     |

|     | Cost by VPR; [H:Hilbert, Z:Z, S:Snake]                                          | 81  |

| 4.5 | Comparison of $GL\%$ (Final BB Cost) of our methods vs. VPR $~$                 | 82  |

| 4.6 | Speedup of our methods over VPR in terms of $GL\%$ (SA moves) and               |     |

|     | ratio of CPU times; [H:Hilbert, Z:Z, S:Snake]                                   | 83  |

| 4.7 | Comparison of $GL\%$ (Critical path delay) of our methods over VPR              | 83  |

| 5.1 | Characteristics of MCNC FPGA placement benchmark circuits                       | 101 |

| 5.2 | Comparison of HPWL cost, speedup and critical path delay                        | 103 |

| 5.3 | Comparison of $HPWL \ cost$ and $CPU \ time$ for $SFC + SA$ and $VPR$           | 105 |

| 5.4 | Comparison of <i>critical path delay</i>                                        | 106 |

| 6.1 | Floorplan results for 20-module example [Cheng 2004]                            | 129 |

| 6.2 | Benchmark circuits, C: CLB, R:RAM, M:MUL                                        | 132 |

| 6.3 | Comparison of wirelength (HPWL <i>a la</i> ASIC): <i>HeteroFloorplan</i> vs.    |     |

|     | [Feng 2006]; Case I: center-to-center; Case II: terminals on periphery          | 132 |

| 6.4 | Comparison of wirelengths (HPWL): HeteroFloorplan vs. [Cheng 2006]              | 134 |

| 6.5 | Comparison of CPU time; [CF: Constrained Floorplanning]                  | 136 |

|-----|--------------------------------------------------------------------------|-----|

| 6.6 | Similarity of CLB allocation by GARR in <i>HeteroFloorplan</i> with net- |     |

|     | work flow based method                                                   | 139 |

| 7.1 | Characteristics of benchmark; [SM: Static modules]                       | 165 |

| 7.2 | Comparison of HPWL, CPU time and reconfiguration overhead; Par-          |     |

|     | tialHeteroFP gives 100% overlap of SM                                    | 165 |

# List of Figures

| 1.1 | Basic FPGA architecture.                                                               | 4    |

|-----|----------------------------------------------------------------------------------------|------|

| 1.2 | Types of FPGA architecture.                                                            | 5    |

| 1.3 | Modern FPGA architecture with Block RAM and Multipliers                                | 8    |

| 1.4 | CAD flow for FPGAs; the rectangle with dashed lines shows the scope                    |      |

|     | of this thesis.                                                                        | 11   |

| 1.5 | The placement problem for FPGAs with CLBs and IOBs. $\ldots$ .                         | 14   |

| 1.6 | The floorplanning problem for FPGAs with <i>heterogeneous</i> resources;               |      |

|     | net $S_4$ and $S_6$ are the <i>nets</i> consisting of modules $\{m_1, m_4, m_5, m_7\}$ |      |

|     |                                                                                        | 16   |

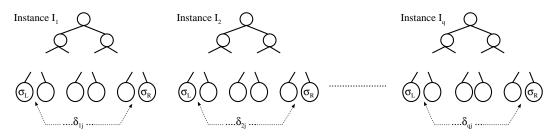

| 1.7 | The floorplanning problem for partial reconfiguration in FPGAs with                    |      |

|     | heterogeneous resources; $\sigma$ : common (static) modules, $\delta$ : dynamic        | 1 🗖  |

| 1 0 |                                                                                        | 17   |

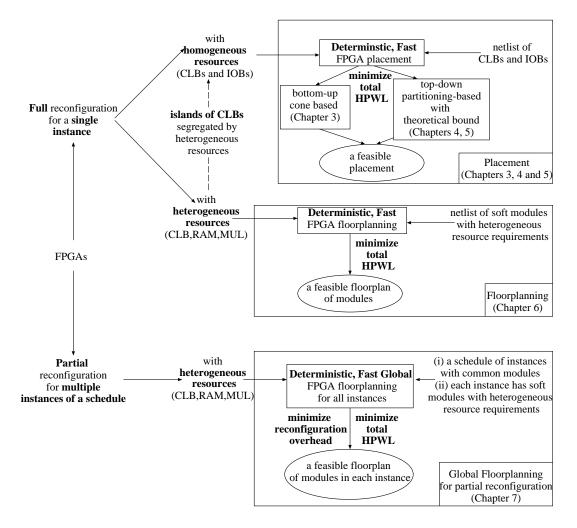

| 1.8 | The organization of this thesis.                                                       | 19   |

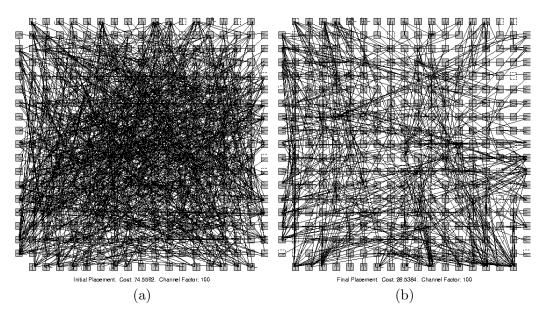

| 2.1 | An example of placement [Betz 1999]: (a) random initial placement of                   |      |

|     | netlist of CLBs and IOBs, (b) final placement minimizing <i>linear con-</i>            |      |

|     | gestion $cost$ (note the reduction in congestion); (Courtesy: [Betz 1999]).            | 22   |

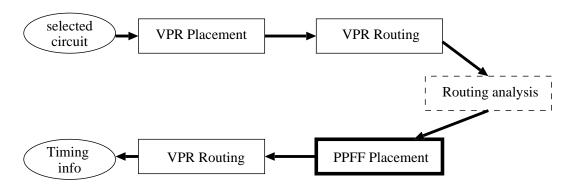

| 2.2 | Flow of PPFF [Maidee 2003, Maidee 2005].                                               | 26   |

| 2.3 | Overview of CAPRI (Courtesy: [Gopalakrishnan 2006])                                    | 28   |

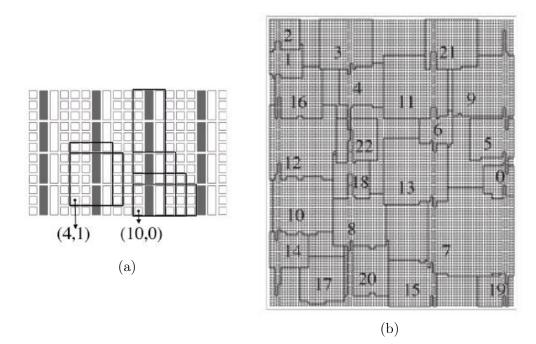

| 2.4 | Example of floorplan obtained by [Cheng 2004, Cheng 2006]. (a) Pos-                    |      |

|     | sible <i>irreducible realization list</i> (IRL)s for two modules (b) a rectilin-       |      |

|     | ear floorplan after compaction (Courtesy: [Cheng 2004, Cheng 2006]).                   | 32   |

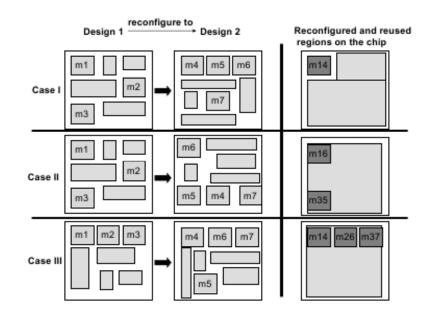

| 2.5 | Partial reconfiguration proposed by Singhal and Bozorgzadeh [Singhal 200               | 06]; |

|     | case III shows the maximum overlap of common modules. (Courtesy:                       |      |

|     | [Singhal 2006])                                                                        | 34   |

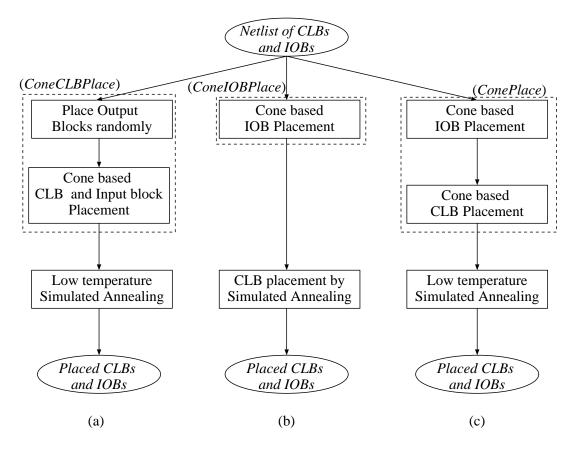

| 3.1 | Flow of our methods: (a) <i>ConeCLBPlace</i> ; (b) <i>ConeIOBPlace</i> ; (c)           |      |

|     | ConePlace.                                                                             | 40   |

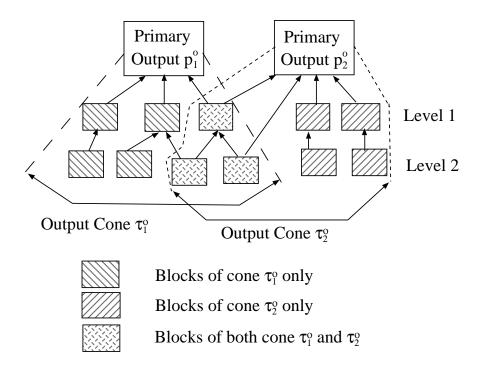

| 3.2 | Two <i>output cones</i> with overlap corresponding to two <i>primary output</i>        |      |

|     | blocks, $p_1^o$ and $p_2^o$                                                            | 42   |

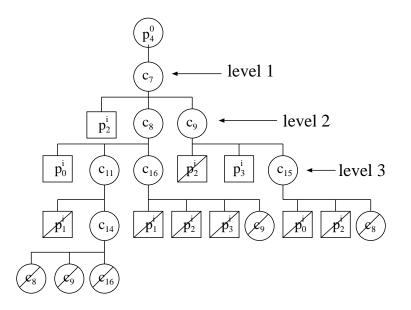

| 3.3 | Illustration of ConeCLBPlace: An output cone $\tau_4^o$ of primary output              |      |

|     | block $p_4^o$ of the netlist in Table 3.7                                              | 44   |

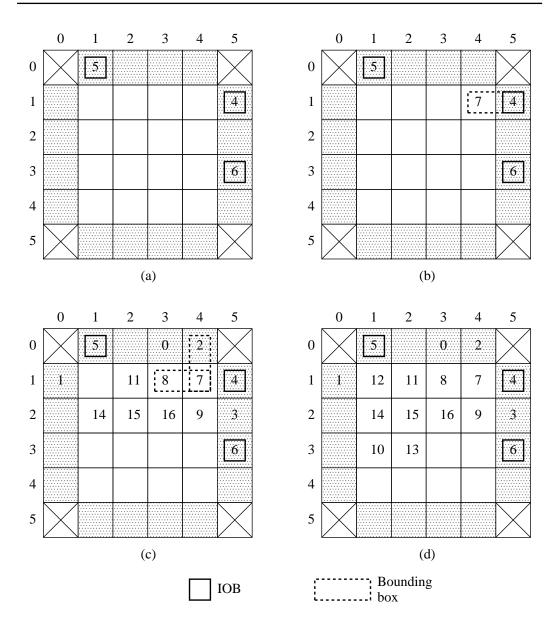

| 3.4 | Execution of $ConeCLBPlace$ on the example netlist of Table 3.1; (a)                                          |     |

|-----|---------------------------------------------------------------------------------------------------------------|-----|

|     | placement of IOBs; (b) placement of $c_7$ within the extended <i>bounding</i>                                 |     |

|     | box $BB_7$ ; (c) placement of all blocks in the cone $\tau_4^o$ ; (d) placement of                            |     |

|     | all blocks in the cones $\tau_4^o$ , $\tau_5^o$ and $\tau_6^o$ .                                              | 45  |

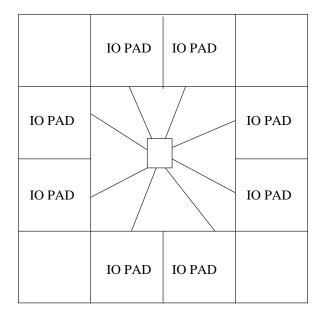

| 3.5 | Position of padframe in an FPGA.                                                                              | 47  |

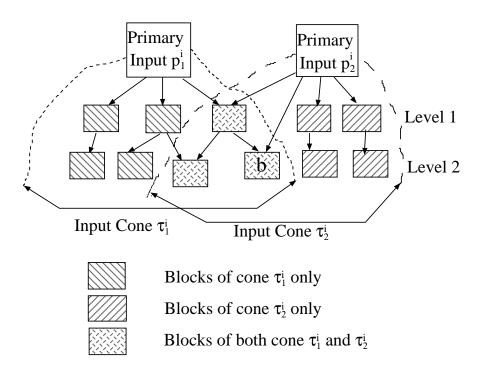

| 3.6 | Two <i>input cones</i> with overlap corresponding to two <i>primary input</i><br>blocks $p_1^i$ and $p_2^i$ . | 48  |

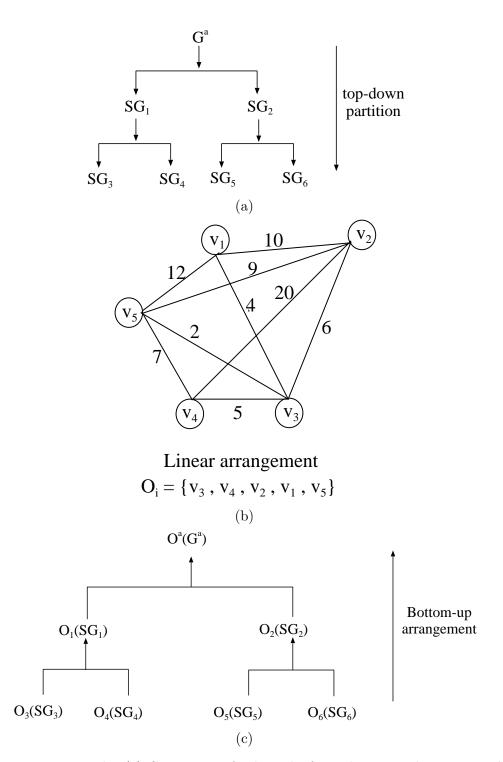

| 3.7 | Example: (a) Generation of subgraphs from the <i>cone adjacency graph</i> ;                                   |     |

| 0.1 | (b) Subgraph $SG_i$ for which <i>linear arrangement</i> $O_i$ of vertices is ob-                              |     |

|     | tained; (c) Generation of <i>circular arrangement</i> of IOBs from <i>linear</i>                              |     |

|     | arrangement of subgraphs                                                                                      | 54  |

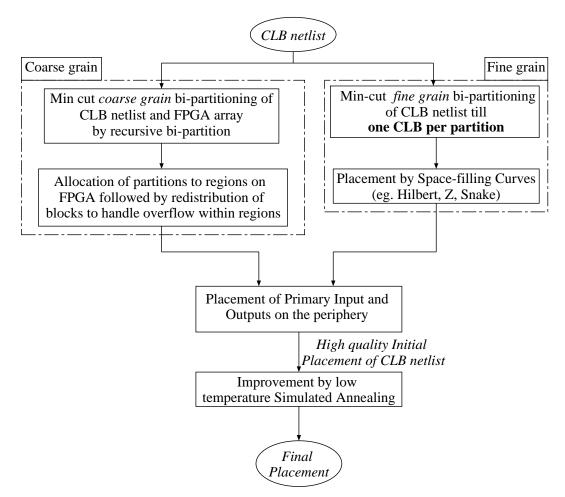

| 4.1 | Flow of our placement method: Coarse grain and Fine grain                                                     | 66  |

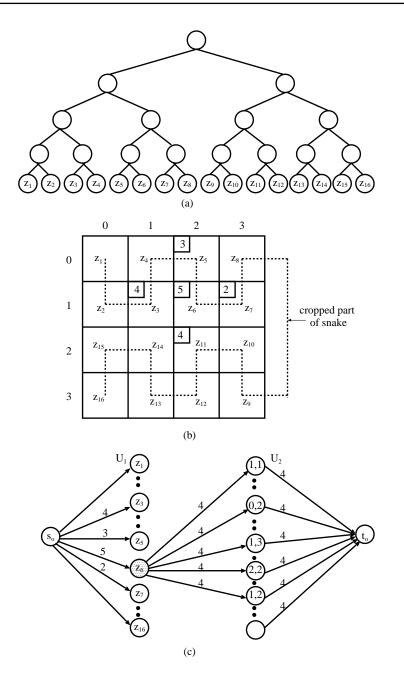

| 4.2 | Steps of <i>Coarse grain</i> method: (a) balanced <i>partition tree</i> with <i>netlist</i>                   |     |

|     | partitions at the leaves (b) assignment of <i>netlist partitions</i> to <i>regions</i>                        |     |

|     | on an FPGA in a $snake$ like fashion; each square corresponds to a                                            |     |

|     | region and is labeled by the <i>netlist partition</i> $z_i$ assigned to it; the                               |     |

|     | number of CLBs in each of the <i>netlist partitions</i> $z_3$ , $z_5$ , $z_7$ , $z_{12}$ and                  |     |

|     | $z_6$ , appears at the top left corner of the corresponding region (c)                                        |     |

|     | flow network for reallocation of CLBs from the overloaded <i>regions</i> to                                   | 70  |

| 4.0 | neighboring ones.                                                                                             | 70  |

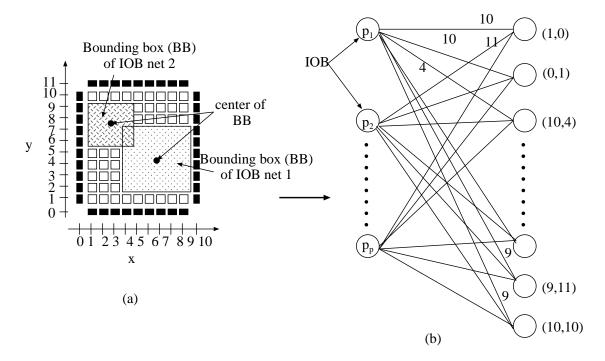

| 4.3 | Minimum weighted bi-partite matching formulation for placement of                                             |     |

|     | IOBs: (a) the bounding box of two IOB nets; (b) the bi-partite graph                                          | 79  |

|     | for matching.                                                                                                 | 73  |

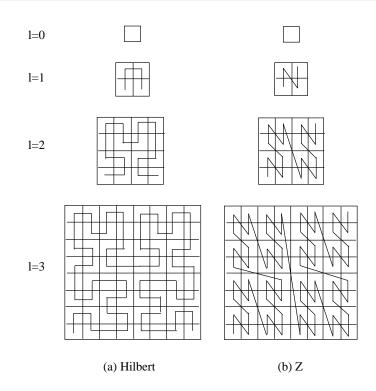

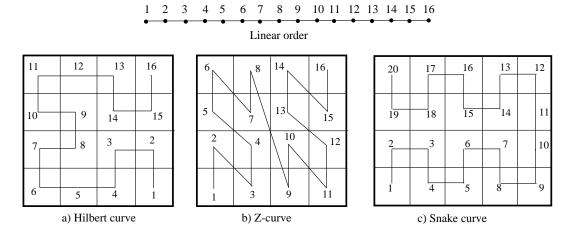

| 4.4 | Generation of space filling curves for $l = 0, 1, 2, 3, \ldots, \ldots$                                       | 75  |

| 4.5 | Placement of a one dimensional arrangement of 16 blocks on to a $4 \times 4$                                  | -   |

|     | array using space filling curves.                                                                             | 76  |

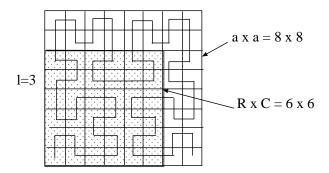

| 4.6 | Cropping the curve for $R \times C$ array within $a \times a$                                                 | 77  |

| 5.1 | A schematic indicating the role of our work                                                                   | 91  |

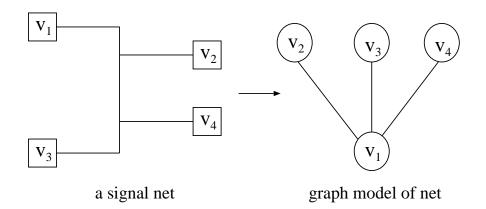

| 5.2 | A net/hyperedge and its corresponding graph; $v_1$ is the source. $\ . \ .$                                   | 92  |

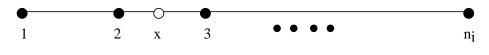

| 5.3 | Span of a net (hyperedge) with $n_i$ CLBs                                                                     | 94  |

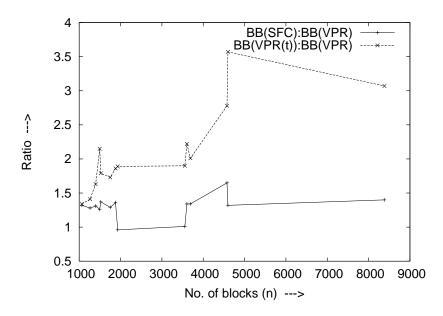

| 5.4 | Effectiveness of our proposed Algorithm 5.2: comparison of the ratios                                         |     |

|     | $\frac{HPWL(SFC)}{HPWL(VPR)}$ and $\frac{HPWL(VPR_t)}{HPWL(VPR)}$ , where t is the time taken by Algorithm    |     |

|     | 5.2, and $HPWL(VPR_t)$ is the $HPWL$ cost of the solution produced                                            |     |

|     | by VPR run only for time $t$                                                                                  | 104 |

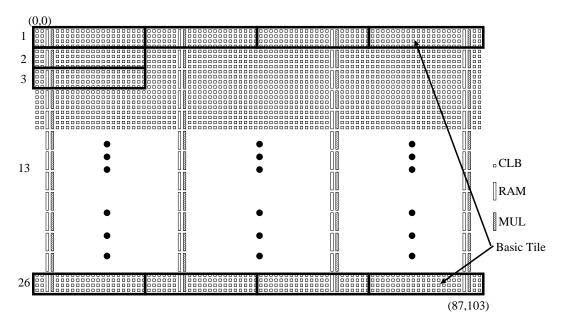

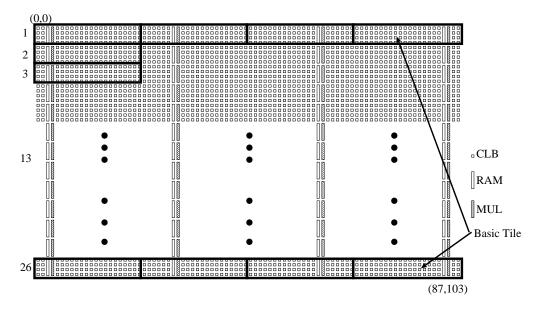

| 6.1  | Spartan-3 XC3S5000 FPGA architecture, tessellated with <i>basic tiles</i> indicated by thick-lined rectangles, each having 4 rows × 20 columns of CLBs and 1 pair of RAM-MUL blocks; $(0, 0, W, H) = (0, 0, 87, 103)$ . 109                                                                                                                                                                                                                                                                                                             |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

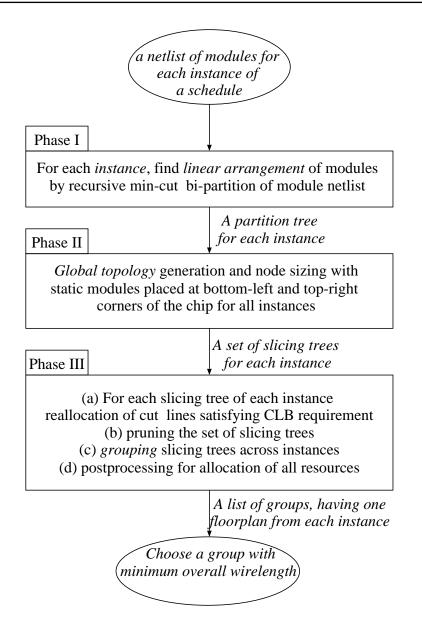

| 6.2  | Flow of our floorplanning method <i>HeteroFloorplan</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

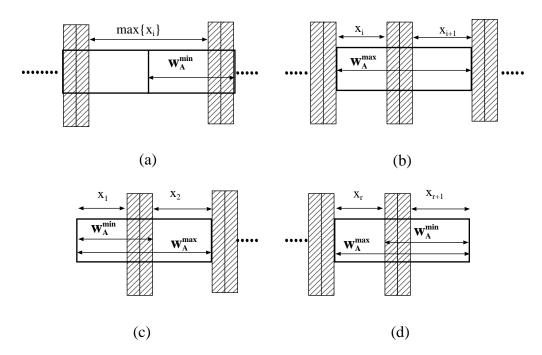

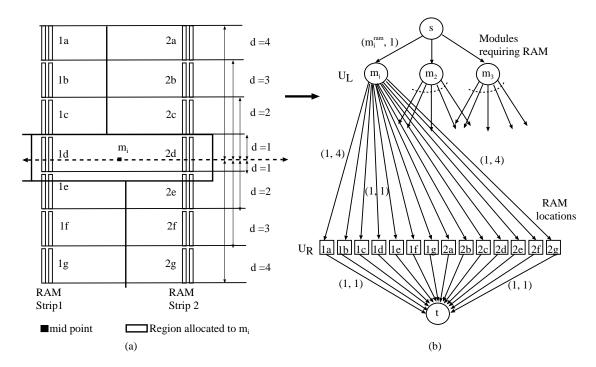

| 6.3  | The width $w_A$ of a <i>basic tile</i> : (a) lower bound, (b) upper bound, (c) for<br>the CLB columns to the left of the left-most RAM/MUL column pair,<br>(d) for the CLB columns to the right of the right-most RAM/MUL<br>column pair                                                                                                                                                                                                                                                                                                |

| 6.4  | The width $w_A$ of a <i>basic tile</i> for $\gamma > 1$ : (a) lower bound, (b) upper<br>bound, (c) for the left-most CLB columns (d) for the right-most CLB<br>columns                                                                                                                                                                                                                                                                                                                                                                  |

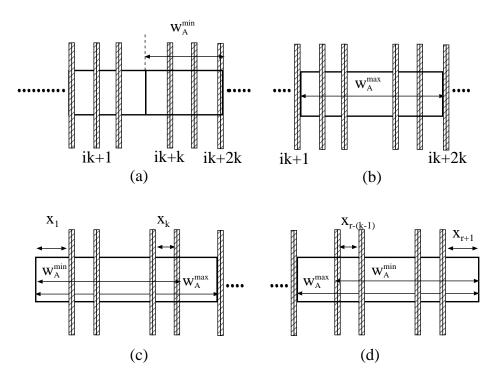

| 6.5  | Lists of shapes created at an internal node $p$ of partition tree $\mathcal{B}$ by post-order traversal. '*' and '+' represent abutment of shapes by vertical and horizontal cut respectively. '  ' denotes merging of two lists of shapes obtained by vertical and horizontal node sizing 121                                                                                                                                                                                                                                          |

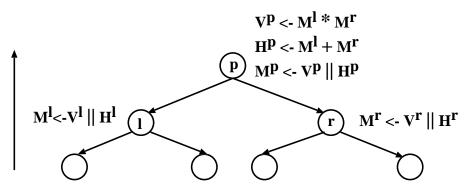

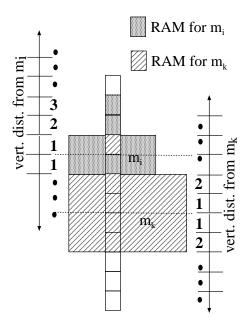

| 6.6  | Candidate RAM/MUL locations for a module $m_i$ with requirement<br>of 3 RAM blocks, but having only 2 RAM blocks within its allocated<br>rectangular region. The 7 RAM blocks within each of RAM strip<br>1 and RAM strip 2 are the candidate RAM locations; (b) portion<br>of the min-cost flow network corresponding to RAM/MUL alloca-<br>tion for module $m_i$ showing arcs to all 14 candidate RAM locations<br>$1a, \ldots 1g, 2a, \ldots, 2g$ ; the pair of numbers on each arc indicate its ca-<br>pacity and cost respectively |

| 6.7  | Example of an allocation of RAM/MUL which is not $\mathit{order-preserving}.125$                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

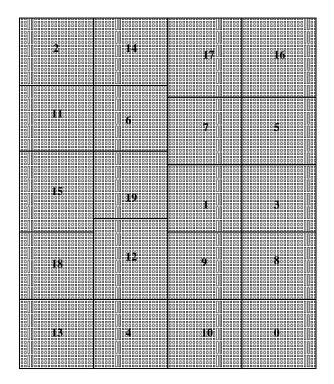

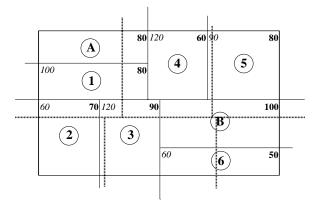

| 6.8  | An example circuit with 20 modules [Cheng 2004]: floorplan pro-<br>duced by <i>HeteroFloorplan</i>                                                                                                                                                                                                                                                                                                                                                                                                                                      |

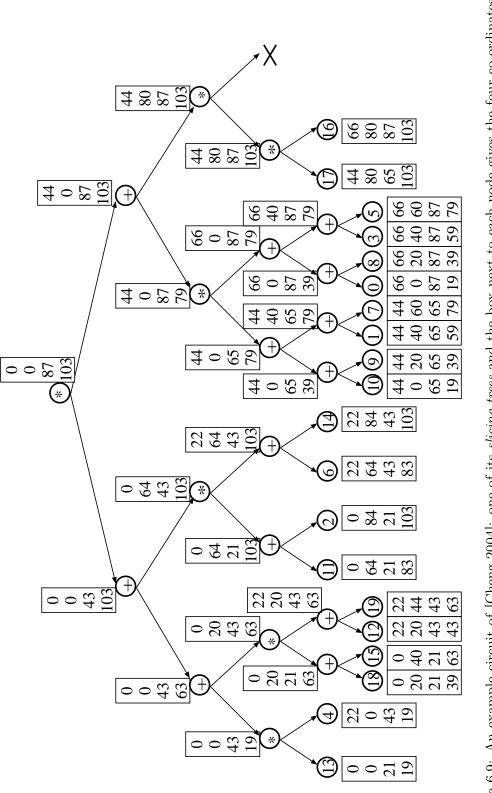

| 6.9  | An example circuit of [Cheng 2004]: one of its <i>slicing trees</i> and the box next to each node gives the four co-ordinates $(x^{min}, y^{min}, x^{max}, y^{max})$ of the region allocated to the node                                                                                                                                                                                                                                                                                                                                |

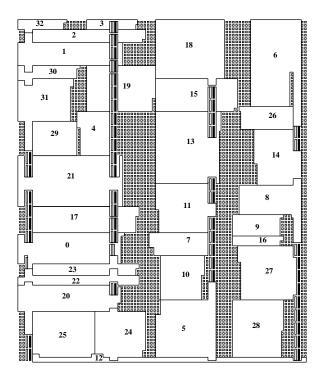

| 6.10 | Floorplan of <i>ami33</i> after phase III for $(T_w, T_h) = (4, 30)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

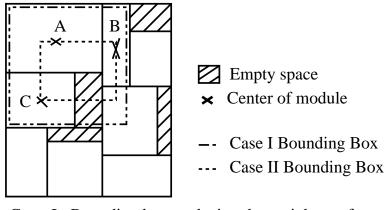

| 6.11 | Computation of bounding box of a net with terminals on modules marked $A, B$ and $C. \ldots \ldots$                                                                                                                                                                                                                                                                                                              |

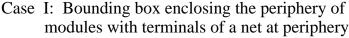

| 6.12 | Variation of HPWL (Case I) with average aspect ratio of a module 135                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

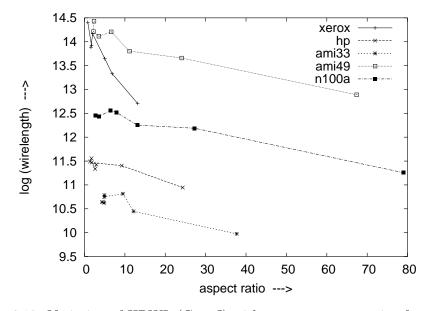

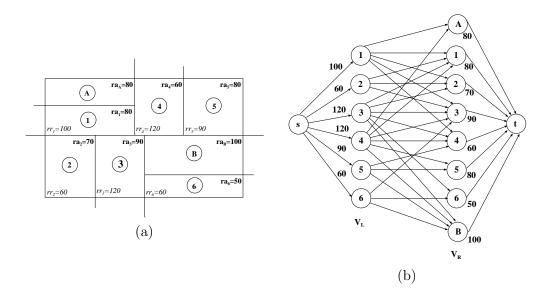

| 6.13 | (a) A linearly scaled down realization $S$ of a node-sized slicing tree<br>to fit an $(0, 0, W, H)$ architecture. Rectangles marked $1, \ldots, 6$ denote<br>the module realizations; $ra_i$ $(rr_i)$ denotes resource available (require-<br>ment). (b) Flow network corresponding to the realization shown in |        |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| 6.14 | (a)                                                                                                                                                                                                                                                                                                             | 137    |

|      | eroFloorplan                                                                                                                                                                                                                                                                                                    | 139    |

| 7.1  | Flow of the proposed method <i>PartialHeteroFP</i>                                                                                                                                                                                                                                                              | 144    |

| 7.2  | Spartan-3 XC3S5000 FPGA Architecture, tessellated with a <i>basic tile</i> , indicated by a rectangle of 4 rows and 20 columns of CLBs and 1 pair                                                                                                                                                               |        |

|      | of RAM-MUL blocks (Figure 6.1 reproduced for convenience)                                                                                                                                                                                                                                                       | 146    |

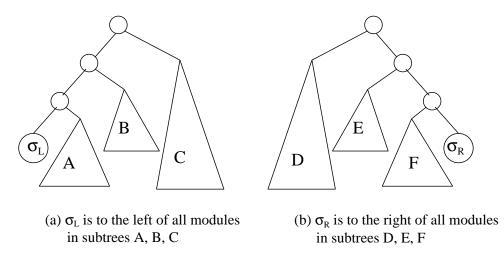

| 7.3  | Modules at the left-most and the right-most leaves go to the bottom-<br>left and top-right corner of the floorplan.                                                                                                                                                                                             | 147    |

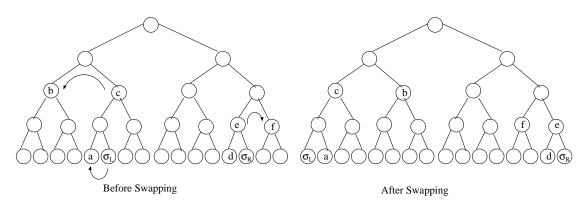

| 7.4  | Swapping of <i>static</i> super modules to extreme ends of the <i>partition</i>                                                                                                                                                                                                                                 | 1 4 17 |

|      | <i>tree</i> ; the arrow indicates the partitions to be exchanged                                                                                                                                                                                                                                                | 147    |

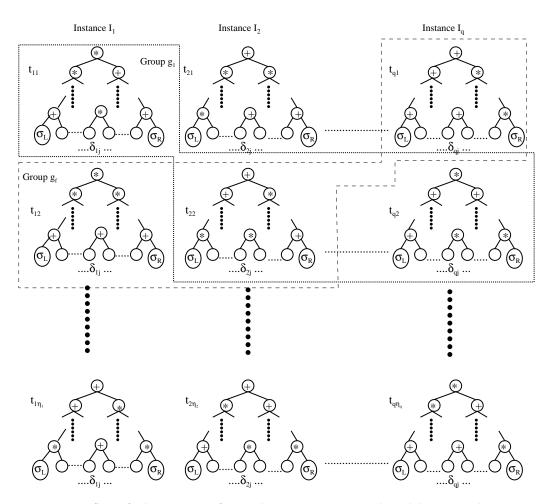

| 7.5  | 1                                                                                                                                                                                                                                                                                                               | 148    |

| 7.6  | Set of <i>slicing trees</i> for each <i>instance</i> ; vertical and horizontal cuts are denoted by $*$ and $+$ ; the dotted polygon indicated the <i>group</i> $g_1$ of                                                                                                                                         |        |

|      |                                                                                                                                                                                                                                                                                                                 | 150    |

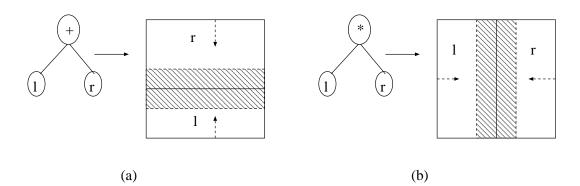

| 7.7  | The convention used for allocation of CLBs for (a) vertical cut (b)                                                                                                                                                                                                                                             |        |

|      | horizontal cut; the shaded part shows the <i>free regions</i> ; unshaded part                                                                                                                                                                                                                                   |        |

|      | represents the allocated region; '+' denotes <i>horizontal cut</i> and '*'                                                                                                                                                                                                                                      |        |

|      | denotes vertical cut.                                                                                                                                                                                                                                                                                           | 152    |

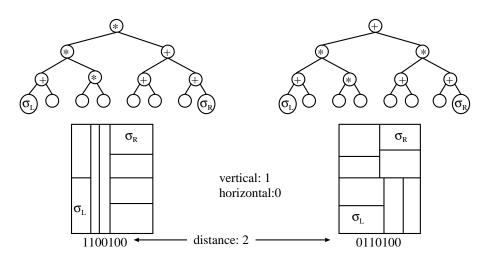

| 7.8  | Distance between two <i>slicing trees</i>                                                                                                                                                                                                                                                                       | 154    |

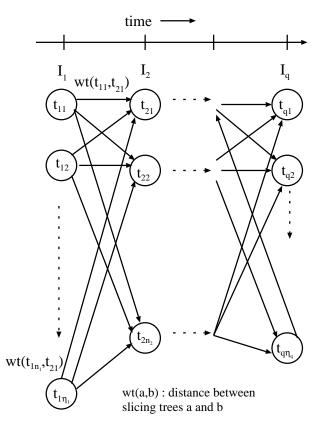

| 7.9  | Grouping of slicing trees by finding shortest path in the associated                                                                                                                                                                                                                                            |        |

|      | digraph                                                                                                                                                                                                                                                                                                         | 155    |

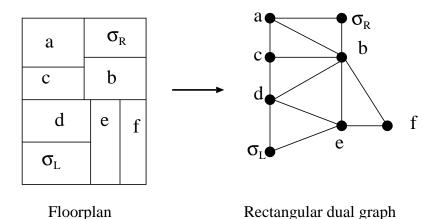

| 7.10 | Rectangular dual graph (RD) corresponding to a floor<br>plan. $\ldots$ .                                                                                                                                                                                                                                        | 157    |

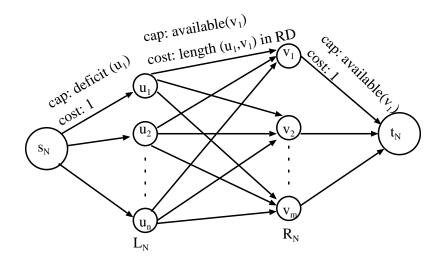

| 7.11 | Postprocessing by <i>min-cost max-flow</i> for satisfying CLB requirements.                                                                                                                                                                                                                                     | 158    |

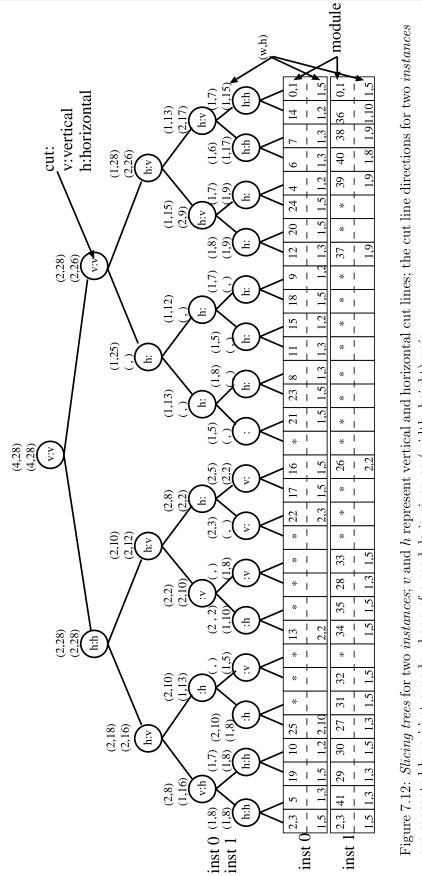

| 7.12 | Slicing trees for two instances; $v$ and $h$ represent vertical and horizon-                                                                                                                                                                                                                                    |        |

|      | tal cut lines; the cut line directions for two <i>instances</i> are separated                                                                                                                                                                                                                                   | 1.00   |

|      | by a ':' at a node; shape of a module is given as (width, height) pair.                                                                                                                                                                                                                                         | 162    |

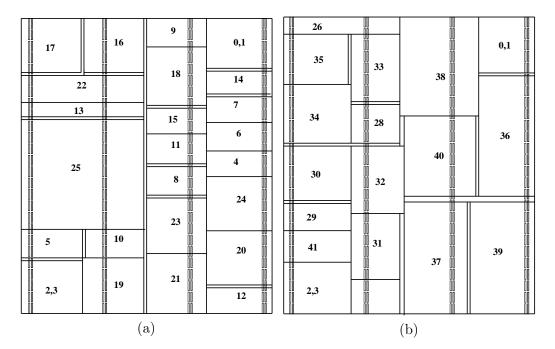

| 7.13 | Floorplan after greedy allocation of CLBs: (a) <i>instance</i> 0, (b) <i>instance</i>                                                                                                                                                                                                                           | 169    |

|      | 1                                                                                                                                                                                                                                                                                                               | 163    |

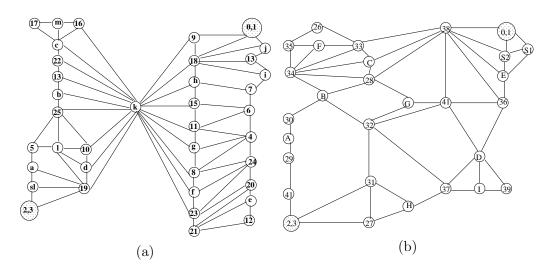

| 7.14 | Rectangular dual graph for (a) <i>instance</i> 0 (b) <i>instance</i> 1; letters repre- |     |

|------|----------------------------------------------------------------------------------------|-----|

|      | sent a rectangular region either unallocated or shared by two modules,                 |     |

|      | and numerals denote the modules with deficit in CLB requirements                       |     |

|      | within its allocated rectangular region                                                | 164 |

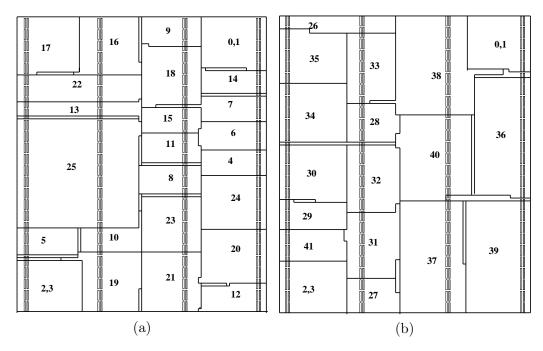

| 7.15 | Final floorplan for (a) <i>instance</i> 0, (b) <i>instance</i> 1                       | 164 |

# List of Symbols

| $\kappa$    | maximum number of shapes generated for a module                             |

|-------------|-----------------------------------------------------------------------------|

| $ ho_m$     | resource requirement vector of module $m$                                   |

| $\sigma_L$  | left super module                                                           |

| $\sigma_R$  | right super module                                                          |

| A           | basic tile                                                                  |

| $b_{ij}^c$  | number of common blocks in cones $\tau_i$ and $\tau_j$                      |

| $b_i$       | any block CLB or IOB                                                        |

| $BB_i$      | bounding box of net $i$                                                     |

| C           | Set of CLBs                                                                 |

| $c_i$       | a CLB                                                                       |

| d           | maximum number of terminals in a net                                        |

| $D^b$       | block netlist graph                                                         |

| $DM_i$      | set of dynamic modules in instance ${\cal I}_i$                             |

| $G^a$       | cone adjacency graph                                                        |

| $G^b$       | bi-partite graph for IOB placement                                          |

| $G^o$       | flow graph for reallocation of overloaded regions                           |

| $G_c$       | netlist graph for clustering                                                |

| $g_f$       | a group, consisting of one slicing tree for each instance in a task scedule |

| Η           | height of FPGA chip in terms of CLB height                                  |

| H = (       | (V, E) hypergraph representing netlist of CLBs or modules                   |

| $H_t$       | height of FPGA chip in terms of basic tile                                  |

| $I_i$       | $i^{th}$ instance of a task schedule                                        |

| k           | number of signal nets                                                       |

| $l^b_i$     | level of a block in cone $\tau_i$                                           |

| M           | set of modules                                                              |

| m           | module                                                                      |

| $m_i^{ram}$ | RAM requirement of a module                                                 |

| n           | number of CLBs or modules                                                |

|-------------|--------------------------------------------------------------------------|

| $n_i$       | number of dynamic modules in instance $I_i$                              |

| $n_{pi}$    | number of primary inputs                                                 |

| $n_{po}$    | number of primary outputs                                                |

| $O_i$       | linear arrangement of subgraph $SG_i$                                    |

| p           | number of primary input and output blocks (IOB)                          |

| $p^i$       | a primary input block                                                    |

| $p^o$       | a primary output block                                                   |

| $p_i$       | an IOB                                                                   |

| q           | number of instances in a task schedule                                   |

| $R_i$       | rectangular region assigned to a module $m_i$                            |

| S           | set of signal nets                                                       |

| $S_i$       | a signal net                                                             |

| SM          | set of static modules among $\boldsymbol{q}$ instances in a task scedule |

| $T_h$       | height of floorplan in terms of basic tile                               |

| $T_m$       | tile required by module $m$                                              |

| $T_w$       | width of floorplan in terms of basic tile                                |

| $t_{ij}$    | $j^{th}$ slicing tree of $i^{th}$ instance                               |

| W           | width of FPGA chip in terms of CLB width                                 |

| $W^c_i$     | width of cone $\tau_i$                                                   |

| $W^o_{ij}$  | width of overlap of cones $	au_i$ and $	au_j$                            |

| $w_A$       | width of basic tile                                                      |

| $W_t$       | width of FPGA chip in terms of basic tile                                |

| $w_{ij}$    | weight of edge $(v_i, v_j)$ in $G^a$                                     |

| $w_{ij}(b)$ | weight of edge $(v_i, v_j)$ due to block b in $G^a$                      |

| $\delta_i$  | a dynamic module                                                         |

| $\eta_i$    | number of slicing trees generated in instance $I_i$                      |

| $\sigma_i$  | a static module                                                          |

| $	au^i$     | input cone                                                               |

| $	au^o$     | output cone                                                              |

|             |                                                                          |

# Chapter 1

# Introduction

#### Contents

| 1.1 FPGA 1                          |                                                                |    |  |  |  |  |

|-------------------------------------|----------------------------------------------------------------|----|--|--|--|--|

| 1.2 Components of a basic FPGA chip |                                                                |    |  |  |  |  |

| 1.3 Types of FPGA 5                 |                                                                |    |  |  |  |  |

| 1.3.1                               | Structural classification                                      | 6  |  |  |  |  |

| 1.3.2                               | Programming technology based classification                    | 7  |  |  |  |  |

| 1.3.3                               | Modern FPGAs                                                   | 8  |  |  |  |  |

| 1.4 Design flow for FPGA            |                                                                |    |  |  |  |  |

| 1.5 Scope of the thesis 12          |                                                                |    |  |  |  |  |

| 1.5.1                               | Placement of CLBs on island-style homogeneous FPGAs            | 13 |  |  |  |  |

| 1.5.2                               | Floorplanning for heterogeneous FPGAs                          | 15 |  |  |  |  |

| 1.5.3                               | Floorplanning for partial reconfiguration in heterogeneous FP- |    |  |  |  |  |

|                                     | GAs                                                            | 17 |  |  |  |  |

| 1.6 Organization                    |                                                                |    |  |  |  |  |

## 1.1 FPGA

Field-programmable gate-arrays (FPGA) are programmable hardware platforms with pre-fabricated logic and interconnects, which are electrically programmed by the user to realize a variety of circuits frequently required in a wide range of applications. Unlike application-specific integrated-circuits (ASICs), where realization of a circuit design takes several man-hours and enormous effort, the pre-fabricated logic and interconnects can be quickly programmed according to the design specification and made functional. Thus, in contrast to the ASICs, FPGAs can be customized and reconfigured depending on the need of the user. A basic FPGA chip consists of a set of configurable logic blocks (CLB) and interconnects which can be connected by means of transistor switches or anti-fuses. Each CLB consists of small memory units in the form of *lookup tables* (LUT) which can be programmed at run-time. To realize a circuit on to FPGA, these LUTs need to be loaded with appropriate functionality in terms of bits at run-time. Given a circuit design, it undergoes several optimization steps [Betz 1999] to get realized on to the FPGA chip. Finally, a *bitstream* of the design is generated that is downloaded on to the FPGA chip. This process of realizing a circuit on to the FPGA chip is called *mapping*. Once the bitstream is loaded on to the chip, the circuit starts functioning. To realize a different circuit on the same chip, one has to download only the corresponding bitstream on to the FPGA chip. Being reconfigurable, the turn-around time for the application is significantly less than realizing an application on ASIC.

FPGAs have experienced an exponential growth in the past twenty years and are increasingly competing with ASICs in medium to low volume market [Wang 2003]. FPGAs were introduced in mid to late eighties with merely 64 *lookup tables* (LUTs) as simple glue logic, whereas modern FPGAs offer up to over two billion *programmable logic cells* along with a large number of macro blocks such as memory, DSP blocks, embedded processors, high speed Input/Outputs and many other pre-placed blocks [Kuon 2007]. The reason for the success of FPGAs is their low *non-recurring engineering* (NRE) costs and reconfigurability. Because of reconfigurability and fast turn-around time, FPGAs are not only used in ASIC prototyping as in earlier days, but also in mission critical applications. Now with millions of logic gates in an FPGA, with shorter design and production time, lower setup cost and risk, it is extensively used in space applications, *digital signal processing* (DSP), software defined radio, aerospace, defense, medical imaging, speech recognition and bio-informatics [Xilinx, Brown 1995, Manimegalai 2007].

In order to take the full advantage of FPGA's reconfigurability, the *mapping* time of a given design on to FPGA chip has to be minimized. The process of mapping is a complex task, involving conflicting objectives to be satisfied during the process. As in ASICs, the mapping of a design on to the FPGA consists of the following design steps: *synthesis*, *technology mapping*, *floorplanning* and *place-and-route*. The problems to be solved for almost all the steps are difficult in nature, and belong to the class of NP-hard problems [Sherwani 1993]. Thus, it is not possible to design polynomial time algorithms to solve the problems optimally. The *computer-aideddesign* (CAD) tools play a critical role in obtaining solutions of *high quality* with *efficiency*. Although these design steps seem to be similar to those for the traditional ASIC design, each step of FPGA design has additional constraints and optimization criteria to be satisfied [Wang 2003, Taghavi 2004].

This thesis focuses on the floorplanning and placement step of the FPGA CAD

flow. The research in this area aims at either obtaining a very high quality solution for the *physical design problem*, or getting the solution quicker with minimal sacrifice in quality of solution. The objective of this thesis is to develop fast yet efficient placement and floorplanning technique for mapping a given design on to FPGA with minimal sacrifice in the quality of solution in the context of run-time reconfiguration in FPGAs. In this chapter, the basic architecture of FPGAs is presented in Section 1.2 followed by different categories of FPGA architectures in Section 1.3. Section 1.4 discusses the FPGA physical design cycle. The scope of the proposed work is presented in Section 1.5. Finally, the chapter concludes with the organization of the thesis in Section 1.6.

### 1.2 Components of a basic FPGA chip

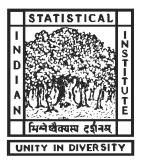

The basic component of any FPGA chip is a set of *programmable* or *configurable* logic blocks (CLB) arranged in a two dimensional array with routing wires laid out in *horizontal* and *vertical channels* between rows and columns of CLBs respectively. A CLB (also called *logic blocks* in general) consists of *lookup tables* (LUT), flip flops (FF) and/or multiplexers for implementation of logic. Figure 1.1 shows a simple earlier generation FPGA architecture which is a widely accepted architecture model used in the FPGA research community [Betz 1999, Emmert 1999b, Chang 2000, Vicente 2004, Maidee 2005, Vorwerk 2009]. The input/output blocks (IOB) are located around the periphery of the chip, providing programmable I/Oconnections and support for various I/O standards [Anderson 2000]. Each CLB is surrounded by routing channels connected through switch blocks and connection blocks. The wires in the channel are segmented, and are of varying length. Commercial FPGA chips have many dedicated interconnects of different lengths which are point-to-point and unidirectional. A switch block connects wires in adjacent channels through programmable switches such as pass-transistors or bi-directional buffers, and is represented as a matrix of possible connections. A connection block connects the wire segments in a channel to the input and output pins of a CLB using *programmable switches*. All the programmable switches are identical. While programming, the appropriate switches are turned on or off. Figure 1.1 shows the internal configuration of a part of an FPGA chip.

The routing architecture of an FPGA is defined by channel width  $W_c$ , switch block flexibility  $F_s$ , connection block flexibility  $F_c$  and segmented wire length. The channel width defines the number of wires laid out and pre-fabricated in the channel of an FPGA chip. The switch block flexibility is the number of wires in each channel

Figure 1.1: Basic FPGA architecture.

to which each incoming wire can connect in a switch block. The *connection block flexibility* is the number of wires in each channel to which a logic block input or output pin can connect. The *segmented wire length* is the number of logic blocks a wire segment spans. As the wires cross different number of logic blocks in segmented wire architecture, the FPGA interconnect delays become highly non-linear, discrete, and in some cases, even non-monotone with respect to the distance. If there is a connection between two CLBs whose distance is 3 CLB units, and there are two options of connecting them; (i) using two wires spanning 1 CLB each, or (ii) one wire spanning 3 CLBs, the second option incurs less delay and hence leads to better performance than the first one. Finally, an H-tree based clock network [Sherwani 1993] is laid on to the chip for feeding the *flip flops* in LUTs.

Each logic block or CLB usually contains a group of basic logic elements (BLE). In an LUT based FPGA architecture, typically each BLE contains a K-input lookup table and a register. The output of K-LUT [Brown 1995, Kuon 2007] can be registered by connecting it to a flip flop, or it can remain unregistered. Commercial FPGAs, for example, Altera's Stratix II FPGA use an *adaptive logic module* (ALM) which contains a group of LUTs and a pair of flip flops [Altera]. The ALM can expand and share the LUT inputs and has more logic capacity than traditional 4-input LUT structures for an equivalent function. An ALM is similar to a 7-input LUT

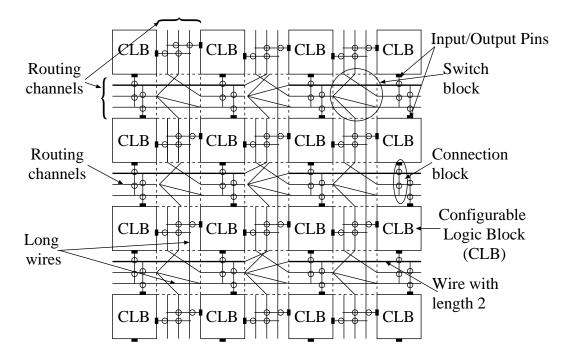

Figure 1.2: Types of FPGA architecture.

that can be flexibly re-partitioned into a number of configurations such as either a 5-input LUT and a 3-input LUT, or two 4-input LUTs. With input sharing, larger combinations can be created, such as two 5-input LUTs or even two 6-input LUTs. The larger logic capacity in Stratix II ALMs improves the overall performance of the design by packing more logic in an ALM.

### 1.3 Types of FPGA

FPGAs are used in different types of applications and the resource requirements are also diverse. FPGAs were first developed by Xilinx in mid 80's [Xilinx]. Later on, many companies such as Altera [Altera], Lattice Semiconductor [Lattice], Actel [Actel], SiliconBlue Technologies [SiliconBlue], Achronix [Achronix], Quicklogic [QuickLogic] developed their own FPGAs of different structures. FPGAs can either be classified by the structure and organization of the logic and routing resources, called *structural classification*, or by the programming technologies used to configure it, called *programming technology based classification*.

#### **1.3.1** Structural classification

FPGAs can be categorized into four classes depending on the arrangement of its logic and routing resources as shown in Figure 1.2. These are:

#### 1.3.1.1 Sea-of-gates architecture

Logic blocks are arranged in a two dimensional array, and interconnects are overlaid on top of the logic blocks as shown in Figure 1.2(a). The *logic block* is generally composed of a multiplexer which feeds a NAND gate or some other functional unit, and a *latch*. Logic blocks are connected to routing resources through multiplexers, and a Static RAM (SRAM) cell controls the multiplexer.

#### 1.3.1.2 Hierarchical PLD architecture

Figure 1.2(b) shows the hierarchical *programmable logic device* (PLD) architecture. The logic blocks or PLD blocks and programmable interconnects are arranged in a hierarchy. Each PLD block contains logic modules with programmable combinational and sequential elements. The logic modules are programmed using the bits stored in configuration memory. Altera FPGAs [Altera ] belong to this category of FPGAs.

#### 1.3.1.3 Symmetrical or island-style architecture

This type of FPGAs is shown in Figure 1.2(c). The CLBs are arranged uniformly in rows and columns as explained in Section 1.2, with wires laid out in the horizontal and vertical channels between rows and columns of CLBs respectively. The IOBs are located on the periphery of the two dimensional array. Each CLB contains one or more K-input LUTs and flip flops. The routing is done through the wires laid out in the channel and the switching blocks present at every junction of horizontal and vertical channel by appropriate programming of the switch blocks. Xilinx, Achronix, SiliconBlue and QuickLogic FPGAs provide this type of FPGA architecture.

#### 1.3.1.4 Row based architecture

Row based architecture has the logic modules and programmable interconnects arranged in alternate rows, as shown in Figure 1.2(d) in one layer. The vertical interconnects, laid out on top of it in a separate layer are used to connect modules in different rows. The IOBs are located on the periphery surrounding the logic modules. Actel Corporation provide this type of FPGAs.

| Company    | General          | Type of     | Programming |

|------------|------------------|-------------|-------------|

|            | Architecture     | logic block | Technology  |

| Xilinx     | Island-style     | LUT-based   | static RAM  |

| Altera     | Hierarchical PLD | PLD block   | EEPROM      |

| Actel      | Row based        | MUX based   | Anti-fuse   |

| Quicklogic | Island-style     | MUX based   | Anti-fuse   |

Table 1.1: Summary of FPGA architectures provided by different companies

In summary, most of the commercial FPGAs belong to the category of islandstyle FPGAs and are used widely in the FPGA research community. Thus, islandstyle FPGA architecture is assumed for the proposed methods in this thesis. However, the CAD tools developed for one type of FPGA architecture can be adapted to other architectures by adding constraints relating to the location of the logic blocks pertaining to that architecture.

#### 1.3.2 Programming technology based classification

FPGAs can be classified into three groups depending on the programming technologies used to configure the FPGAs [Brown 1995, Kuon 2007].

Anti-fuse programming technology: FPGAs using this technology are one time programmable as *anti-fuses* make permanent connections between logic blocks. Programming is done by blowing the anti-fuse. A high voltage breaks down the metal-to-metal anti-fuse and causes the fuse to conduct [Kuon 2007]. It provides a low resistance, bidirectional connection between segments. This technology is used in Actel and QuickLogic FPGAs.

Static RAM (SRAM) programming technology: Programmable connections are realized using pass gates or multiplexers. SRAM cell controls the pass gates and multiplexers. Since SRAM is volatile, the FPGA needs to be reconfigured each time the power is applied to the chip. Xilinx, Lattice Semiconductor, Altera FPGAs mostly use SRAM programming technology.

**EEPROM programming technology:** It uses EEPROM (*electrically erasable programmable read-only memory*) memories and it helps reprogramming of device by erasing and rewriting into the configuration memory several times. Unlike SRAM technology, it does not require external memory storage to program it at power up. Altera FPGAs also use this technology for programming.

Of these approaches, *static memory* and *anti-fuse* technologies are widely used in modern FPGAs. Although SRAM based cells occupy large areas, it is widely

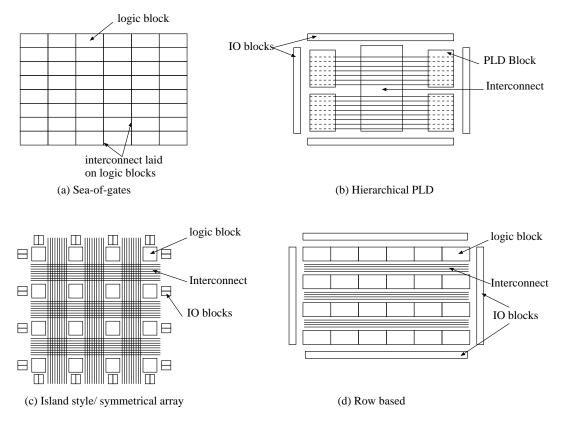

Figure 1.3: Modern FPGA architecture with Block RAM and Multipliers.

used for its re-programmability features. Moreover, an FPGA can even be partially reconfigured, while a portion of it is still executing some operations using the SRAM technology. Most of the symmetrical array based FPGA architectures use SRAM programming technology, and row based structures use anti-fuse technology. Table 1.1 shows a summary of the existing major architectures adopted by the leading FPGA fabrication companies [Xilinx , Altera , Actel , QuickLogic ].

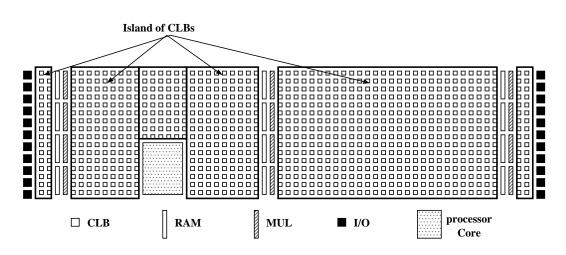

#### 1.3.3 Modern FPGAs

The basic FPGA consisted of only the CLBs and IOBs in the beginning. These are termed as FPGAs with *homogeneous* resources. Unlike earlier generation FPGAs, modern FPGAs such as Xilinx's Spartan and Virtex Series [Xilinx], Altera's Stratix series [Altera] consist of not only the CLBs, but also block RAMs (BRAM), Multipliers (MUL), DSP cores, and even small microprocessors on the FPGA chip to support *System-on-Chip* (SoC) designs. One such configuration with CLBs, RAMs, multipliers (MULs) and processor core is shown in Figure 1.3.

The first type of *heterogeneous* resources in FPGAs was BRAM which first appeared commercially in the Altera Flex 10K series FPGA [Ngai 1995, Altera 2003, Kuon 2007]. This memory block consisted of 2Kb of static RAM, which could be configured as either a  $2048 \times 1$ , or  $1024 \times 2$ , or  $512 \times 4$  or  $256 \times 8$  bit memory. FPGAs in the Xilinx Virtex-4 series onwards have block RAMs of 18Kb [Xilinx ]. Xilinx Virtex II FPGA [Xilinx 2005] first introduced the multiplier (MUL) integrated into the chip. This series of FPGAs contained  $18 \times 18$  multiplier that sat along a block memory. Since the introduction of Virtex II, Xilinx and other manufacturers have introduced more sophisticated hard computational units that include

multiplier-accumulators, and some multiplexer functions [Kuon 2007]. The Stratix I [Kuon 2007] of Altera contains a single  $36 \times 36$  multiplier-accumulator block that can be broken into eight  $9 \times 9$  multipliers and an adder to sum results. Before long, Altera introduced *Excalibur*, an FPGA which included a hard processor core from ARM Inc. [ARM], connected to an Altera Apex 20K series FPGA [Kuon 2007]. Almost at the same time, Xilinx introduced Virtex II Pro FPGAs which included one, two, or four IBM Power PC microprocessor cores [IBM] integrated with a Virtex II logic fabric [Xilinx 2005]. Several Xilinx Virtex-4 and Virtex-5 subfamilies also support Power PC cores [Kuon 2007].

The most popular Xilinx Spartan series has about 478K gates, 35K FFs, which can operate at 300MHz. These FPGAs are built on 90nm technology, while Virtex series FPGAs use 65nm technology having up to 2.2 million gates, 153K FFs, operating at 550MHz [Xilinx]. Altera's Stratix series has up to 7.7 million gates, 430KFFs in its logic cells, and uses *adaptive logic module* (ALM) technology [Altera]. This chip can operate at 600MHz and it is made in 65nm technology. Lattice Semiconductor uses SRAM technology having FPGAs with 1.7 million gates operating at 550MHz. Actel produces FPGAs with 752K gates operating at 350MHz. These FP-GAs use anti-fuse technology for programming and are built on 130nm technology. SiliconBlue Technologies and Achronix FPGAs are used for smaller applications. SiliconBlue Technologies provides low power FPGAs with 17K gates, operating at 32MHz fabricated in 65nm technology. Achronix FPGAs are RAM based and power efficient for being asynchronous.

Almost all of the modern FPGA architectures have CLBs, Block RAMs (BRAM) and Multipliers (MUL) embedded in the FPGA chip. Thus, the Xilinx Spartan like architecture is assumed for the efficient floorplanning methods presented in this thesis. However, the proposed methods can be suitably adapted for other architectures by adding appropriate location constraints for each additional resource on a modern FPGA chip.

## 1.4 Design flow for FPGA

In order to obtain high performance circuit on an FPGA, highly efficient CAD tools are required in each step of the FPGA design flow. Figure 1.4 depicts the typical CAD flow for modern FPGAs. A circuit to be mapped on to an FPGA, is first written in any of the hardware description languages such as VHDL/ Verilog. This description is then *synthesized* and *technology mapped* to the target FPGA architecture depending on the number of inputs and outputs available in the LUT of CLBs. Next, this technology-mapped netlist of CLBs are placed to physical locations on the target chip optimizing certain objective functions such as minimization of wirelength, delay and power. In recent times, due to large design size, increased complexity and partial reconfigurability in FPGAs, circuits are partitioned into modules and the technology-mapped netlist of modules are floorplanned before placement of individual CLBs in a module. The placement is then routed by determining the exact pre-fabricated wire segments to be used for inter-connecting the terminals of the placed CLBs. This defines the programming of the appropriate programmable interconnects on chip, and is stored as a bitstream. Finally, the bitstream of the placed and routed circuit is downloaded on to the FPGA chip through a hardware interface such as a dedicated serial or parallel port of a PC, for execution. A more detailed discussion on each of this step follows [Chen 2006]:

**Design entry:** Typically, the digital design is represented at *register transfer level* (RTL) describing the transfer of signals between registers and the logical operations performed on these signals during transfers. This RTL design is then described using various hardware description languages such as VHDL [IEEE 1987] / Verilog [Verilog International 1993]. The design constraints such as expected operating frequency, delay bounds of signal path delays (i) from input pads to output pads (I/O delay), (ii) from input pads to registers, and (iii) from registers to output pads are specified as input. The design constraints also include physical location constraints specifying the position of certain type of logic in a particular place. The target FPGA device to which the given design is to be mapped, is next selected from the set of available architectures depending on the size and resource requirements of the design.

**Synthesis:** For a design, different *datapath* operations such as additions, multiplications, register files, memory blocks, control logic etc, are identified from the given Register-Transfer-Level (RTL) design. Next, architecture independent optimizations such as *datapath optimization* and *control logic optimization* is performed.

**Technology mapping:** After synthesis and architecture independent optimization, the technology mapping step maps the optimized datapath and control logic to dedicated circuit structures such as multipliers, embedded memory blocks and CLBs available on the FPGA chip. This generates a *netlist* of CLBs, IOBs and other resources to be assigned to the target FPGA chip. The *netlist of CLBs* defines a set of *signal nets*, where each *signal net* connects a set of CLBs or IOBs.

**Floorplan:** With increasing complexity of modern FPGAs and design size, physical mapping of a flattened *technology mapped netlist* of CLBs and IOBs on to a chip has become more complex, and is likely to be counter-productive for obtaining

Figure 1.4: CAD flow for FPGAs; the rectangle with dashed lines shows the scope of this thesis.

high performance. In order to overcome these issues, a given design is partitioned into modules and then mapped on to a target architecture. Each module in the technology mapped *netlist of modules* requires a number of different logic resources available on the chip. A floorplanning step has become essential for modern FPGAs to allocate required logic resources to each of the module. The floorplanning problem for FPGAs with pre-placed heterogeneous resources and fixed-die size is the problem of allocating logic resources to each module, such that there is no overlap of modules while the optimization criteria such as total wirelength and area of the floorplan are minimized. One of the main focus of this thesis is this floorplanning step of physical design cycle for heterogeneous FPGAs.

**Placement:** After the technology mapping step, a netlist of *logic blocks* is obtained. The CLBs are then assigned to specific locations on the target chip such that certain objective criteria such as minimization of wirelength and *critical path delay*, are achieved. In order to obtain high performance circuit, the delay due to interconnection has to be minimized. This requires the connected CLBs and IOBs to sit as close as possible to each other. The exact delay of a connection can not be computed until and unless the path of the connection is routed through the channels and switch boxes on a particular FPGA chip. For large designs, this step is preceded by floorplanning of the modules, and then the netlist of CLBs within each module

are placed.